1

Изобретение относится к технике передачи дискретных сообщений.

Известно устройство синхронизации по циклам в дискретном канале связи, содержащее делитель частоты, выходы ячеек которого подключены к входам формирователя синхросигналов, и дешифратор маркерных групп, выход которого подключен через элементы И к соответствующим накопителям 1.

Однако известное устройство имеет большое время вхождения в синхронизм.

С целью сокращения времени вхождения в синхронизм в предлагаемом устройстве синхронизации по циклам в дискретном канале связи выходы каждой ячейки делителя подключены к вторым входам соответствующих элементов И через введенные формирователи стробов, причем выходы накопителей подключены к дополнительным входам формирователя синхросигналов через введенные блоки выделения максимума.

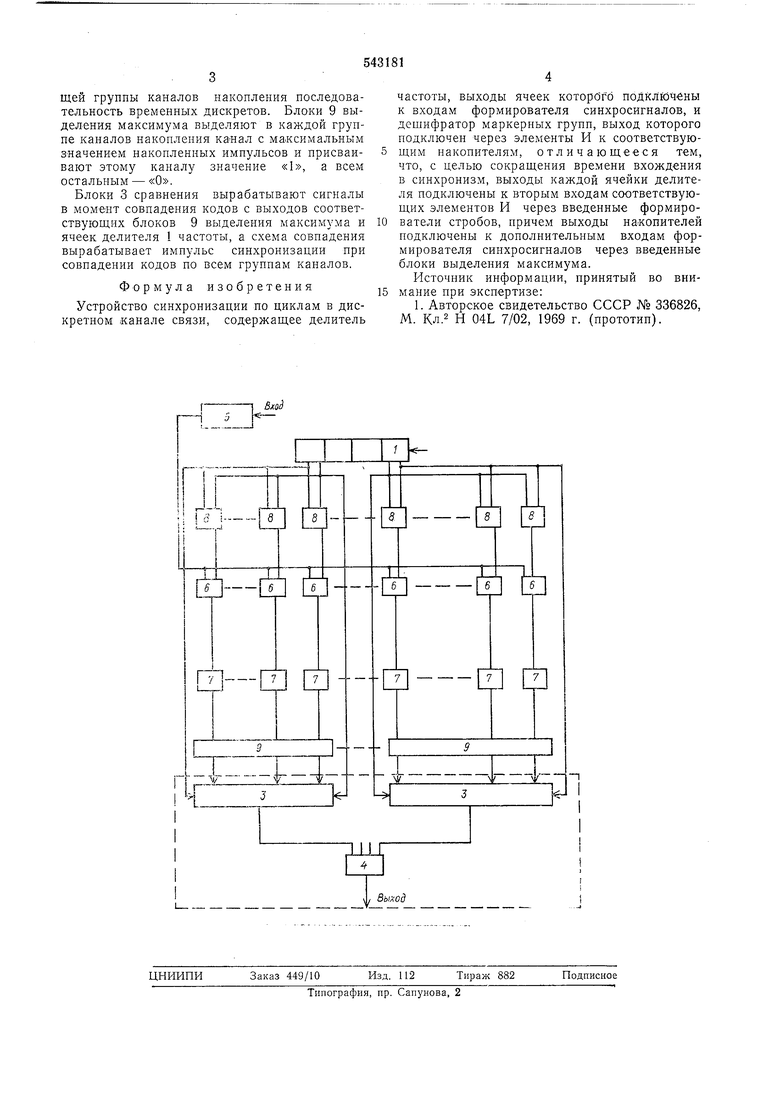

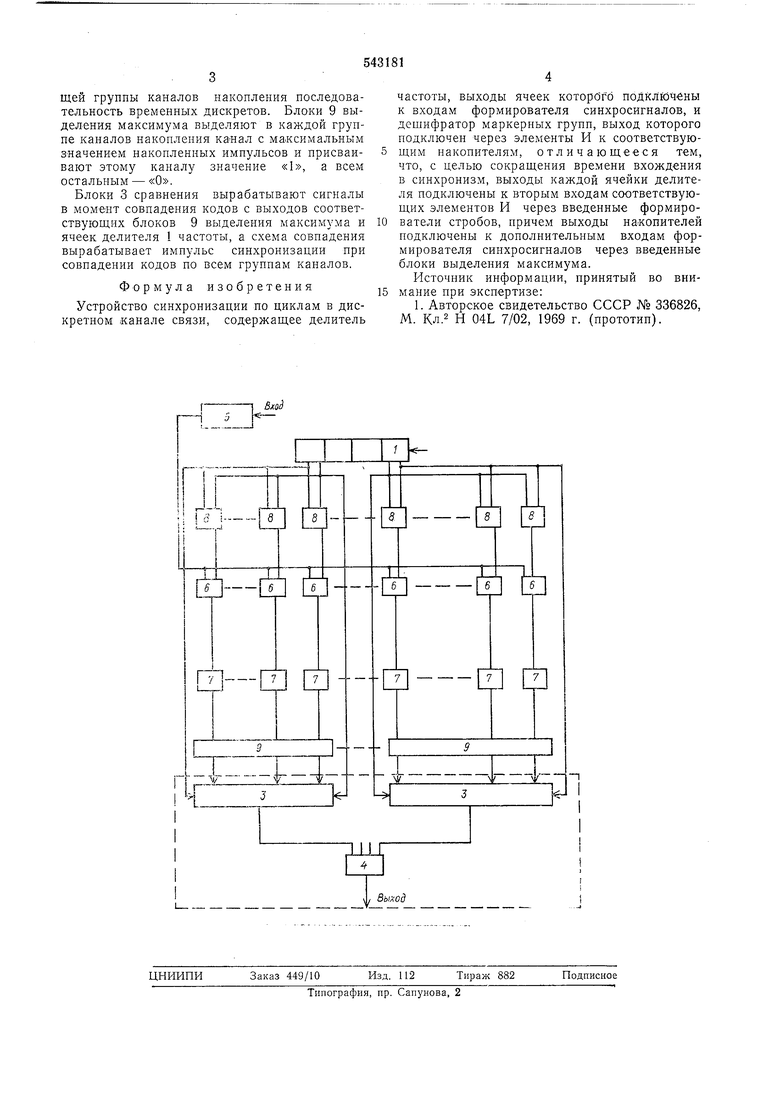

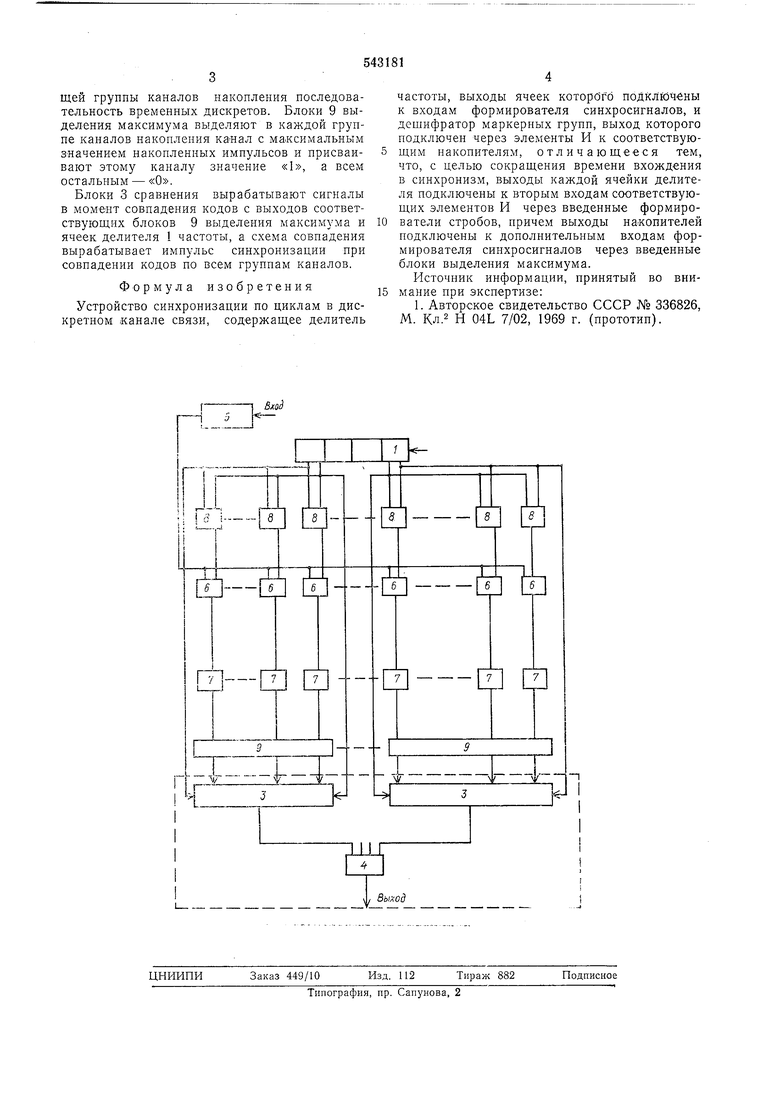

На чертеже приведена функциональная CXQма устройства.

Устройство синхронизации по циклам в дискретном канале связи содержит делитель 1 частоты, выходы ячеек которого подключены к входам формирователя 2 синхросигналов, состоящего из блоков 3 сравнения и схемы 4 совпадения, дешифратор 5 маркерных групп, выход которого подключен через элементы И 6

к соответствующим «акопителям 7, причем выходы каждой ячейки делителя 1 частоты подключены к вторым входам соответствующих элементов И 6 через введенные формирователи 8 стробов, а выходы накопителей 7 подключены к дополнительным входам формирователя 2 синхросигналов через блоки 9 выделения максимума. Устройство работает следующим образом.

Дешифратор 5 маркерных групп опознает маркерную группу в информационном разряде.

Делитель 1 частоты, формирователи 8 стробов, элементы И 6, накопители 7 и блоки 9

выделения максимума образуют анализирующий узел, который опознает после накопления в течение заданного числа циклов, связанного с требуемой помехоустойчивостью, номера каналов по каждой из m групп, соответствующие позиции цикла, в которой с наибольшей вероятностью присутствуют импульсы с дешифратора маркерных групп 5.

Каждая ячейка делителя частоты 1, содержащего п ячеек, делит поступающую «а ее

вход последовательность импульсов на

п , где .V - число участков разбиения

периода цикловой синхронизации. Формирователи 8 стробов образуют для соотвествуюЩей группы каналов накопления последовательность временных дискретов. Блоки 9 выделения максимума выделяют в каждой группе каналов накопления канал с максимальным значением накопленных импульсов и присваивают этому каналу значение «1, а всем остальным - «О.

Блоки 3 сравнения вырабатывают сигналы в момент совпадения кодов с выходов соответствующих блоков 9 выделения максимума и ячеек делителя 1 частоты, а схема совпадения вырабатывает импульс синхронизации при совпадении кодов по всем группам каналов.

Формула изобретения

Устройство синхронизации по циклам в дискретном канале связи, содержащее делитель

частоты, выходы ячеек которого подключены к входам формирователя синхросигналов, и дешифратор маркерных групп, выход которого подключен через элементы И к соответствующим накопителям, отличающееся тем, что, с целью сокращения времени вхождения в синхронизм, выходы каждой ячейки делителя подключены к вторым входам соответствующих элементов И через введенные формирователи стробов, причем выходы накопителей подключены к дополнительным входам формирователя синхросигналов через введенные блоки выделения максимума.

Источник информации, принятый во внимание при экспертизе:

1. Авторское свидетельство СССР № 336826, М. Кл.2 Н 04L 7/02, 1969 г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой синхронизации | 1977 |

|

SU621113A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1990 |

|

RU2022485C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ по ЦИКЛАМ в КАНАЛЕ АДРЕСНОЙ СИСТЕМЫ СВЯЗИ | 1972 |

|

SU336826A1 |

| Устройство для формирования синхросигналов радиоретрансляционной станции | 1972 |

|

SU449454A1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Динамическое запоминающее устройство и формирователь синхросигналов для него | 1980 |

|

SU936030A1 |

Выход

Авторы

Даты

1977-01-15—Публикация

1975-06-27—Подача