Устройство относится к теХЯИке передачи .рет;1ы. сообн1ений в усло.виях интепсивпых импульсных помех. Применение устройства особенно целесообразно при передаче дискретных сооби1еиий в асинхрО11но-адресиых системах связи с частот 1о-време}шой .матрицей (А.А.СС с ЧВМ), где при иснользогвании способов, осно:ван1ных иа передаче дешифрируемой на приеме синхрогруппы (маркерной грунты), обычно довольно велика вероятиость сбоя нри дешифра|Ц.ии.

Известные устройства синхронизации по циклам в канале адресной системы связи содержат дешифратор маркерных групн, делитель, схемы совгнадения, н.реО:бразователи-наканители «код-аиалог и сравнения.

Цель изобретения - упрощение устройства при сохранении надежности в работе.

Указанная цель достигается тем, чго парафазные выходы де.тителя Надключены ко входам преобразователей-накопителей, выходы которых соединены со входами бло.ков сравнения. При этом -каждой ячейке делите.ли соответствует одип блок сравнения, а выходы блоков иодключены ко в.ходам формирователя син.хросиг} ала, нриче.м ко входу каждой из тюследовательно соединенных схем совпадения фор.мирователя си-нхросигнала подключен выход соответствующей ячейки делителя, а другие вход|)1 схем совпадения нодк.почены к

выходам триггеров заиом иания формирователя синхросигнала.

Сформированный таким образо м двоичны сигнал нОМера лозиции, на которую чаще всего поступают импульсы с выхода дешифрато)а маркерных груоп и которая с наибольше вероятностью соответствует началу цикла, запоминается в триггерах за.помина.ння, число которых соответствует чис«ту разрядов, необходимых для двОИчной записи числа позиций цикла. Фазу делителя-распределителя устанавливают нри НОраЗряднюм совпадении указаииого номера с номером комбинации, набранной на триггерах дел.ителя-раснределителя.

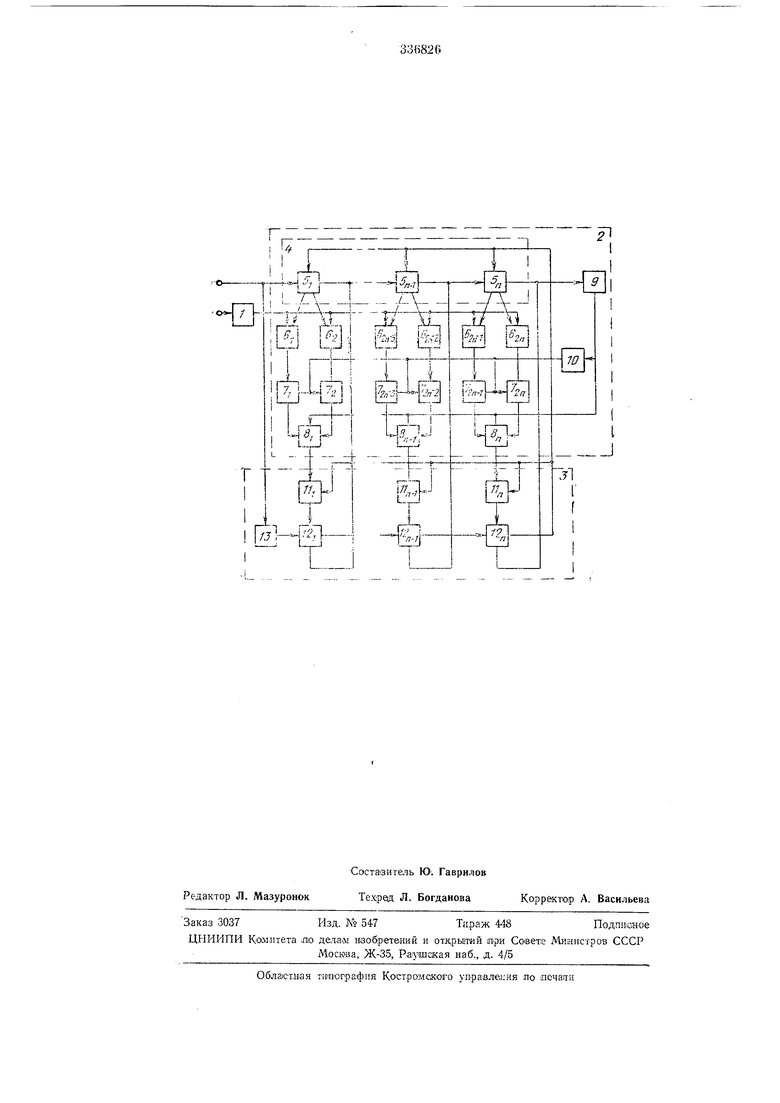

Блок-схема устройства ;приведена на чертеже.

Устройство состоит из дешифратора .маркерной груииы /, опозПающего .маркерную группу в информационном сигнале и .ири дешифрации грун.ны, соответствующей маркерной грулпе формирующего сигнала, отмечаюHiero преднолагаемлю позицию иачала цнкла; из анализируюи1,его узла (узла шюзнанателя на.мера маркерной лознции) 2, онознаюннго, по истечении заданного чис.ча цнк.10, которое однозначно связано с требуемой иомехоустойчнвостью, номера позиции цикла, на которую чаще всего поступали импульсы с дешифр.атора маркерной грунны } н которая с нанГ)У.1ьшс1 | короят.ио.счыо co.oiiKie пвует яача-лу ц.пкла, II ;узла (Ьор.мн роваПци сшгхро.спгнала 3, (boj)Miipyioinero спгиал, уст..тИваюЩИЙ фазу пр.исмиого .расафеделителя ;; соответствии с номером, указанным лз.юм опозяазателя iK.iepa мархертюй позиции 1.

Узел отюЗиава-теля номе|.)а Л1ар:;е)1оГ1 пози.ИИи 2 состоит из делителя-раса1р:еде1;штеля 4, представляющего собой лпиешсу двоичных элементов 5i-5„ (где /; - число разрядой, необходимых для записи ,ч двоично кйа числа .позиций в цикле), работающих в режиме деления та-ктово частот1« и выдающих на своих выходах в 1пр.оцессе дс гсиия «омер .просчитываемой иозицНИ в .двоич1Ю :м коде, и схем совиадения 6i-62,i, попарно исд-ключенйых к каждому двончисму элементу 5j-5,t делите,тя-раснределителя и в зависимости от -состояния двоичного элемеита нотерем-енно открываемых для сигналов с дешифратора маркерHoii грушиы J.

, схем овладеиия (t-62„ соеди.н.яются с :ПрёОбразо,в:атедя1МИ-1иа1КОй1Ителями 7i-7,,, которые иаканливают нмлульсы с выхода дещнф ратор.а 1, в течение заданного числа ц;гк.1 ав дел и те л я -р аоир ед ел ител я.

Напряжеиие с выходов накопителей ясаждого элемента делителя-рас-иределителя попарно сравнивают с помощью камоар:аторов 8i-8,1 .По истечении заданного числа циклов, онределяемого счетчиком циклов 9, производится опрос компараторов, в результате чего поразрядно одределяется, на каких накопителях в каждой из сравниваемых пар накопились большие иапряжеиия.

Если в данном р-азряде большее напряжение накоилено в наасапителе с нечетным номером, то с выхода КО-мларатора при апросе поступает импульс, а при иа1КОпЛенин большего напряжения IB накопителе с четным номерОМ имиу:1ьс iC выхода .компаратюра 1не ааступает. Опрос К.01М:паратора ироизводишся ло И1стечеНИ1И заданного числа циклОв работы делителяраспраделителя 4 имлульоов СО счетчика циклов 5. П-оСле опроса .происходит сброс налсопителя и;М1Пульоо.м опроса, заде1ржа ИНЫ1М яа линии задер к1ки 10.

При оьросе KOMiHapaTOp-QB на их выходах поразрядно формируется двоичный сигнал номера позиции, на которую чаще всего поступают импульсы с дещифратора 1 и которая с

наибольшей вероятностью является позицией начала цикла. Этот двоичный номер заПО,минается далее в узле формирователя 3. Узел формирования снихрослгиала 3 состоит из

триггеров залО|МИнания , на которых, но Окончанию заданного ЧИсла циклов, запоминается двоичный номер позиции начала ци-кла, выдаваемый ком парато1рами Si-8„ , из соединенных последовательно схем савпадения }2i-12п , которые подсоединены к выходам триггеров Запоминания 11 „ и ко вторым входам которых ПОдСОединены выходы двоичных элементов делителя-распределителя 4.

При иораарядном совладевии двоииного номера позиции нйчала цикла, записанного на триггерах запоминания lli-11 п , с комбинацией, избран-ной на элементах делителя-рас.пределителя 4, открываются лоразрядные схемы совладения 12i-}2п и. через них на устанОвку фазы делителя-распределителя 4 проходит такт01вый импульс, задержанный в пр.еделах п-ериода па линии задержки 13, который Производит установку фазы в момент просчета делителем-распределителем 4 позиции, номера -которой записаны на триггерах запоминания 11 -11 „ .

Предмет изобрете и и я

Устройство сиихронизации по циклам в канале адреоной системы связи, содержащее дешифратор маркерных групп, делитель, схемы совпадения, преобразователи-накопители «код-аналог и блоки сравнения, отличающееся тем, что, с щелью шрощения устройства, парафазйые выходы каждой авоичной ячейки делителя лодяслючены через схемы совпадения

ко входам лреобразавателей-накапителей, выходы которых соединены со входами блоков сравнения, при этом каждой двоичной ячейке делителя соответствует один блок сравнения, а ВЫХОДЫ указанных блоков лодключены ко

входам формирователя синхросигнала, причем ко входу каждой из носледовательно соединеиных схем совиа|дения формирователя синхросигнала шодключен. выход соофветстпующей ячейки делителя, а другие входы схем совпадения л.О1Дключены к выходам триггеров

запоминания формирователя синхросигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство синхронизации по циклам в дискретном канале связи | 1975 |

|

SU543181A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| Устройство синхронизации по циклам | 1974 |

|

SU565402A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ СИСТЕМ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1971 |

|

SU300955A1 |

| Устройство для контроля коммутации информационных каналов | 1982 |

|

SU1120333A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ СИСТЕМЫ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1970 |

|

SU279701A1 |

| Устройство для группового управления лифтами | 1982 |

|

SU1089024A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1993 |

|

RU2038634C1 |

Даты

1972-01-01—Публикация