(54) ДИНАМИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО И ФОРМИРОВАТЕЛЬ СИНХРОСИГНАЛОВ ДЛЯ НЕГО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Запоминающее устройство | 1985 |

|

SU1256096A1 |

| Электронно-счетный частотомер | 1981 |

|

SU1041947A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Динамическое запоминающее устройство | 1983 |

|

SU1166177A1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Устройство сопряжения анализатора технологического процесса с ЭВМ | 1983 |

|

SU1149271A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для считывания графической информации | 1987 |

|

SU1550549A1 |

1

Изобретение относится к запоминающим устройствам и может быть использовано для построения запоминающих устройств на полупроводниковых интегральных запоминающих микросхемах динамического типа (ЗМД).5

Известно запоминающее устройство, содержащее накопитель, группу элементов управляющей и дополнительной логики, адаптер и датчики синхросигналов 1.

Недостатками этого устройства являются ю низкие быстродействие и надежность.

Наиболее близким по техническому рещению к изобретению является динамическое запоминающее устройство, содержащее накопитель, блрк местного управления, включающий в себя датчик синхросигналов, блок 15 управления регенерацией и адаптер, выходы которого соединены с входами накопителя для обеспечения последнего управлением, синхронизацией и вводом-выводом соответствующей информации 2.20

Недостатками этого устройства являются увеличение периода регенерации при больщой длительности или высокой частоте запросов, а также прерывание цикла регенерации при поступлении запроса на обращение. Кроме того, применяемый в устройстве датчи синхросигналов не используется для управления каналами регенерации, что снижает быстродействие, надежность и уровень унификации устройства.

Известен также формирователь синхросигналов, содержащий генераторы, элементы задержки и делители частоты 3.

Недостатками этого формирователя являются низкие быстродействие и надежность, а также ограниченность области его применения, обусловленные отсутствием мультиплексного канала по входу, что не позволяет применить его в качестве общего блока для каналов записи/считывания и регенерации.

Цель изобретения - повыщение быстродействия и надежности устройства и .формирователя синхросигналов.

Поставленная цель достигается тем. что в динамическое запоминающее устройство, содержащее накопитель, мультивибратор, счетчик, блок местного управления, формирователь синхросигналов, блок управления регенерацией, входы которого являются входами обращения устройства, и блок согласования, одни из входов и выходов которого являются адресными входами, информационными входами и выходами устройства, а другие входы и выходы подключены соответственно к выходам блока местного управления, к одним из выходов счетчика, к информационным выходам, входам синхронизации, адресным и информационным входам накопителя, причем первый и второй управляемые входы блока местного управления соединены соответственно с первым и вторым выходами блока управления регенерацией, одни из выходов формирователя синхросигналов подключены соответственно к информационным входам блока местного управления и к счетному входу счетчика, введены формирователь строб-сигналов, формирователь длительности циклов, первый триггер, дифференцирующий элемент и первый элемент И-НЕ, причем первый и второй входы формирователя длительности, циклов соединены соответственно с третьим выходом блока управления регенерацией и с первым выходом формирователя строб-сигналов, а третий и четвертый входы - с другими выходами формирователя синхросигналов, первый вход которого подключен к третьему управляющему входу блока местного управления и первому выходу формирователя длительности циклов, второй вход которого соединен с четвертым управляемым входом блока местного управления, вторым входом формирователя синххросигналов и управляемым входом счетчика, другой выход которого подключен к первому входу формирователя строб-сигналов, второй, третий и четвертый входы которого соединены соответственно с выходом первого элемента И-НЕ, с выходом мультивибратора, с выходом дифференцирующего элемента и первым входом первого триггера, второй вход которого подключен к второму выходу формирователя строб-сигналов, а инверсный выход - к прямому входу первого элемента И-НЕ, первый и второй инверсные входы которого соединены соответственно с четвертым входом формирователя длительности циклов и с входом мультивибратора, входы дифференцирующего элемента и мультивибратора и третьи выходы формирователя строб-сигналов и формирователя длительности циклов являются соответственно входами запуска и управляющими выходами устройства. Формирователь строб-сигналовсодержит второй и третий триггеры, первый элемент И и первый элемент задержки, вход которого подключен к прямому выходу второго триггера, а. выход - установочному входу третьего триггера, инверсный выход которого соединен с первым входом первого элемента И, выход которого подключен к первому установочному входу второго триггера, прямой выход которого, выход первого элемента И и инверсный выход второго триггера являются соответственно первым, вторым и третьим выходами формирователя, входами с первого по четвертый которого

являются соответственно счетный вход третьего триггера, второй вход первого элемента И, второй установочный и счетный входы второго триггера.

Формирователь длительности циклов содержит четвертый и пятый триггеры, второй элемент И, элемент ИЛИ и второй элемент И-НЕ, первый вход которого, входы элемента ИЛИ и второй вход второго элемента И-НЕ являются соответственно входами с первого по четвертый формирователя, выходами которого являются прямой выход четвертого триггера, выход второго элемента И, и инверсный выход пятого триггера, причем первый и второй входы элемента ИЛИ соединены соответственно с первым и вторым входами второго элемента И, третий вход которого подключен к инверсному выходу четвертого триггера, прямой выход и установочный вход которого соединен соответственно с счетным входом и инверсным выходом пятого триггера, установочный вход которого подключен к первому входу второго элемента И-НЕ, третий вход которого соединен с выходом элемента ИЛИ, а выход - со счетным входом четвертого триггера.

Поставленная цель достигается также тем, что в формирователь синхросигналов, содержащий делители частоты, второй элемент задержки и генератор сигналов, прямой и инверсный выходы которого подключены соответственно к счетнЫм входам первого и второго делителей частоты, введен мультиплексор, первый и второй входы которого являются соответственно первым и вторым входами формирователя, выход мультиплексора соединен с входом генератора сигналов, а управляемый вход - с установочными входами делителей частоты и выходом второго элемента задержки, вход которого подключен к одному из инверсных выходов второго делителя частоты, причем счетные входы третьего и четвертого делителей частбты соединены соответственно с одними из прямых выходов первого и второго делителей частоты, другие прямые и инверсные выходы которых, выходы третьего и четвертого делителей частоты и выход второго элемента задержки являются выходами формирователя.

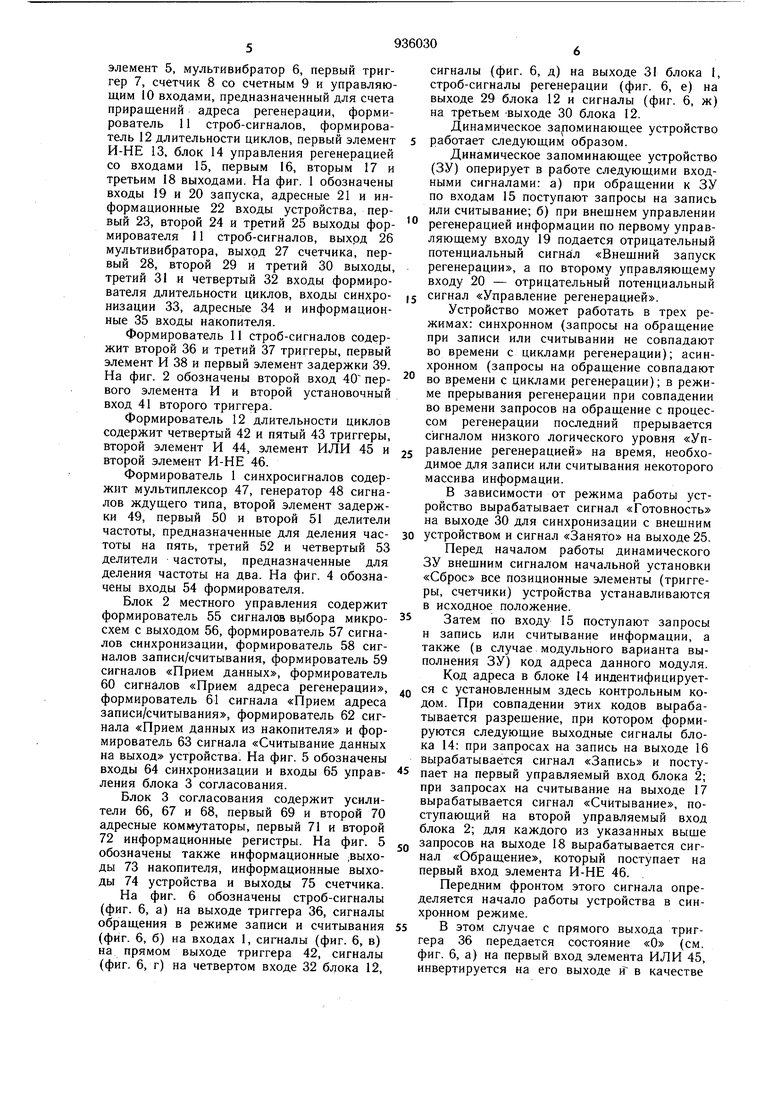

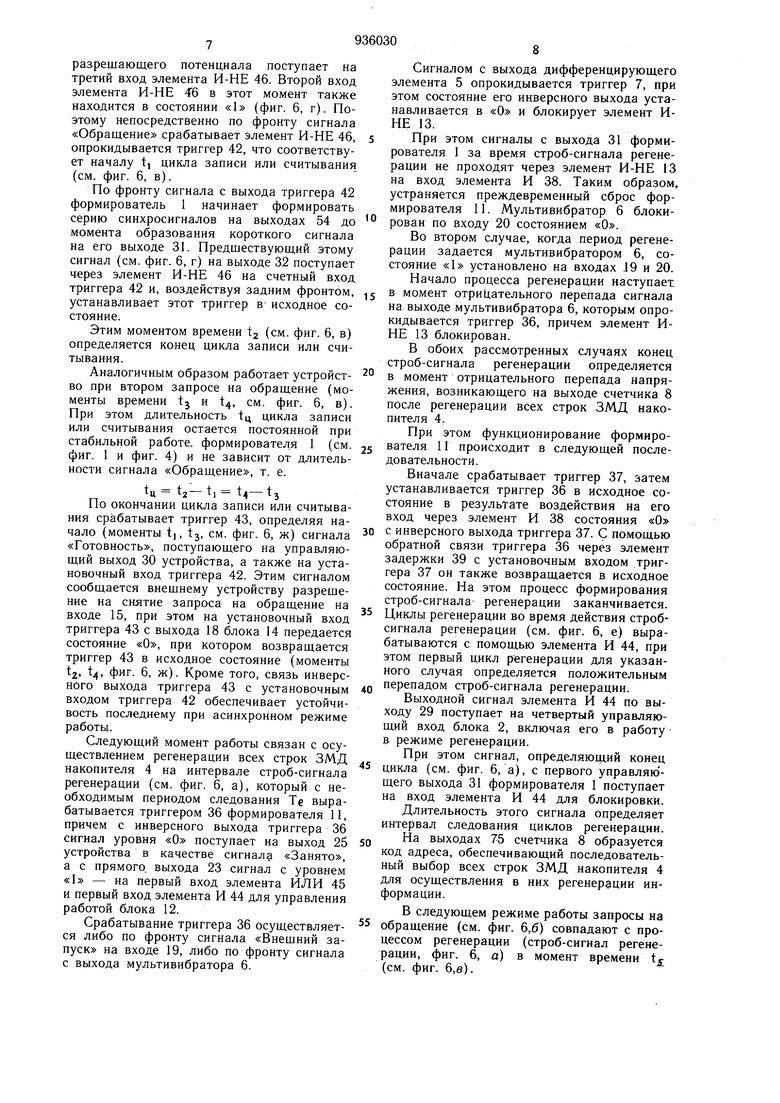

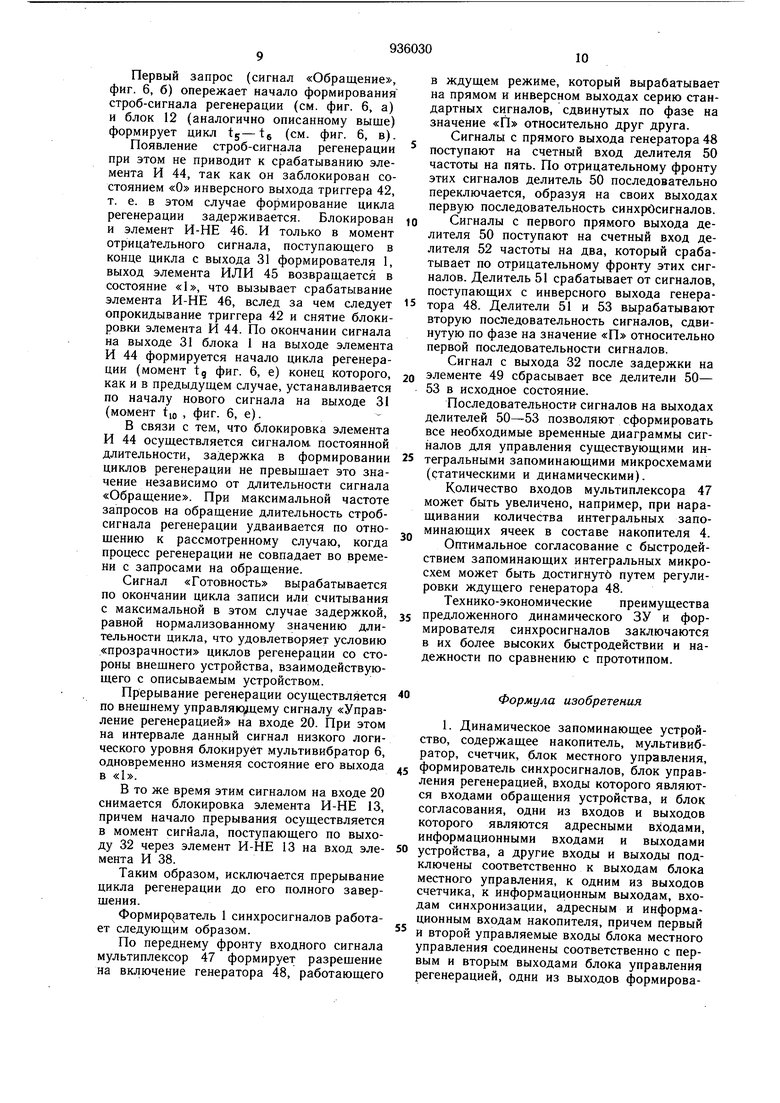

На фиг. 1 представлена функциональная схема предложенного устройства; на фиг. 2 и 3 - функциональная схема формирователя строб-сигналов; на фиг. 3 - функциональная схема формирователя длительности циклов; на фиг. 4 - функциональная схема предложенного формирователя синхросигналов; на фиг. 5 - функциональные схемы блока местного управления и блока.согласования; на фиг. 6 - диаграммы, поясняющие работу предложенного устройства.

Динамическое запоминающее устройство содержит формирователь 1 синхросигналов, блок 2 местного управления, блок 3 согласования, накопитель 4, дифференцирующий

элемент 5, мультивибратор б, первый триггер 7, счетчик 8 со счетным 9 и управляющим 10 входами, предназначенный для счета приращений адреса регенерации, формирователь 11 строб-сигналов, формирователь 12 длительности циклов, первый элемент И-НЕ 13, блок 14 управления регенерацией со входами 15, первым 16, вторым 17 и третьим 18 выходами. На фиг. 1 обозначены входы 19 и 20 запуска, адресные 21 и информационные 22 входы устройства, первый 23, второй 24 и третий 25 выходы формирователя 11 строб-сигналов, выход 26 мультивибратора, выход 27 счетчика, первый 28, второй 29 и третий 30 выходы, третий 31 и четвертый 32 входы формирователя длительности циклов, входы синхронизации 33, адресные 34 и информационные 35 входы накопителя.

Формирователь 11 строб-сигналов содержит второй 36 и третий 37 триггеры, первый элемент И 38 и первый элемент задержки 39. На фиг. 2 обозначены второй вход 40 первого элемента И и второй установочный вход 41 второго триггера.

Формирователь 12 длительности циклов содержит четвертый 42 и пятый 43 триггеры, второй элемент И 44, элемент ИЛИ 45 и второй элемент И-НЕ 46.

Формирователь 1 синхросигналов содержит мультиплексор 47, генератор 48 сигналов ждущего типа, второй элемент задержки 49, первый 50 и второй 51 делители частоты, предназначенные для деления частоты на пять, третий 52 и четвертый 53 делители частоты, предназначенные для деления частоты на два. На фиг. 4 обозначены входы 54 формирователя.

Блок 2 местного управления содержит формирователь 55 сигналов вь1бора микросхем с выходом 56, формирователь 57 сигналов синхронизации, формирователь 58 сигналов записи/считывания, формирователь 59 сигналов «Прием данных, формирователь 60 сигналов «Прием адреса регенерации, формирователь 61 сигнала «Прием адреса записи/считывания, формирователь 62 сигнала «Прием данных из накопителя и формирователь 63 сигнала «Считывание данных на выход устройства. На фиг. 5 обозначены входы 64 синхронизации и входы 65 управления блока 3 согласования.

Блок 3 согласования содержит усилители 66, 67 и 68, первый 69 и второй 70 адресные коммутаторы, первый 71 и второй 72 информационные регистры. На фиг. 5 обозначены также информационные .выходы 73 накопителя, информационные выходы 74 устройства и выходы 75 счетчика.

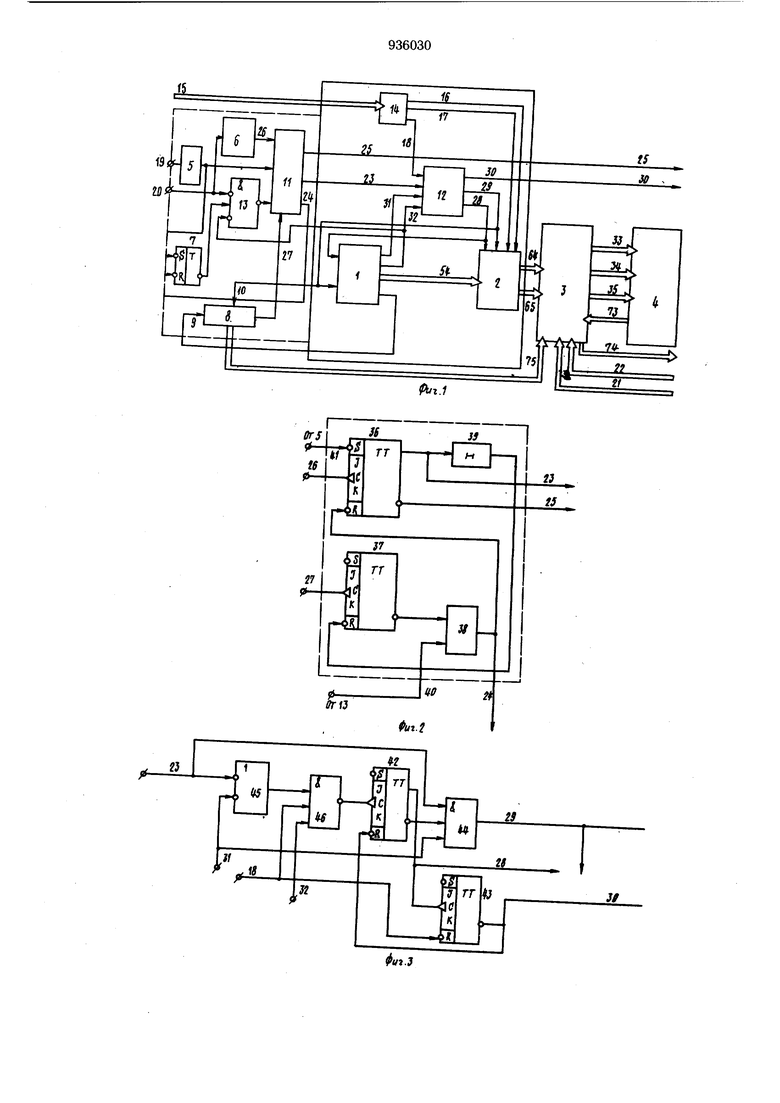

На фиг. 6 обозначены строб-сигналы (фиг. 6, а) на выходе триггера 36, сигналы обращения в режиме записи и считывания (фиг. 6, б) на входах 1, сигналы (фиг. 6, в) на прямом выходе триггера 42, сигналы (фиг. 6, г) на четвертом входе 32 блока 12,

сигналы (фиг. 6, д) на выходе 31 блока 1, строб-сигналы регенерации (фиг. 6, е) на выходе 29 блока 12 и сигналы (фиг. 6, ж) на третьем -выходе 30 блока 12.

Динамическое запоминающее устройство работает следующим образом.

Динамическое запоминающее устройство (ЗУ) оперирует в работе следующими входными сигналами: а) при обращении к ЗУ по входам 15 поступают запросы на запись или считывание; б) при внешнем управлении

° регенерацией информации по первому управляющему входу 19 подается отрицательный потенциальный сигнал «Внешний запуск регенерации, а по второму управляющему входу 20 - отрицательный потенциальный

5 сигнал «Управление регенерацией.

Устройство может работать в трех режимах: синхронном (запросы на обращение при записи или считывании не совпадают во времени с циклами регенерации); асинхронном (запросы на обращение совпадают

° во времени с циклами регенерации); в режиме прерывания регенерации при совпадении во времени запросов на обращение с процессом регенерации последний прерывается сигналом низкого логического уровня «Уп5 равление регенерацией на время, необходимое для записи или считывания некоторого массива информации.

В зависимости от режима работы устройство вырабатывает сигнал «Готовность на выходе 30 для синхронизации с внешним

0 устройством и сигнал «Занято на выходе 25. Перед началом работы динамического ЗУ внешним сигналом начальной установки «Сброс все позиционные элементы (триггеры, счетчики) устройства устанавливаются в исходное положение.

5 Затем по входу 15 поступают запросы н запись или считывание информации, а также (в случае модульного варианта выполнения ЗУ) код адреса данного модуля. Код адреса в блоке 14 индентифицируетQ ся с установленным здесь контрольным кодом. При совпадении этих кодов вырабатывается разрешение, при котором формируются следующие выходные сигналы блока 14: при запросах на запись на выходе 16 вырабатывается сигнал «Запись и поступает на первый управляемый вход блока 2; при запросах на считывание на выходе 17 вырабатывается сигнал «Считывание, поступающий на второй управляемый вход блока 2; для каждого из указанных выще

Q запросов на выходе 18 вырабатывается сигнал «Обращение, который поступает на первый вход элемента И-НЕ 46. ,

Передним фронтом этого сигнала определяется начало работы устройства в синхронном режиме.

5 В этом случае с прямого выхода триггера 36 передается состояние «О (см. фиг. 6, а) на первый вход элемента ИЛИ 45, инвертируется на его выходе й в качестве

разрешающего потенциала поступает на третий вход элемента И-НЕ 46. Второй вход элемента И-НЕ 46 в этот момент также находится в состоянии «1 (фиг. 6, г). Поэтому непосредственно по фронту сигнала «Обращение срабатывает элемент И-НЕ 46, опрокидывается триггер 42, что соответствует началу t, цикла записи или считывания (см. фиг. 6, в).

По фронту сигнала с выхода триггера 42 формирователь 1 начинает формировать серию синхросигналов на выходах 54 до момента образования короткого сигнала на его выходе 31. Предществующий этому сигнал (см. фиг. 6, г) на выходе 32 поступает через элемент И-НЕ 46 на счетный вход триггера 42 и, воздействуя задним фронтом, устанавливает этот триггер в- исходное состояние.

Этим моментом времени iz (см. фиг. 6, в) определяется конец цикла записи или считывания.

Аналогичным образом работает устройство при втором запросе на обращение (моменты времени tj и t4, см. фиг. 6, в). При этом длительность 1ц цикла записи или считывания остается постоянной при стабильной работе, формирователя 1 (см. фиг. 1 и фиг. 4) и не зависит от длительности сигнала «Обращение, т. е.

, t4-t3

По окончании цикла записи или считывания срабатывает триггер 43, определяя начало (моменты t, tj, см. фиг. 6, ж) сигнала «Готовность, поступающего на управляющий выход 30 устройства, а также на установочный вход триггера 42. Этим сигналом сообщается внещнему устройству разрещение на снятие запроса на обращение на входе 15, при этом на установочный вход триггера 43 с выхода 18 блока 14 передается состояние «О, при котором возвращается триггер 43 в исходное состояние (моменты t,, t, фиг. 6, ж). Кроме того, связь инверсного выхода триггера 43 с установочным входом триггера 42 обеспечивает устойчивость последнему при асинхронном режиме работы.

Следующий момент работы связан с осуществлением регенерации всех строк ЗМД накопителя 4 на интервале строб-сигнала регенерации (см. фиг. 6, а), который с необходимым периодом следования Те вырабатывается триггером 36 формирователя 11, причем с инверсного выхода триггера 36 сигнал уровня «О поступает на выход 25 устройства в качестве сигнала «Занято, а с прямого, выхода 23 сигнал с уровнем «1 - на первый вход элемента ИЛИ 45 и первый вход элем.ента И 44 для управления работой блока 12.

Срабатывание триггера 36 осуществляется либо по фронту сигнала «Внещний запуск на входе 19, либо по фронту сигнала с выхода мультивибратора 6.

Сигналом с выхода дифференцирующего элемента 5 опрокидывается триггер 7, при этом состояние его инверсного выхода устанавливается в «О и блокирует элемент ИНЕ 13.

При этом сигналы с выхода 31 формирователя 1 за время строб-сигнала регенерации не проходят через элемент И-НЕ 13 на вход элемента И 38. Таким образом, устраняется преждевременный сброс формирователя И. Мультивибратор 6 блокирован по входу 20 состоянием «О.

Во втором случае, когда период регенерации задается мультивибратором 6, состояние «1 установлено на входах J9 и 20.

Начало процесса регенерации наступает в момент отрицательного перепада сигнала на выходе мультивибратора 6, которым опрокидывается триггер 36, причем элемент ИНЕ 13 блокирован.

В обоих рассмотренных случаях конец строб-сигнала регенерации определяется в момент отрицательного перепада напряжения, возникающего на выходе счетчика 8 после регенерации всех строк ЗМД накопителя 4.

При этом функционирование формирователя 11 происходит в следующей последовательности.

Вначале срабатывает триггер 37, затем устанавливается триггер 36 в исходное состояние в результате воздействия на его вход через элемент И 38 состояния «О с инверсного выхода триггера 37. С помощью обратной связи триггера 36 через элемент задержки 39 с установочным входом триггера 37 он также возвращается в исходное состояние. На этом процесс формирования строб-сигнала регенерации заканчивается. Циклы регенерации во время действия стробсигнала регенерации (см. фиг. 6, е) вырабатываются с помощью элемента И 44, при этом первый цикл регенерации для указанного случая определяется положительным перепадом строб-сигнала регенерации.

Выходной сигнал элемента И 44 по выходу 29 поступает на четвертый управляющий вход блока 2, включая его в работу В режиме регенерации.

При этом сигнал, определяющий конец цикла (см. фиг. 6, а), с первого управляющего выхода 31 формирователя 1 поступает на вход элемента И 44 для блокировки.

Длительность этого сигнала определяет интервал следования циклов регенерации.

На выходах 75 счетчика 8 образуется код адреса, обеспечивающий последовательный выбор всех строк ЗМД накопителя 4 для осуществления в них регенерации информации.

В следующем режиме работы запросы на обращение (см. фиг. 6,6) совпадают с процессом регенерации (строб-сигнал регенерации, фиг. 6, а) в момент времени (см. фиг. 6,в).

Первый запрос (сигнал «Обращение, фиг. 6, б) опережает начало формирования строб-сигнала регенерации (см. фиг. 6, а) и блок 12 (аналогично описанному выше) формирует цикл (см. фиг. 6, в).

Появление строб-сигнала регенерации при этом не приводит к срабатыванию элемента И 44, так как он заблокирован состоянием «О инверсного выхода триггера 42, т. е. в этом случае формирование цикла регенерации задерживается. Блокирован и элемент И-НЕ 46. И только в момент отрицательного сигнала, поступающего в конце цикла с выхода 31 формирователя 1, выход элемента ИЛИ 45 возвращается в состояние «1, что вызывает срабатывание элемента И-НЕ 46, вслед за чем следует опрокидывание триггера 42 и снятие блокировки элемента И 44. По окончании сигнала на выходе 31 блока 1 на выходе элемента И 44 формируется начало цикла регенерации (момент tq фиг. 6, е) конец которого, как и в предыдущем случае, устанавливается по началу нового сигнала на выходе 31 (момент tio , фиг. 6, е).

В связи с тем, что блокировка элемента И 44 осуществляется сигналом, постоянной длительности, задержка в формировании циклов регенерации не превышает это значение независимо от длительности сигнала «Обращение. При максимальной частоте запросов на обращение длительность стробсигнала регенерации удваивается по отношению к рассмотренному случаю, когда процесс регенерации не совпадает во времени с запросами на обращение.

Сигнал «Готовность вырабатывается по окончании цикла записи или считывания с максимальной в этом случае задержкой, равной нормализованному значению длительности цикла, что удовлетворяет условию «прозрачности циклов регенерации со стороны внешнего устройства, взаимодействующего с описываемым устройством.

Прерывание регенерации осуществляется по внешнему управляюдцему сигналу «Управление регенерацией на входе 20. При этом на интервале данный сигнал низкого логического уровня блокирует мультивибратор 6, одновременно изменяя состояние его выхода в «Ь.

В то же время этим сигналом на входе 20 снимается блокировка элемента И-НЕ 13, причем начало прерывания осуществляется в момент сигнала, поступающего по выходу 32 через элемент И-НЕ 13 на вход элемента И 38.

Таким образом, исключается прерывание цикла регенерации до его полного завершения.

Формир9ватель 1 синхросигналов работает следующим образом.

По переднему фронту входного сигнала мультиплексор 47 формирует разрешение на включение генератора 48, работающего

в ждущем режиме, который вырабатывает на прямом и инверсном выходах серию стандартных сигналов, сдвинутых по фазе на значение «П относительно друг друга.

Сигналы с прямого выхода генератора 48 поступают на счетный вход делителя 50 частоты на пять. По отрицательному фронту этих сигналов делитель 50 последовательно переключается, образуя на своих выходах первую последовательность синхросигналов. Сигналы с первого прямого выхода делителя 50 поступают на счетный вход делителя 52 частоты на два, который срабатывает по отрицательному фронту этих сигналов. Делитель 51 срабатывает от сигналов, поступающих с инверсного выхода генератора 48. Делители 51 и 53 вырабатывают вторую последовательность сигналов, сдвинутую по фазе на значение «П относительно первой последовательности сигналов.

Сигнал с выхода 32 после задержки на элементе 49 сбрасывает все делители 50- 53 в исходное состояние.

Последовательности сигналов на выходах делителей 50-53 позволяют сформировать все необходимые временные диаграммы сигналов для управления существующими интегральными запоминающими микросхемами (статическими и динамическими).

Количество входов мультиплексора 47 может быть увеличено, например, при наращивании количества интегральных запоминающих ячеек в составе накопителя 4.

Оптимальное согласование с быстродействием запоминающих интегральных микросхем может быть достигнуть путем регулировки ждущего генератора 48.

Технико-экономические преимущества предложенного динамического ЗУ и формирователя синхросигналов заключаются в их более высоких быстродействии и надежности по сравнению с прототипом.

40

Формула изобретения

формирователь синхросигналов, блок управления регенерацией, входы которого являются входами обращения устройства, и блок согласования, одни из входов и выходов которого являются адресными входами, информационными входами и выходами

устройства, а другие входы и выходы подключены соответственно к выходам блока местного управления, к одним из выходов счетчика, к информационным выходам, входам синхронизации, адресным и информационным входам накопителя, причем первый и второй управляемые входы блока местного управления соединены соответственно с первым и вторым выходами блока управления регенерацией, одни из выходов формирователя синхросигналов подключены соответственно к информационным входам блока местного управления и к счетному входу счетчика, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, оно содержит формирователь строб-сигналов, формирователь длительности циклов, первый триггер, дифференцирующий элемент и первый элемент И-НЕ, причём первый и второй входы формирователя длительности циклов соединены соответственно с третьим выходом блока управления регенерацией и с первым выходом формирователя строб-сигналов, а третий и четвертый входы - с другими выходами формирователя синхросигналов, первый вход которого подключен к третьему управляющему входу блока местного управления и первому выходу формирователя длительности циклов, второй выход которого соединен с четвертым управляемым входом блока местного управления, вторым входом формирователя синхросигналов и управляемым входом счетчика другой выход которого подключен к первому входу формирователя строб-сигналов, второй, третий и четвертый входы которого соединены соответственно с выходом первого элемента И-НЕ, с выходом мультивибратора, с выходом дифференцирующего элемента и первым входом первого триггера, второй вход которого подключен к второму выходу формирователя строб-сигналов, а инверсный выход - к прямому входу первого элемента И-НЕ, первый и второй инверсные входы которого соединены соответственно с четвертым входом формирователя длительности циклов и с входом мультивибратора, входы дифференцирующего элемента и мультивибратора и третьи выходы формирователя строб-сигналов и -формир ователя длительности циклов являются соответственно входами запуска и управляющими выходами устройства. 2. Устройство по п. 1, отличающееся тем, что формирователь строб-сигналов содержит второй и третий триггеры, первый элемент И и первый элемент задержки, вход которого подключен к прямому выходу второго триггера, а выход - к установочному входу третьего триггера, инверсный выход которого соединен с первым входом первого элемента И, выход которого подключен к первому установочному входу второго триггера, прямой выход которого, выход первого элемента И и инверсный выход второго триггера являются соответственно первым, вторым и третьим выходами формирователя, входами с первого по четвертый которого являются соответственно счетный вход третьего триггера, второй вход первого элемента И, второй установочный и счетный входы второго триггера. 3.Устройство по пп. 1 и 2, отличающееся тем, что формирователь длительности циклов содержит четвертый и пятый триггеры, второй элемент И, элемент ИЛИ и второй элемент И-НЕ, первый вход которого, входы элемента ИЛИ и второй вход второго элементы И-НЕ являются соответственно входами спервого по четвертый формирователя, выходами которого являются прямой выход четвертого триггера, выход второго элемента И и инверсный выход пятого триггера, причем первый и второй входы элемента ИЛИ соединены соответственно с первым и вторым входами второго элемента И, третий вход которого подключен к инверсному выходу четвертого триггера, прямой выход и установочный вход которого соединены соответственно со счетным входолт и инверсным выходом пятого триггера, установочный вход которого подключен к первому входу второго элемента И-НЕ, третий вход которого соединен с выходом элемента ИЛИ, а выход - со счетным входом, четвертого триггера. 4.Формирователь синхросигналов, содержащий делители частоты, второй элемент задержки и генератор сигналов, прямой и инверсный выходы которого подключены соответственно к счетным входам первого и второго делителей частоты, отличающийся ° Целью повыщения быстродействия и надежности формирователя, он содержит мультиплексор, первый и второй входы которого являются соответственно первым и вторым входами формирователя, выход мультиплексора соединен с входом генератора сигналов, а управляемый вход - с установочными входами делителей частоты и выходом второго элемента задержки, вход которого подключен к одному из инверсных выходов второго делителя частоты, причем счетные входы третьего и четвертого делителей частоты соединены соответственно с одними из прямых выходов первого и второго делителей ч.астоты, другие прямые и инверсные выходы которых, выходы третьего и четвертого делителей частоты и выход второго элемента задержки являются выходами формирователя. Источники информации, принятые во внимание при экспертизе 1.Приборы и техника эксперимента. 1978, № б, с. 41-45. 2.Патент США № 379D961, кл. G 11 С 11/34, 1974 (прототип). 2. В помощь радиолюбителю. Вып. 52, М., ДОСААФ, 1976, с. 41-53 (прототип).

fui.S

Авторы

Даты

1982-06-15—Публикация

1980-08-08—Подача