(54) УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1971 |

|

SU307482A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Система для асинхронного сопряжения импульсных потоков | 1986 |

|

SU1420670A1 |

| Устройство синхронизации по несущей частоте | 1983 |

|

SU1124440A1 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Устройство для приема дискретной информации | 1983 |

|

SU1111260A1 |

| Устройство тактовой синхронизациии РЕгЕНЕРАции | 1979 |

|

SU809620A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ ШИРОКОПОЛОСНЫХ ШУМОПОДОБНЫХ СИГНАЛОВ | 1979 |

|

SU1840109A1 |

1

Изовретение относится к связи и может исполь ваться в аппаратуре систем передачу данных.

Известно устройство синхронизации по циклам в дискретном канете связи, содержащее делитель частоты, выходы ячеек которого подключены к входам формирователя синхросигналов, деьшфратор маркерных групп, выход которого подключен через элементы И к соответствующим накопителям, формирователи стробов, через которые выходы каждой ячейки делителя подключены к вторым входам соответствующих элементов И, а также блоки выделения максимума, через которые выходы на.копителей подключены к дополнительным входам фор№1рователя синхросигналов i .

Наиболее близкое , к предлагаемому изобретению устройство фазовой синхронизации содержит последовательно соединенные местный генератор и линию задержки, выходы которой подключены к первым входам блока совпадений, к вторым входам которого под- . ключены соответствующие выходы блока памяти Г а выходы блока совпадений подключены к соответствующим входам блока сборки L2 .

Однако известные устройства затрачивсют значительное время на вхождение в синхронизм и не работоспособны при частоте фазирующего сигнала, в кратное число раз меньшей частоты местного генератора.

Цель изобретения - сокращение времени вхождения в синхронизм и обеспечение работы устройства при частот фазирунедего сигнала, меньшей частоты местного генератора в кратное число раз.

Для эгого в устройство фазовой синхронизации, содержащее последоват ьно соединенные местный генератор и линию задержки, выходы которой подключены к первым входам блока совпадений, к вторым входам которого подключены соответствующие выходы блока пё1мяти, а выходы блока совпадений подключены к соответствующим входам блока сборки, введены элемент згидержки и дополнительный блок совпадений, при этом фазирующий сигнал подан на вход сброса блока памяти и на вход элемента згщержки,-выход которого подключен к одним входам дополнительного блока совпадений, к другим входг1м которого подключены соответствующие выходы линии задержки, а выходы дополнительного блока совпадений подключены к дополнительным входам блока сборки, выходы которог -тюдключены к соответствующим установочным входам блока памяти.

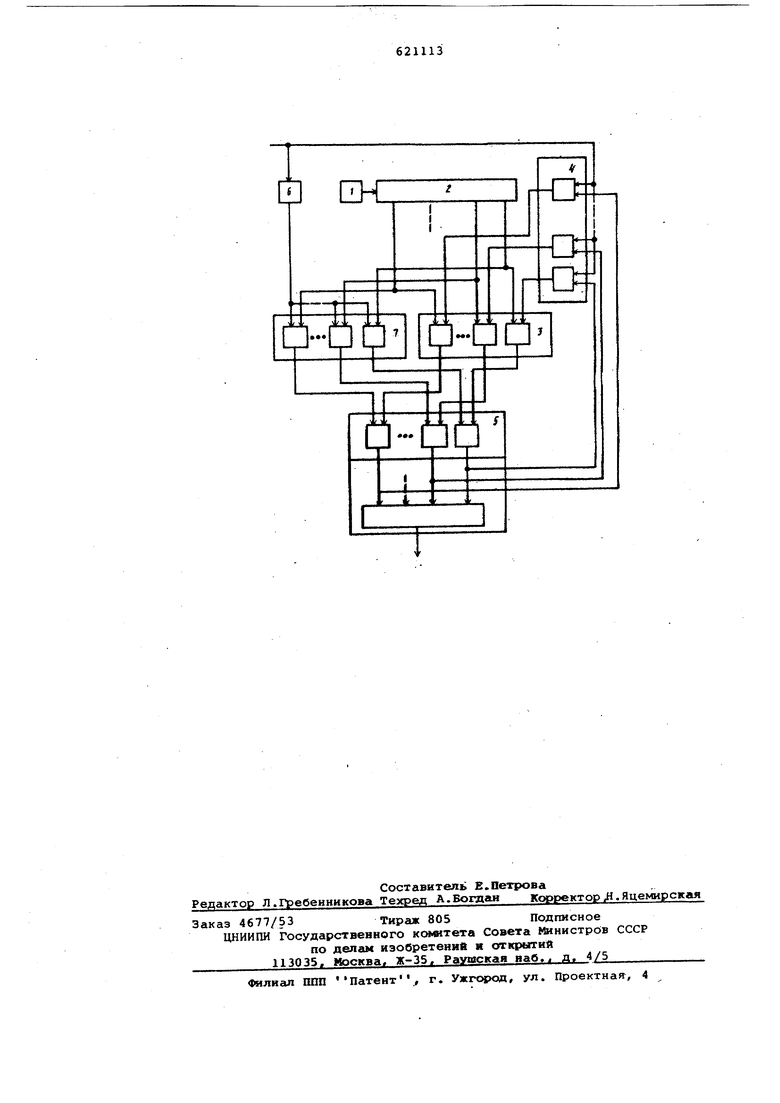

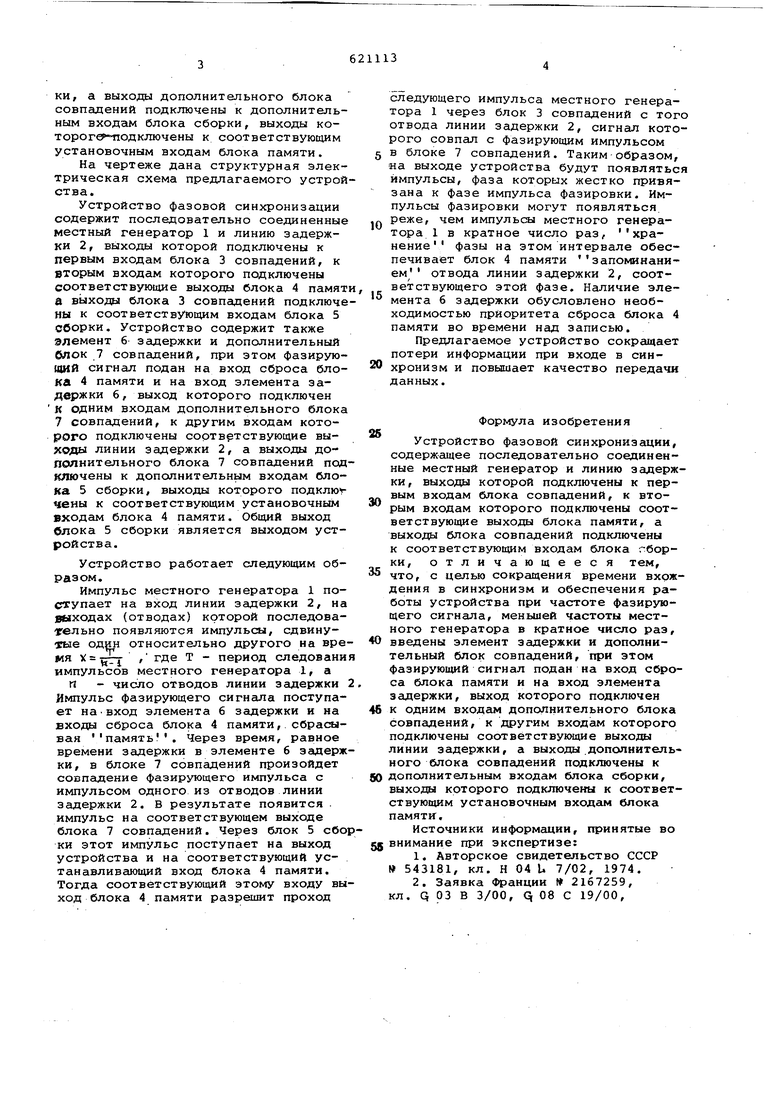

На чертеже дана структурная электрическая схема предлагаемого устройства.

Устройство фазовой синхронизации содержит последовательно соединенные местный генератор 1 и линию задержки 2, выходы которой подключены к первым входам блока 3 совпадений, к вторым входам которого подключены соответствующие выходы блока 4 памят а выходы блока 3 совпадений подключены к соответствующим входам блока 5 Сборки. Устройство содержит также элемент б задержки и дополнительный блок 7 совпадений, при этом фазирующий сигнал подан на вход сброса блока 4 памяти и на вход элемента задержки 6, выход которого подключен к одним входам дополнительного блока 7 совпадений, к другим входам которого подключены соответствующие выходы линии задержки 2, а выходы дополнительного блока 7 совпадений подключены к дополнительным входам блока 5 сборки, выходы которого подключаемы к соответствующим установочным входам блока 4 памяти. Общий выход блока 5 сборки является выходом устройства.

Устройство работает следующим образом.

Импульс местного генератора 1 поступает на вход линии задержки 2, на выходах (отводах) которой последовагельно появляются импульсы, сдвинутые один относительно другого на время X rj / где Т - период следовани импульсов местного генератора 1, а

п - число отводов линии задержки Импульс фазирующего сигнала поступает на-вход элемента 6 задержки и на входы сброса блока 4 памяти,. сбрасывая память . Через время, равное времени задержки в элементе 6 задержки, в блоке 7 совпадений произойдет совпещение фазирующего импульса с импульсом одного из отводов линии задержки 2. В результате появится импульс на соответствующем выходе блока 7 совпадений. Через блок 5 сбоки этот импульс поступает на выход устройства и на соответствующий устанавливающий вход блока 4 памяти. Тогда соответствующий этому входу выход блока 4 памяти разреишт проход

следующего импульса местного генератора 1 через блок 3 совпадений с того отвода линии задержки 2, сигнал которого совпал с фазирующим импульсом

в блоке 7 совпадений. Таким образом, на выходе устройства будут появляться импульсы, фаза которых жестко привязана к фазе импульса фазировки. Импульсы фазировки могут появляться.

„ реже, чем импульсы местного генератора 1 в кратное число раз, хранение фазы на этом интервале обеспечивает блок 4 памяти запоминанием отвода линии задержки 2, соответствующего этой фазе. Наличие элемента 6 згщержки обусловлено необходимостью приоритета сброса блока 4 памяти во времени над записью.

Предлагаемое устройство сокращает потери информации при входе в синхронизм и повышает качество передачи данных.

Формула изобретения

Устройство фазовой синхронизгщии, содержсццее последовательно соединенные местный генератор и линию задержки , выходы которой подключены к первым входам блока совпгщений, к вторым входам которого подключены соответствующие выходы блока памяти, а выходы блока совпадений подключены к соответствующим входам блока гборки, отличающееся тем, что, с целью сокращения времени вхождения в синхронизм и обеспечения работы устройства при частоте фазирующего сигнала, меньшей частоты местного генератора в кратное число раз,

введены элемент задержки и дополнительный блок совпадений, при этом фазирующий сигнал подан на вход сброса блока памяти и на вход элемента задержки, выход которого подключен

5 к одним входам дополнительного блока совпадений, к другим входам которого подключены соответствующие выходы линии задержки, а выходы дополнительного блока совпс1дений подключены к

0 дополнительным входам блока сборки, выходы которого подключены к соответствующим установочным входам блока памяти.

Источники информации, принятые во

g внимание при экспертизе:

кл. q 03 В 3/00, q 08 С i9/oo.

Авторы

Даты

1978-08-25—Публикация

1977-03-21—Подача