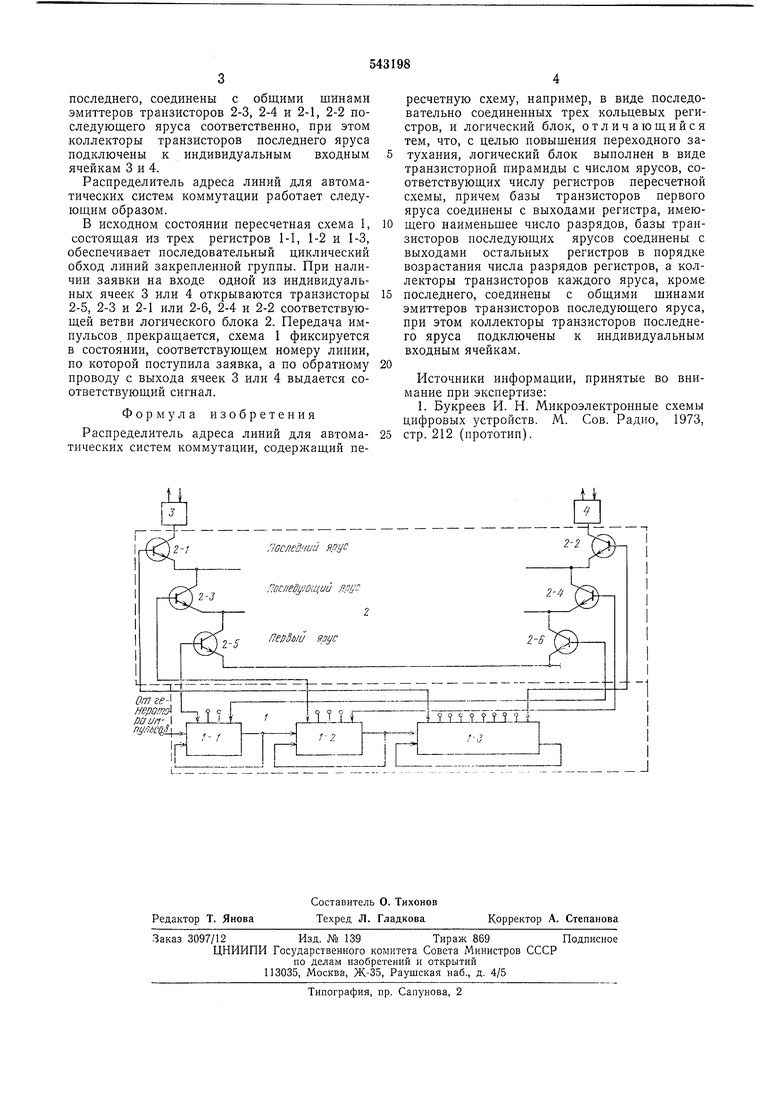

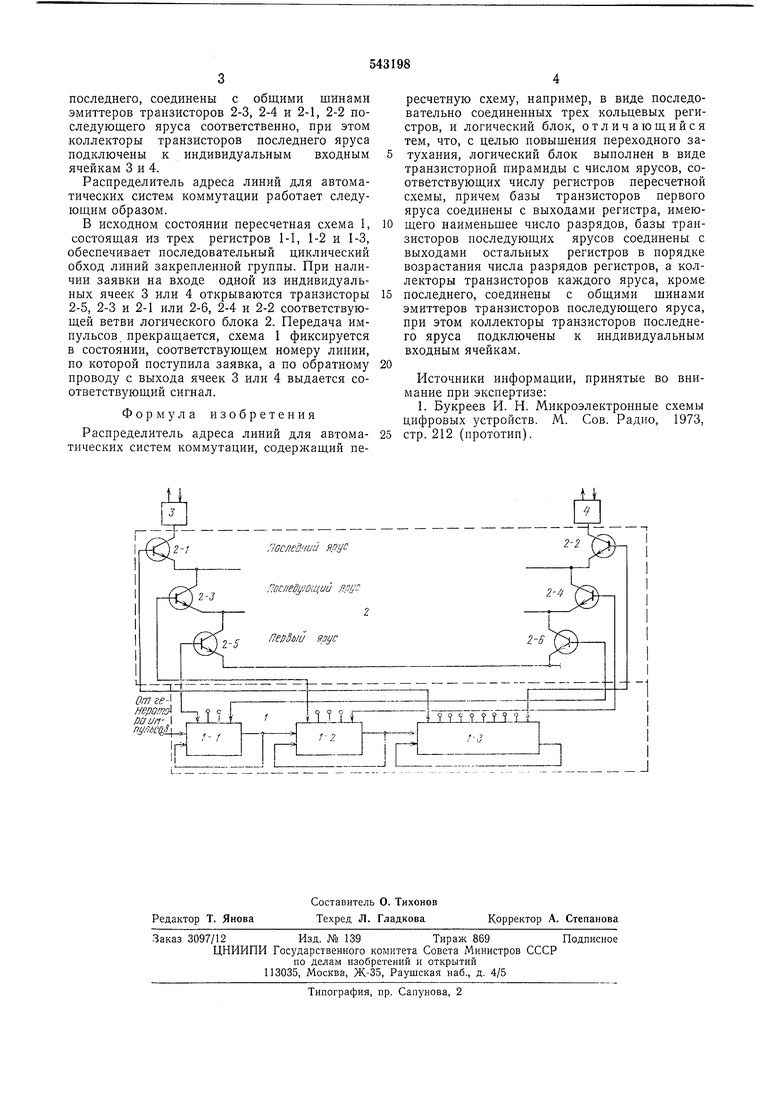

последнего, соединены с общими шинами эмиттеров транзисторов 2-3, 2-4 и 2-1, 2-2 последующего яруса соответственно, при этом коллекторы транзисторов последнего яруса подключены к индивидуальным входным ячейкам 3 и 4.

Распределитель адреса линий для автоматических систем коммутации работает следующим образом.

В исходном состоянии пересчетная схема 1, состоящая из трех регистров 1-1, 1-2 и 1-3, обеспечивает последовательный циклический обход линий закрепленной группы. При наличии заявки на входе одной из индивидуальных ячеек 3 или 4 открываются транзисторы 2-5, 2-3 и 2-1 или 2-6, 2-4 и 2-2 соответствующей ветви логического блока 2. Передача импульсов прекращается, схема 1 фиксируется в состоянии, соответствующем номеру линии, по которой поступила заявка, а по обратному проводу с выхода ячеек 3 или 4 выдается соответствующий сигнал.

Формула изобретения

Распределитель адреса линий для автоматических систем коммутации, содержащий пересчетную схему, например, в виде последовательно соединенных трех кольцевых регистров, и логический блок, отличающийся тем, что, с целью повышения переходного затухания, логический блок выполнен в виде транзисторной пирамиды с числом ярусов, соответствующих числу регистров пересчетной схемы, причем базы транзисторов первого яруса соединены с выходами регистра, имеющего наименьшее число разрядов, базы транзисторов последующих ярусов соединены с выходами остальных регистров в порядке возрастания числа разрядов регистров, а коллекторы транзисторов каждого яруса, кроме

последнего, соединены с общими шинами эмиттеров транзисторов последующего яруса, при этом коллекторы транзисторов последнего яруса подключены к индивидуальным входным ячейкам.

Источники информации, принятые во внимание при экспертизе:

1. Букреев И. Н. Микроэлектронные схемы цифровых устройств. М. Сов. Радио, 1973,

стр. 212 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресно-разрядной выборки системы 2,5 д | 1973 |

|

SU531277A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| КОЛЬЦЕВАЯ ПЕРЕСЧЕТНАЯ СХВЛ\А | 1973 |

|

SU365844A1 |

| Коммутационная ячейка | 1972 |

|

SU447839A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| Импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1571561A1 |

| Устройство для программного управления объектом | 1988 |

|

SU1605211A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

Авторы

Даты

1977-01-15—Публикация

1974-01-02—Подача