1

Изобретение относится к автоматике и измерительной технике и может быть использовано в цифровых измерителях частоты.

Известен умножитель частоты следования импульсов, содержащий делитель опорной частоты, счетчик импульсов,, входной и выходной формирователи, запоминающий регистр, счетчик импульсов опорной частоты, блок управления {1 .

Недостатком этого устройства является сравнительно невысокая-точность умножения.

Наиболее близким к предлагаемому является устройство умножения частоты следования импульсов, содержащее входной формирователь импульсов, выход которого соединен с первым входом счетчика поделенной опорной частоты, второй вход которого соединен с выходом делителя опорной частоты, первый выход - с первым входом первого элемента сравнения, второй выход - с первым входом запоминающего регистра, второй вход которого подключен к первому входу делителя опорной частоты, второму выходу блока управления, входу счетчика опорной частоты I и второму входу триггера, второй вход которого соединен с выходом выходного (Формирователя импульсов, третий - с выходом клапана, а выход - с первым входом второго элемента сравнения, второй вход которого соединен с выходом запоминающего регистра, а выход - с входом выходного формирователя импульсов, при этом первый вход клайана соеди0нен с шиной опорной частоты и вторым входом делителя опорной частоты,второй вход - с выходом триггера, первый вход которого соединен с выходом первого элемента сравнения (2J.

5

Недостатком данного устройства является низкая точность.

Цель изобретения - повышение точности умножения.

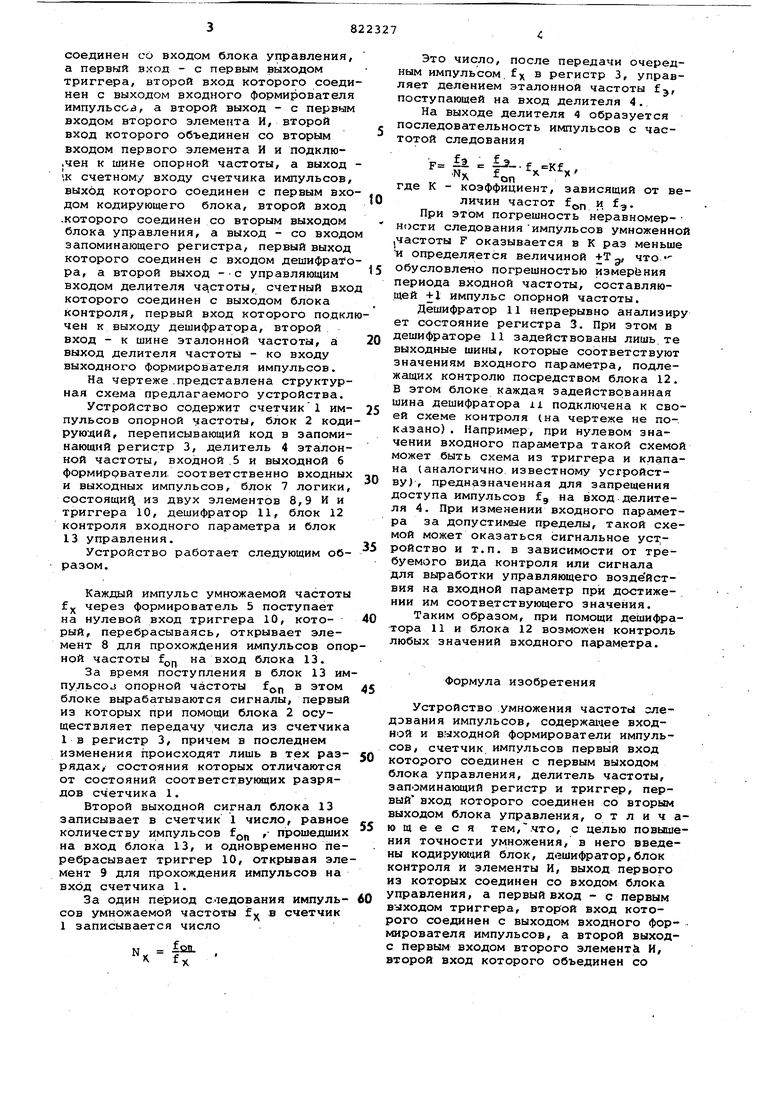

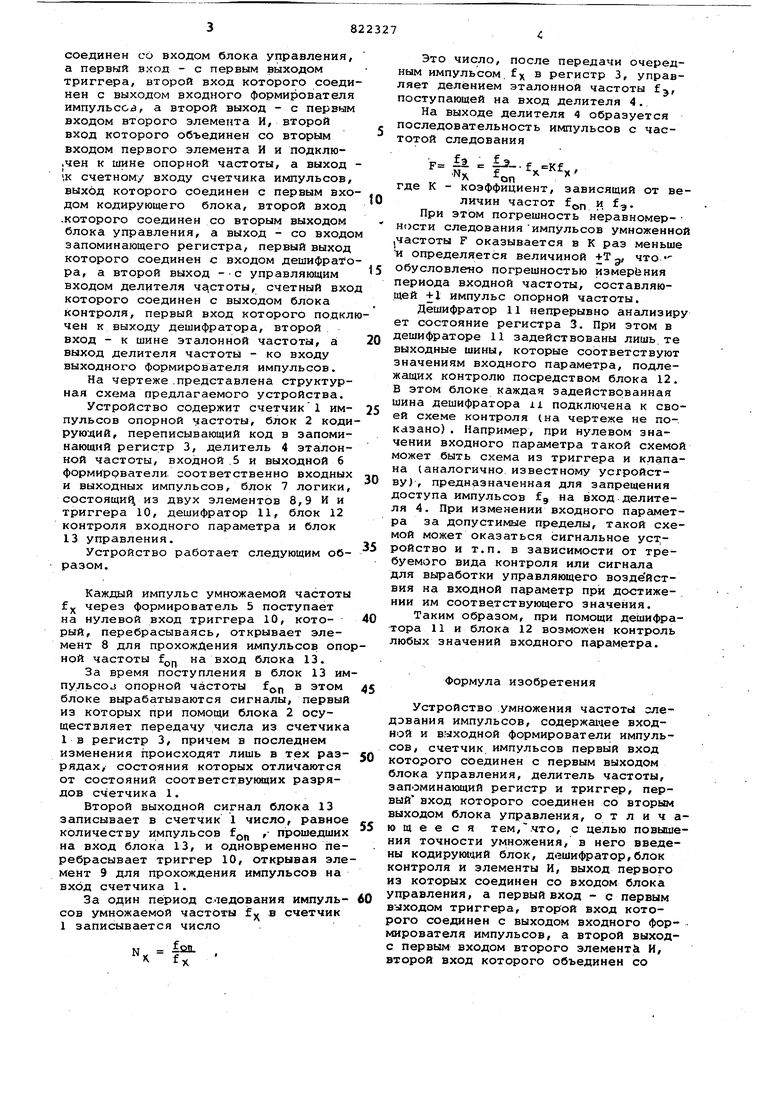

Для достижения этой цели в устрой0ство умножения частоты следования импульсов, содержащее входной и выходной фсфмирователи импульсов, сч.етчик импульсов, первый вход кот орого соединен с первым выходом блока уп5равления, делитель частоты, запоминакнций регистр и триггер, первый вход которого соединен со вторым выходом блока управ.т1ения, введены кодирующий блок, дешифратор, блок контроля и 0 элементы .И, выход первого из которых соединен со входом блока управления, а первый вход - с первым выходом триггера, второй вход которого соеди нен с выходом входного формирователя импульсов, а второй выход - с первым входом второго элемента И, второй вход которого объединен со вторым входом первого элемента И и подклю,чен к шине опорной частоты, а выход ,к счетному входу счетчика импульсов, выход которого соединен с первым вхо дом кодирующего блока, второй вход .которого соединен со вторым выходом блока управления, а выход - со входо запоминающего регистра, первый выход которого соединен с входом дешифрато ра, а второй выход --с управляющим входом делителя ча.стоты, счетный вхо которого соединен с выходом блока контроля, первый вход которого подкл чен к выходу дешифратора, второй вход - к шине эталонной частоты, а выход делителя частоты - ко входу выходног-о формирователя импульсов. На чертеже .представлена структурная схема предлагаемого устройства. Устройство содержит счетчик1 импульсов опорной частоты, блок 2 коди руюдий, переписывающий код в запоминающий регистр 3, делитель 4 эталонной частоты, входной .5 и выходной 6 формирователи, соответственно входных и выходных импульсов, блок 7 логики, состоящий из двух элементов 8,9 И и триггера 10, дешифратор 11, блок 12 контроля входного параметра и блок 13 управления. Устройство работает следующим образом. Каждый импульс умножаемой частоты f через формирователь 5 поступает на нулевой вход триггера 10, который, перебрасываясь, открывает элемент 8 для прохождения импульсов опо ной частоты fpj на вход блока 13. За время поступления в блок 13 им пульсов опорной частоты fj, в этом блоке вырабатываются сигналы, первый из которых при помощи блока 2 осуществляет передачу числа из счетчика 1 в регистр 3, причем в последнем изменения происходят лишь в тех разрядах, состояния которых отличаются от состояний соответствующих разрядов счетчика 1. Второй выходной сигнал блока 13 записывает в счетчик 1 число, равное количеству импульсов fQ ,- прошедших на вход блока 13, и одновременно перебрасывает триггер 10, открывая эле мент 9 для прохождения импульсов на вход счетчика 1. За один период саедования импульсов умножаемой частоты f в счетчик 1 записывается число Это число, после передачи очередным импульсом.fx в регистр 3, управляет делением эталонной частоты f, поступающей на вход делителя 4, На выходе делителя 4 образуется последовательность импульсов с частотой следования F ,, Nx fon где К - коэффициент, зависящий от величин частот fjjn и fэ. При этом погрешность неравнрмер- ности следованияимпульсов умноженной )Частоты F оказывается в К раз меньше и определяется величиной +Т д, что обусловлено погрешностью измерения периода входной частоты, составляющей +1 импульс опорной частоты. Дешифратор 11 непрерывно анализиру ет состояние регистра 3. При этом в дешифраторе 11 задействованы лишь, те выходные шины, которые соответствуют значениям входного параметра, подлежащих контролю посредством блока 12. В этом блоке каждая задействованная шина дешифратора и подключена к своей схеме контроля (на чертеже не по-, казано). Например, при нулевом значении входного параметра такой схемой может быть схема из триггера и клапана (аналогично известному устройству) , предназначенная для запрещения доступа импульсов fg на вход делителя 4. При изменении входного параметра за допустимые пределы, такой схемой может оказаться сигнальное устройство и т.п. в зависимости от требуемого вида контроля или сигнала для выработки управляющего воздействия на входной параметр при достижении им соответствующего значения. Таким образом, при помощи дешифратора 11 и блока 12 возможен контроль любых значений входного параметра. Формула изобретения Устройство .умножения частоты гледэвания импульсов, содержахцее входной и в.:лходной формирователи импульсов, счетчик импульсов первый вход которого соединен с первым выходом блока управления, делитель частоты, запоминающий регистр и триггер, первый вход которого соединен со вторым выходом блока управления, отличающееся тем,.что, с целью повышения точности умножения, в него введены кодирующий блок, дешифратор,блок контроля и элементы И, выход первого из которых соединен со входом блока управления, а первый вход - с первым выходом триггера, второй вход которого соединен с выходом входного формирователя импульсов, а второй выходс первым входом второго элемента И, второй вход которого объединен со

вторым входом первого элемента И и подключен к шине опорной частоты, а выход - к счетному входу счетчика импульсов/ выход которого соединен с первым входом кодирующего блока, второй вход которого соединен со вторым выходом блока управления, а выход - со входом запоминающего регистра, первый выход которого соединен со входом дешифратора, а второй выходс управляющем входом делителя частбты, счетный вход которого соединен

с выходом блока контроля, первый вход которого подключен к выходу дешифратора, второй вход - к шине эталонной частоты, а выход делителя частоты - ко входу выходного формирователя импульсов.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР

357668, кл. Н 03 К 5/01, 09.03.71,

2.Авторское свидетельство .СССР

№ 354646, кл. Н 03 К 5/00. 05.11.71.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения частоты следования периодических импульсов | 1981 |

|

SU1005285A2 |

| Устройство для умножения частоты следования периодических импульсов | 1975 |

|

SU544112A2 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Умножитель частоты | 1979 |

|

SU813728A1 |

| Цифровой умножитель частоты | 1979 |

|

SU788363A1 |

| Устройство для умножения частотыСлЕдОВАНия пЕРиОдичЕСКиХиМпульСОВ | 1979 |

|

SU824419A2 |

| Устройство для умножения частоты следования периодических импульсов | 1978 |

|

SU769720A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1012431A1 |

| ЧАСТОТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ ЕРМАКОВА-ФЕДОРОВА (ВАРИАНТЫ) | 2007 |

|

RU2362175C2 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

Авторы

Даты

1981-04-15—Публикация

1979-07-04—Подача