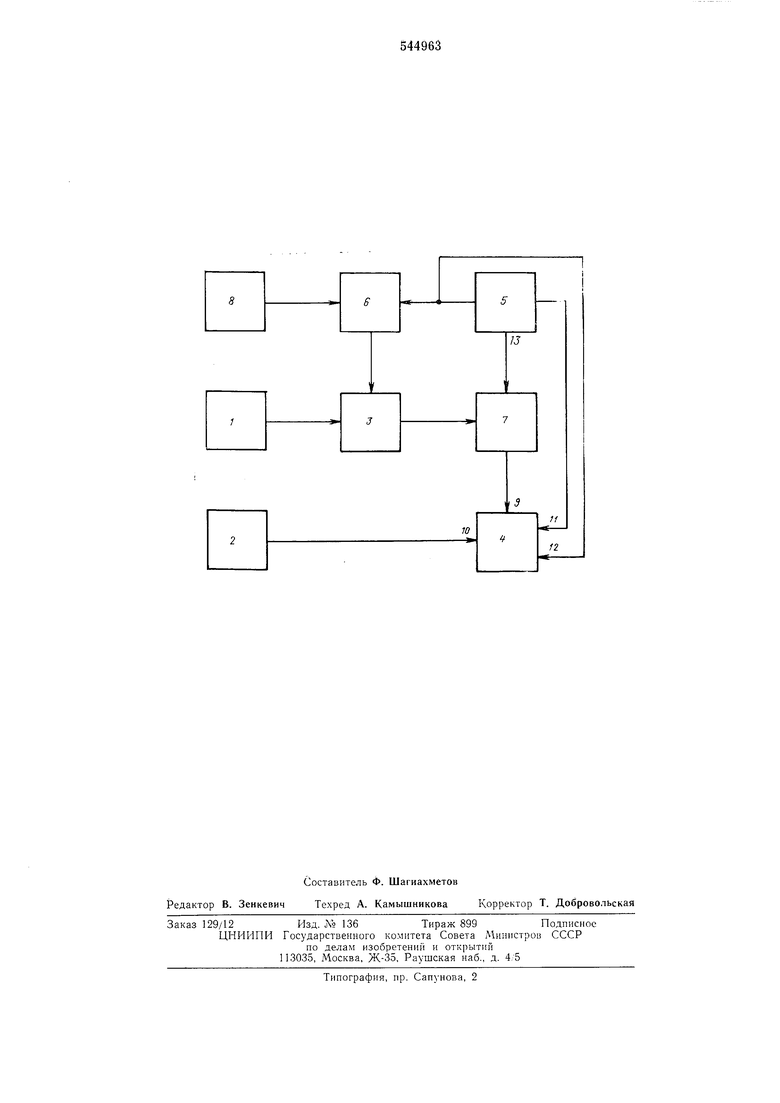

рый поступает па управляюо ий вход 12 сумматора-вычптателя 4 п переводит его в режпм соответствепно сложеппя плп вычптаппя, причем в режиме еложеппя знак результата равен знаку умепьп1аемого Л, что впдно из приведенных выраженнй (1): (+Л)+(5)(Л + 5) (-, А + (-В) - {А+В (+Л)-(-5) + (Л+5) (-А}-()-(А + В) В этом елучае блок управления 5 формирует сигнал, который с выхода 13 поступает па вход элемента И 7 и запрещает передачу знакового разряда вычптаемого В на вход 9 сумматора-вычптателя 4. Уменьшаемого Л пз регпстра 2 попадает на вход 10 еумматора-вычнтателя 4 последовательно со знаковым разрядом. Прп еложеппп знаковых разрядов уменьшаемого п вычнтаелюго в знаковом разряде суммы нолучается зпак, соответствующпй знаку умепьп.1аемого А. Прп сложенпп чнсел с разнымн знакамп плп вычитан1Н1 с одннаковымн блок управления 5 по входу 11 переводит сумматор-вычптатель 4 в режим вычнтаппя, причем знак результата определяетея как знаками онерапи модулями уменьшаемого н вычндов, так таемого, что видно из приведенных выраженнй (2): (-Л) + (+В) - (А-В} (+Л) + (-В) +--{А-Б) (-Л) - (-В) - {А-В} {+Л) - (+В) + (А-В Разность Л-В положительна, , или отрицательна, если |Л При перавенстве сигналом по выходу 13 блока управления 5 занреп;аетея передача знакового разряда вычптаемого нз регистра 1 через элемент И 7 на вход 9 сумматора-вычптателя 4. Уменьшаемое Л из регистра 2 поступает на вход 10 еумматора-вычптателя последовательно со знаковым разрядом. При вычитании нуля пз знакового разряда уменьшаемого па выходе сумматора-вычмтателя формируется знак результата, равный знаку меньшаемого в регистре 2. При неравенстве В енгпал пз блока управления поступает на вход 12 сумматора-вычитателя, переводя его в режим вычитания В-А, п на вход элемента И 6. В момент времепп, соответствуюпиш знаковому разряду, блок сппхроппзаиин 8 вырабатывает сигнал, ранный «I, который через элементы И 6, 7 п элемент НЛИ 3 поступает па вход 9 сумматора-вычнтателя в знаковол разряде вышггасмого В. Такнм образом, в сумматоре-вычптателе выполняется операция: - В -Л, а зпак результата оказывается положительным, еслн знак уменьшаемого Л от)ин,ателен, плп отрицательным, если знак умеиьшаемого Л положительный. Таким образом, изобретеиие иозволяет формировать знак результата суммирования при мепьшпх затратах оборудования, чем известиое устройство, за счет исключения двух элементов «Запрет н введения новых связей. Формула и 3 о б р е т е и и я Уетройетво для формирования знака результата иоразрядиого сложения, содержащее одноразрядный еумматор-вычптатель, блок управления, блок синхронизации, иервый и второй регистры сдвига, первый и второй элементы И, элемент ИЛИ, нрнчем первый и вто)ой входы иервого элемента И п первый управляющий вход одпоразрядпого сумматора-вычитателя соедпнеиы соответствеппо с выходом блока спихронпзацпи, с первым н вторым выходами блока уиравления, отличаюHt е е с я тем, что, с целью сокрап1ения оборудования, выход первого элe.мeJГla П и первого рсгиетра едвига через элсмеит ИЛИ еоединен с нервым входом второго элемента И, второй вход и выход которого соединепы соответствеиио с третьим выходом блока уиравления и с иервым кодовым входом одноразрядного сумматора-вычьтателя, вто)ые кодовый н управляюии1Й входы которого соедипеиы соответствеппо е выходом второго регистра сдвига II с иервым выходом блока управления. Источиики информации, принятые во BHiiманне при экспертизе: 1.Соловьев Г. И. Арифметическое устройство вычислпте.чыюй машииг г «Вычислительная техника, Сборннк статей. Госатомиздат, М., 1960, с. 18, рис. 4. 2.Электроииая клавпишая вычислительная мапл1иа. «11екра-11 IT. Техиическое описание. Щб 3.021.001.70, стр. 28 (прототнн).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразованияфуРьЕ | 1978 |

|

SU794637A1 |

| Устройство для вычитания двоичнодесятичных кодов времени | 1976 |

|

SU595730A1 |

| Устройство для вычисления элементарных функций | 1975 |

|

SU553612A1 |

| Устройство для решения систем ли-НЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU811274A1 |

| Арифметическое устройство | 1974 |

|

SU526891A1 |

| Устройство для сложения десятичных чисел | 1975 |

|

SU595729A1 |

| Цифровой функциональный преобразователь | 1975 |

|

SU599265A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Устройство для вычисления гиперболических функций | 1980 |

|

SU957208A1 |

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

Авторы

Даты

1977-01-30—Публикация

1974-06-03—Подача