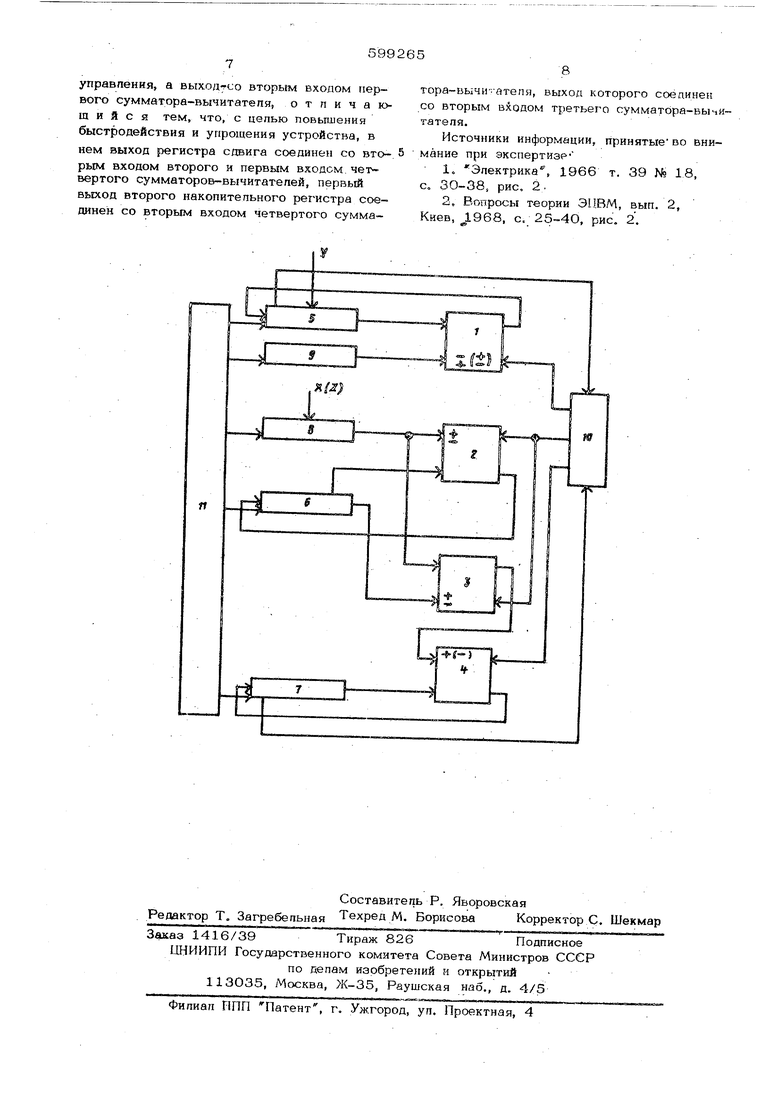

(54) ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ дом четвертого сумматора-вычитатепя, вы-ход которого соецинен со вторым входом третьего сумматора-выЧйтатёля, На чертеже изображена бпок схема цифрового функционального преобразователя.. Цифровой функционапьный преобраэоватеп состоит из одноразрядных сумматоров-вычитатепей 1.4 комбинационного типа, накопительных регистров , регистра 8 сдвига, блока 9 формирования констант, дискримина тора 10 знака и блока 11 управпения. Выходы сумматоров-вычитатепей 1,2 и 4 сое динены с инфо{)мационными входами накопите пьных регистров S-7 соответственно, а выходы последних соединены с первыми входами указанных сумматоров-вычитатепей Второй выход наконитепьного регистра 6 соединен со вторым входом сумматора-выЧитатепя 3, выход которого соединен со вторым входом сумматора-вычитателя; Т4. Выход регистра 8 сдвига соединен с первы входом сумматора-вычитатепя 3 и вторым входом сумматора-вычитатепя 2. Выход бло 9формирования констант соединен с входом сумматора-вычитатепя 1. Вторые (знаковые} выходы накопительных регистров 5 и 7 соединены с входами дискриминатора 10знака. Первый выход последнего соединен с .управляющим входом сумматора-вычи тателя 1, второй выход - с управляющими входами сумматоров-вычитатепей 2 и 3, третий выход - с управляющим входом сум матора-вычитателя 4. Входьг накопительных регистров 5-7, регистра 8 сдвига и бпока 9 соедине ны с выходами блока 11 управле ния. БлокЭ формирования констант выполнен, например, в виде одностороннего запом .нающего устройства или регистра сдвига. Он генерирует на выходе константы вида 2 где I - комер итерации. Первый выход накопительного регистра 6 выполнен от вы хода предпоследнего разряда регистра. Дискриминатор 1О знака состоит из логических элементов и триггера. Блок 11 управления состоит из генератора тактовых импульсов, счетчика, распределителя и ло гических элементов. Входами устройства являются : вход,накопительного регистра 5 для аргумента Y, вход регистра 8 сдаига для аргумента X в первом цикле вьг-1исления и для аргумента Z во втором цикле вычисления. Выходом устройства является выход накопительного регистра 5. Цифровой функциональный преобразоватепь работает следующим образом. Первоначально регистры 5-8 и блок 9 устанавливаются в нулевое состояние. В первом цикле вычиспения в накопительный регистр 5 в параллельном двоичном коде подается значение аргумента Y, в регистр сдвига - значение аргумента X. Каждый икл вычисления состоит из Л итераций, де Й число разрядов аргумента. Ячейки, остоящие из накопительных регистров 5,6 7 и сумматоров-йычитагелей 1,2 и 3:4, каждой итерации работают параллельно . Разностно-итерационный алгоритм, реалиуемый в предложенном устройстве, осноан на представлении любого двоичного чиса -в виде ряда: .. , где 1 зависит от процесса лежения за приближением .определенной веичины к заданному аргументу. В первом цикле Бычиспения производитя приближение вепичи ны|У к заданному ргументу У, т.ео вьтолняется решение уравения , а затем вычисляются ункции следующей системе рекуррентых соотношений: - JMUj-q, 1-1 при .l-2 - j-X2- J)5 V - XY2f 4Q ,.j . . Bo втором цикле вычисления производится приближение квадрата величинь и.,умноженное на третий аргумент Е,к величине ХУ , полученной в первом цикле вычисления, т.е. выполняется решение управления ХУ . О по следующей системе рекуррентных соотношений: UO-Q Uj.i Uj-q.,-4, Vj,2Uj,...,.-2a..x Wj,L XY2-2. cOj-(jVj-22 2J)5 . Г 1приШ1 0 V ir j l-l pHbUj 0 . Таким образом, в конце второго цикла вычислений получается требуемая функция. Структура алгоритмов первого и второго циклов одинакова, за исключением начальных условий и знаков в первом и третьем соотношениях. Первое рекуррентное соотношение алгоритма реализуется в накопительном регистре 5, сумматоре-вычитателе 1 .и блоке 9 формирования констант. Второе соотношение реализуется в накопительных регистрах 6,8 и сумматоре-вычитателе 2. Третье соотношеыие реализуется в накопительном рег-кстре и сумматорах-вычнтателях 3 и 4. Величина jt определяется в аискрими 1аторе 10 по знаку накопительного регистра 5 дпя первого цикпа вычиспения ипи по знаку накопитепьного регистра 7 дпя второго цикпа вычиспения. Каждое соотношение вычиспяется поспедоватепьно за тактов.,где m |tOEr,mlчиспо дополнитепьных защитных разрядов регистров дпя компенсации погрешности усе чения чисеп при сдвиге. В пюбой ите рации с выходов блока 11 управления выда ется серия тактовых импульсов, которые сд гают содержимое регистров 5-8, подавая информацию на входы сумматоров-вычитате пей i-4. Результаты алгебраического суммирования ь каждой итерации с выходоз сумматоров-вычитатепей 1,2 и 4 записываются мпадшими разрядами вперед в освооождаюпшеся при сдвиге старипю разряды накопительных регистров 5-7 соответственно и продвигаются к начапу этих, регистров Очередная константа вида ) с выхода блока 9 формирования констант подается на сумматор-вычитатепь 1, где поразрядно суммируется ипи вычитается с содержимым регистра 5. Величина Х2 выхода регистра. 8 поразрядно суммируется (при CJ. | 1) или вычитается (при i. 1) сумматоре--вычитатепе 2 с пог ооинным значением содержимого накопитепьного регистра 6. Попное значение содержимого .Vj регистра 6 суммируется ипи вычитается с содержимым регистра 8 в сумматоре-вычитатепе 3 Зтст результат суммируется с содержимым { UJj ) накопитепыгого регистра 7 в сум маторе-вычитатепе 4. Значение знакового разряда накопительного регистра 5 передается з дискриминатор 1О, с первого и второго выходов которого выдается очередное значение величины . При попожитепьном значении содержимого регистра 5 ; -f 1, при отрицательном значении С третьего выхода дискриминатора 10 выдается сигнал, определяющий сложение по второму входу сумматора-вычитателя 4. После выполнения TL итераций цикпа в регистре 5 устанавливается нулевое значение (в пределах разрядной сетки)j в регист ре 6 произведение двух аргументов, сдвинутое на П+1 разрядов, в регистре 7произведение первого аргумента на квадрат второго, т. е. значение ХУ , Во втором цикле вычисления первоначапьио в регистрах 5,6 и 8 устанавпиваюгся нулевые значения, содержимое регистра . 7 сохраняется прежним. В регистр 8 сдви га заносится двоичный код значен11ятретье го )1та 1 . Процессы вычиспения в riepBLM и втором циклах одинаковы, за ИСКЛКУчением изменения знаков величин Q,i , управляющих режимом (слолчеиие-вычитг.шие) в сумматоре-вычитатепе 1. С первого выхода дискриминатора 10 выдается отрицание значения величины CJ.: , с второго значение величины t.;, , с третьего - сигнал, определяющий вычитание по р}торому входу сумметора-вычитателя 4. Значение вепичины Cj, определяется по знаку содержимого накопительного регистра 7. После выполнения п итераций в накопительном регистре 5 устанавливается значение искомой функции ./E , в накопительном регистре 6 - значёЖё функции (сдвинутое на Т1+1 разрядов), в накои гтельном регистре 7 - нулевое значение. Время вычисления указанных функций равно в тактах Т 2.Ts -i-2n(Tn+-i)f2TTi,что значительно меньше вычисления традиционными средствами. Параллельно-последовательная структура предложенного цифрового функционального преобрайовате/хя обладает простотой схемных решений из стандартных цифровых элементов и относительно высокой однородностью и регулярностью, что позволяет, используя возможности современной интегральной технологии, изготовить это.в виде одной интегральной схемы. Формула изобретения Оифровой функциональный преобразователь, содержаиаий блок управления, три накопительиых регистра, первые входы которых соединены с первым, вторым и третьим выходами блока управления соответственно, регистр сдвига, вход которого соединен с четвертым выходом блока управления, четьфе сумматора - вычитателя, дискриминатор знака, выходы которого соединены с управляющимся входами сумматоров-вычитателей, выходы первого, второго и третьего сумматоров- ычнтателей соединены со вторыми входами соответствующих накопительных регистров, первые выходы первоI-O и третьего накопительных регистров соединены с первыми входами соответствующих- сумматоров-вычитателей, а вторые выходы этих накопительных регистров соединены с первым и вторым входами дискриминатора знака соответственно, второй выход второго 1шкоггительного регистра соегагнен с первым входом второго сумматора-вы- читателя, бпок формирования констант, Bxn;i к.отопого соединен с пятым выходом блока

7

управления, а выход со вторым входом первого сумматора-вычитатепя, о т п и ч а юШ и и с я тем, что, с цепью повышения быстродействия и упрощения устройства, в нем выход регистра сдвига соединен со вторым входом второго и первым входом четвертого сумматоров-вычитатепей, первый выход второго накопитепьного регистра соединен со вторым входом четвертого сумма8

тора вычи-.-атепя, выход которого соединен со вторым входом третьего сумматора-вычитателя.

Источники информации, принятыево внимание при экспертизе1.Электрика, 1966 т. 39 № 18, с, 30-38, рис. 2.

2,Вопросы теории ЭЦВМ, вып. 2, Киев, JL968, с. 25-4О, рис. 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Устройство для вычисления корня -ой степени | 1977 |

|

SU742929A1 |

| Устройство для вычисления гиперболического тангенса | 1973 |

|

SU526890A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Устройство для вычисления кубического корня | 1973 |

|

SU516037A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1973 |

|

SU536490A1 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Двоичное устройство деления | 1974 |

|

SU497585A1 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

Авторы

Даты

1978-03-25—Публикация

1975-07-08—Подача