граммное прерывание соединены с соответствующими управляющими входами и выходами устройства.

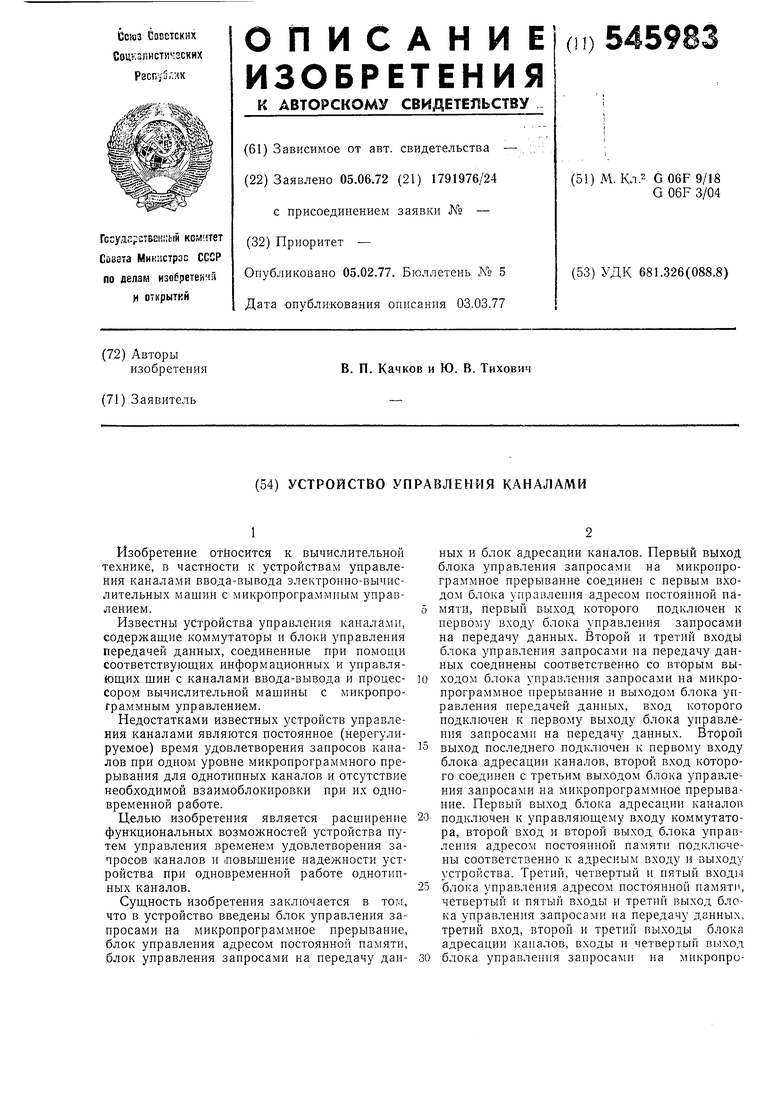

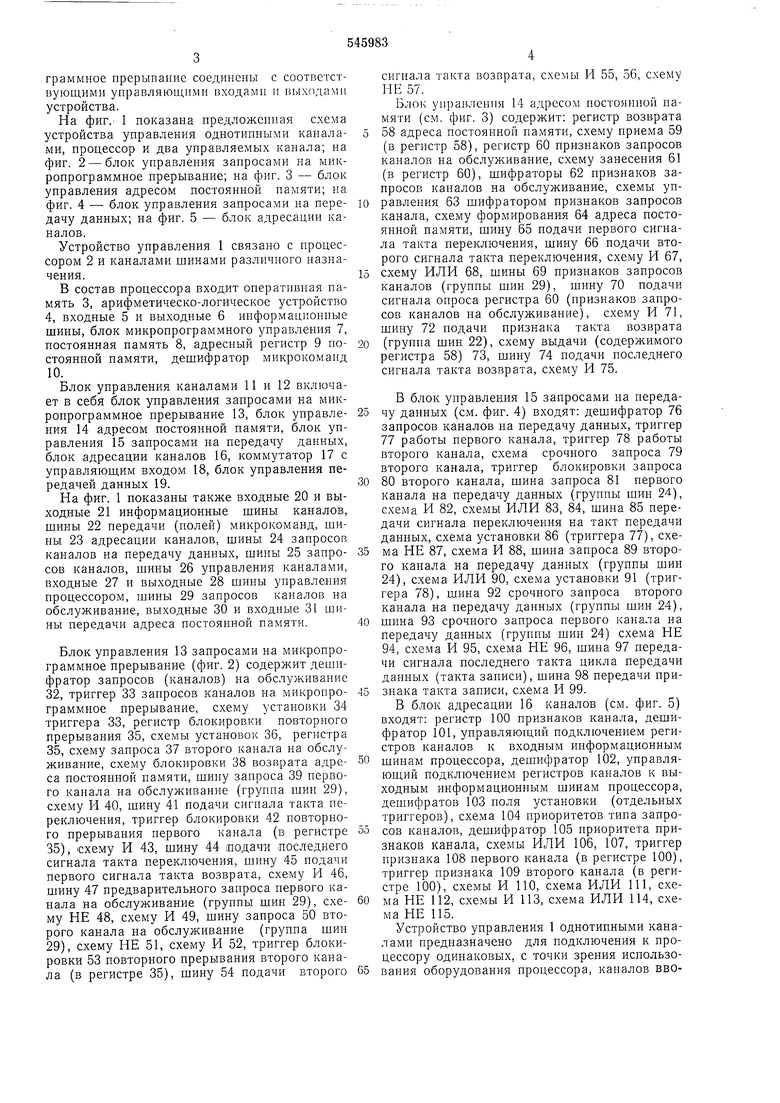

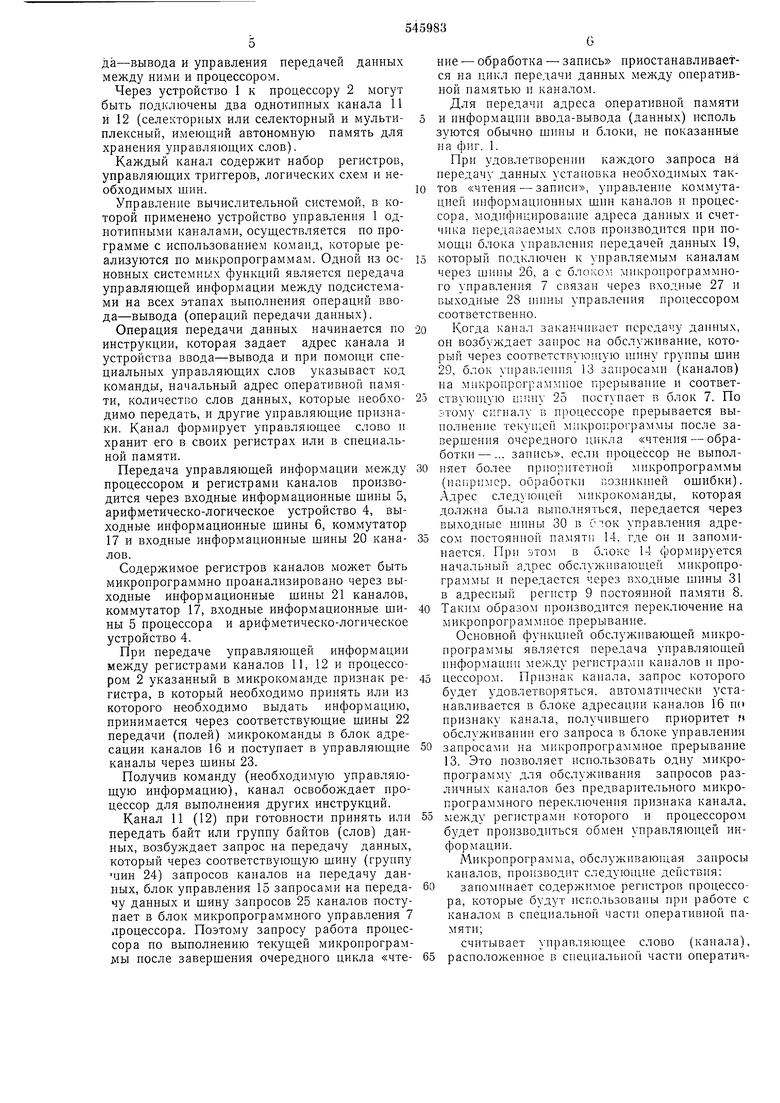

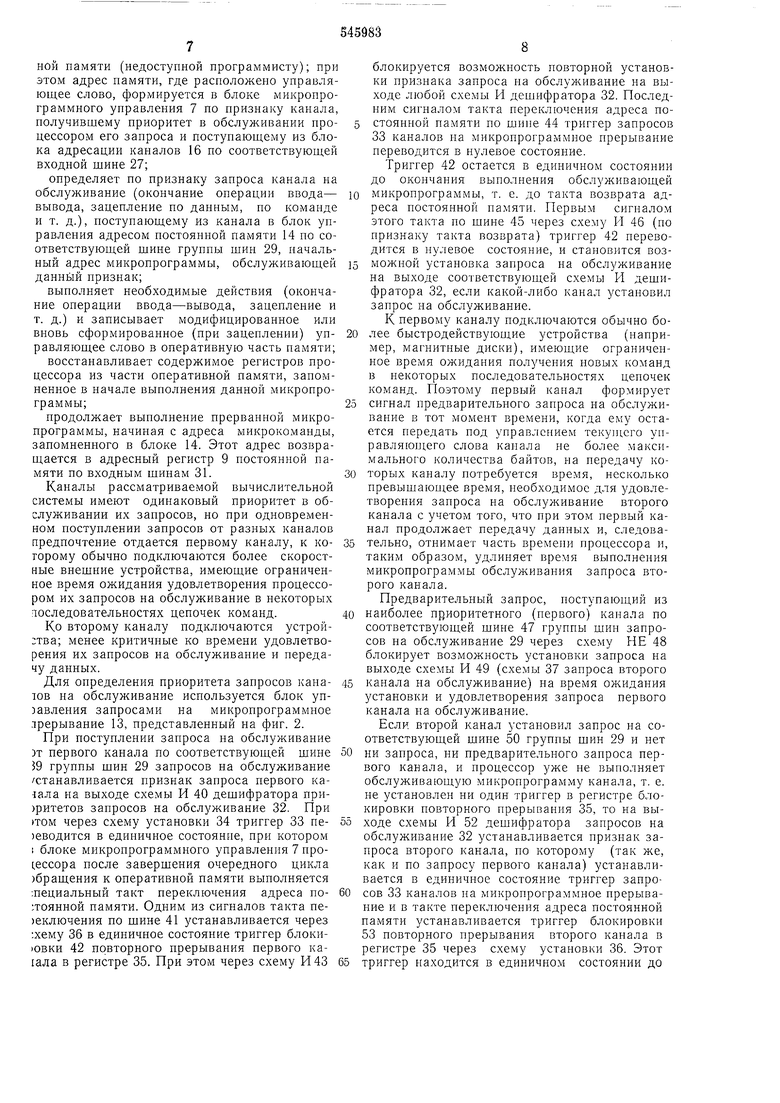

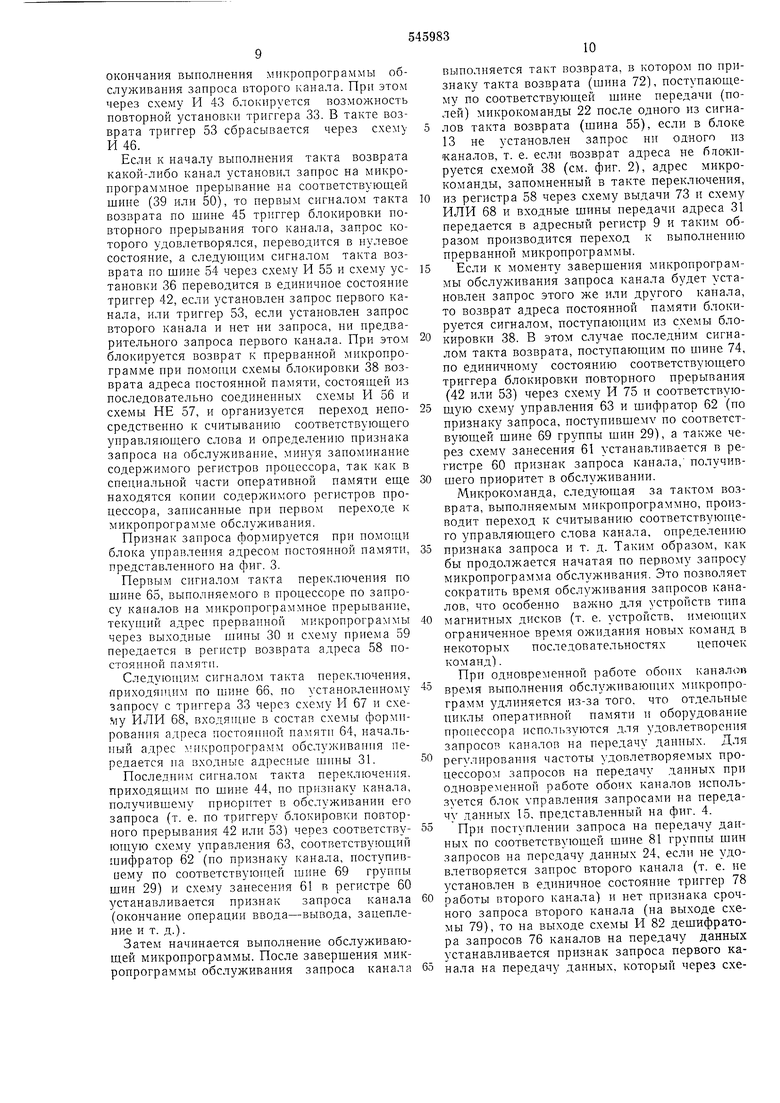

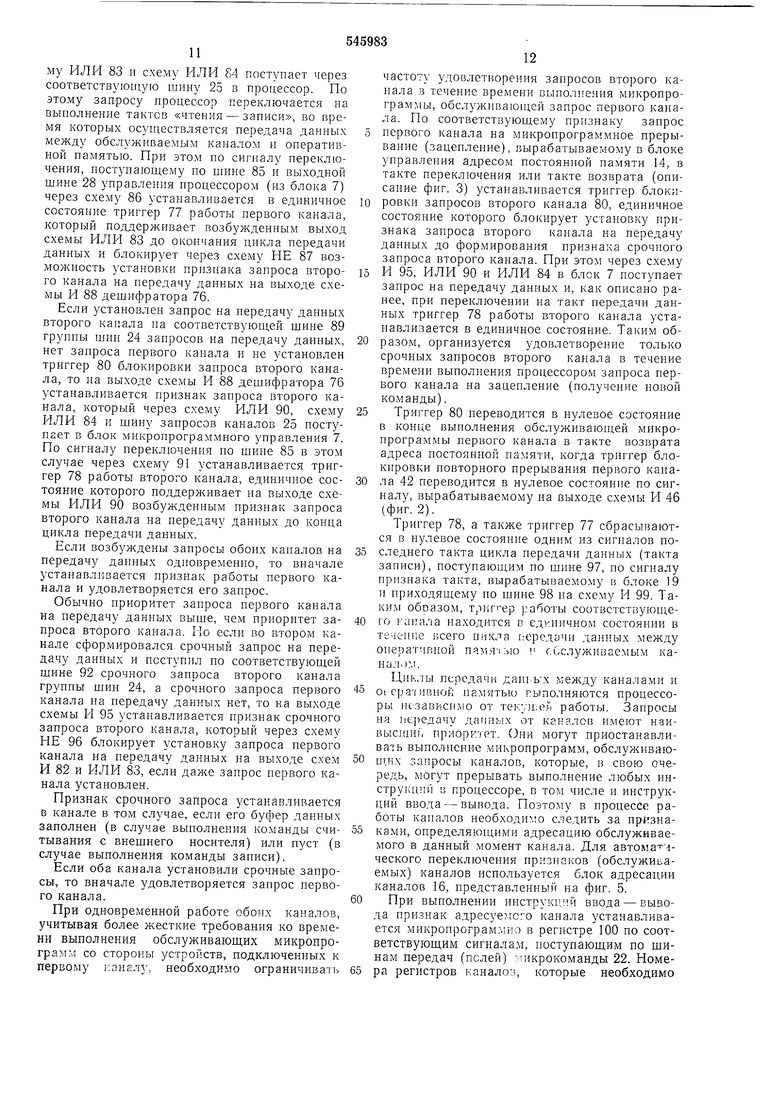

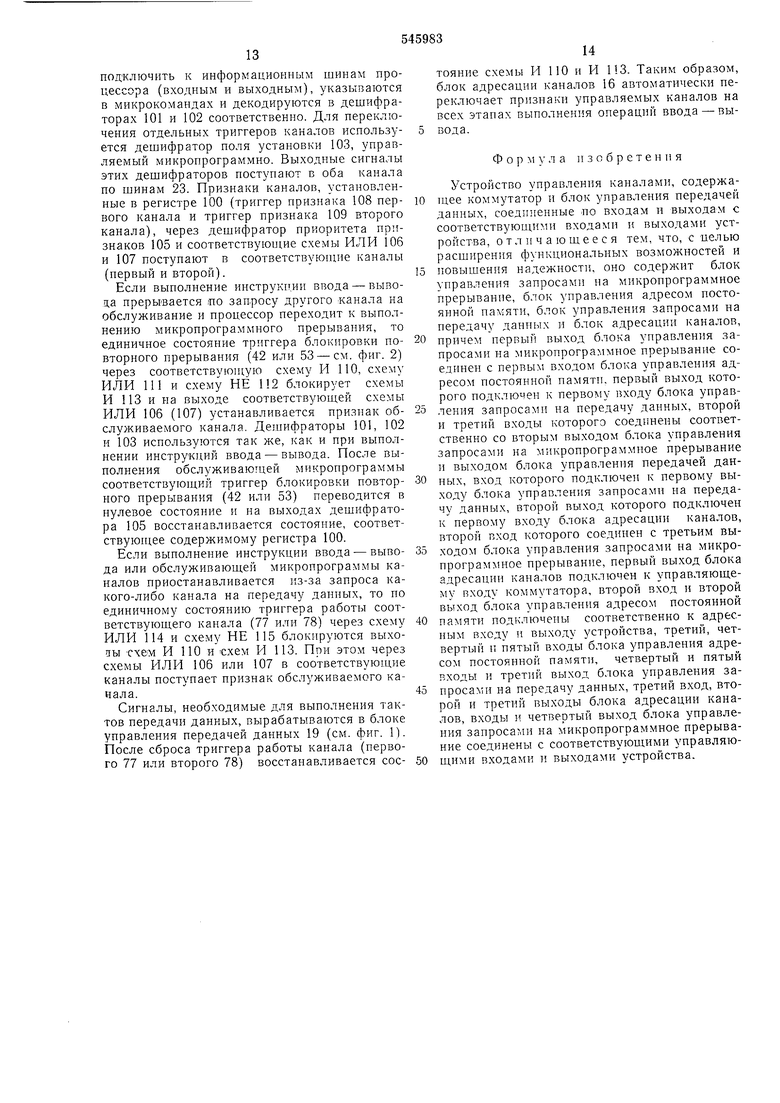

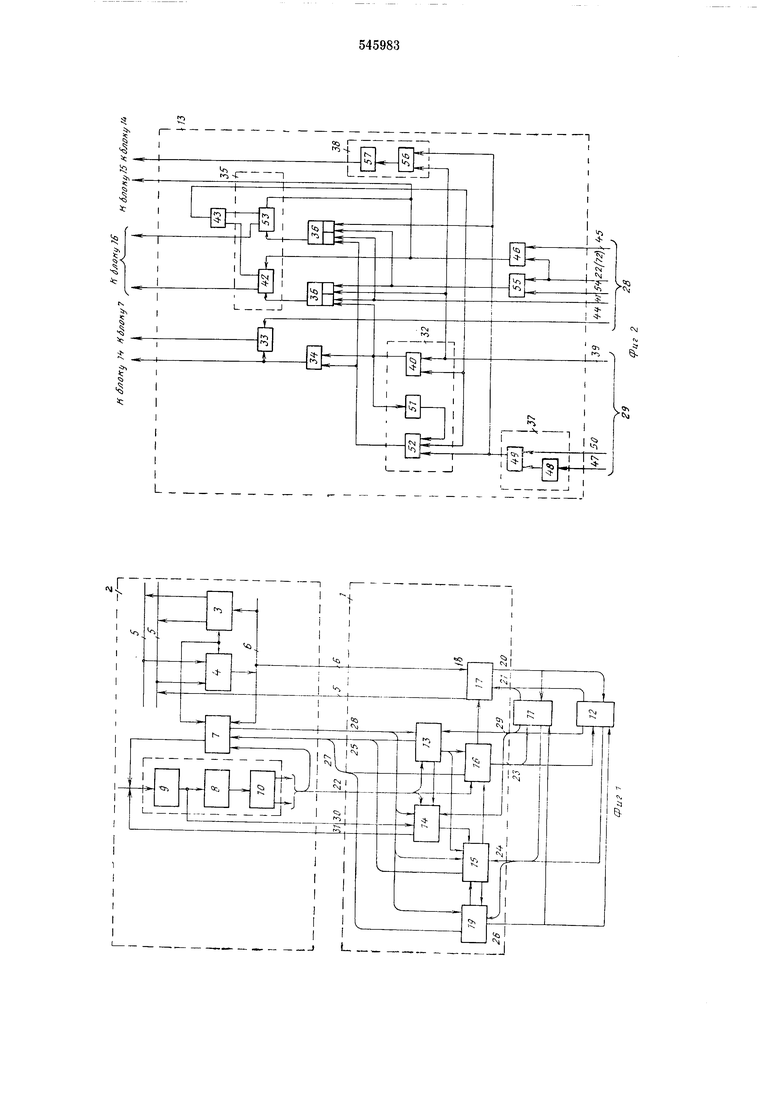

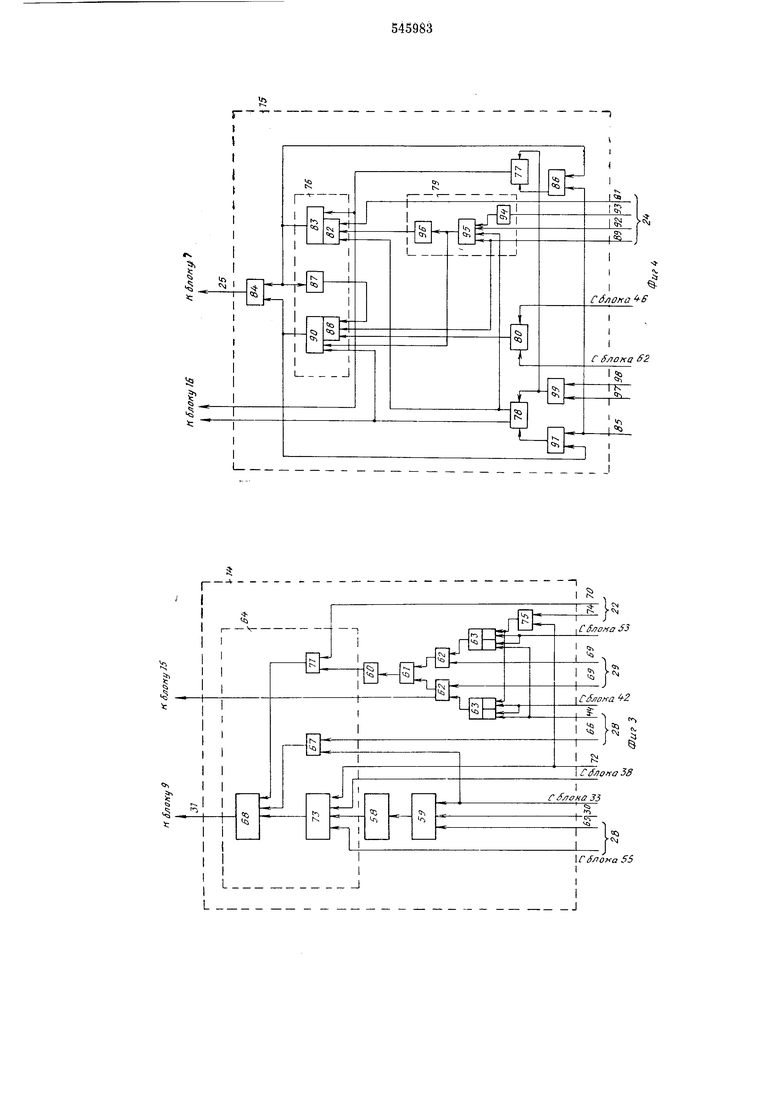

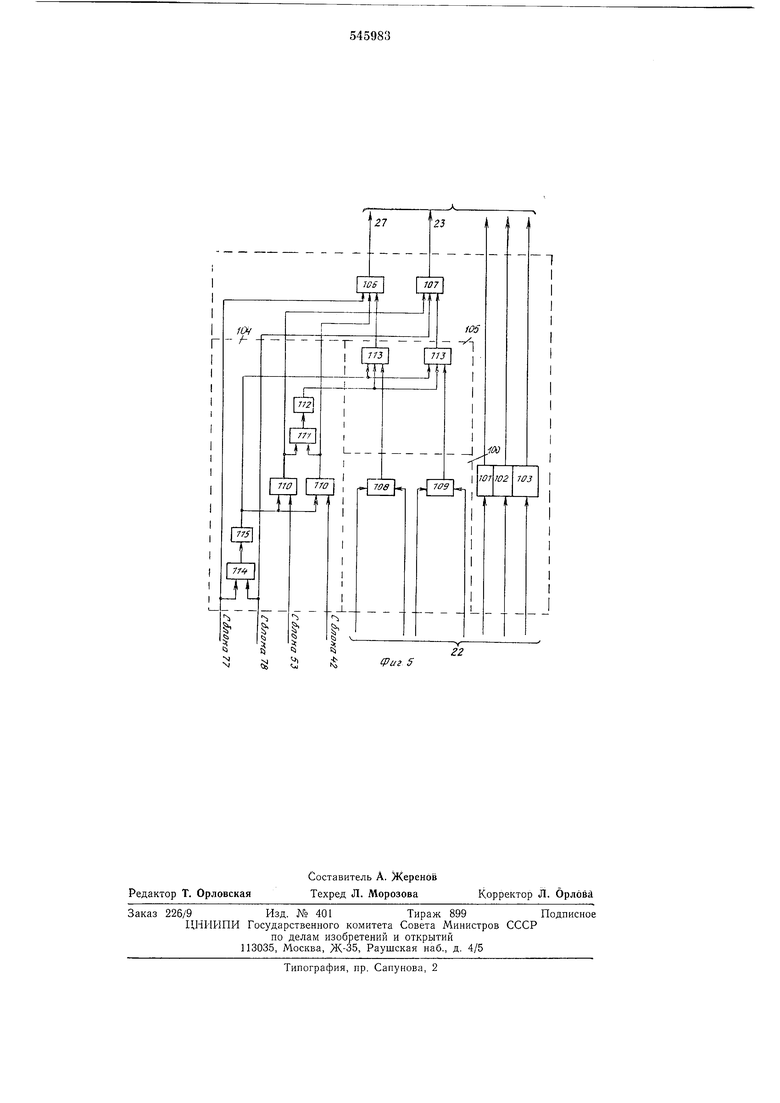

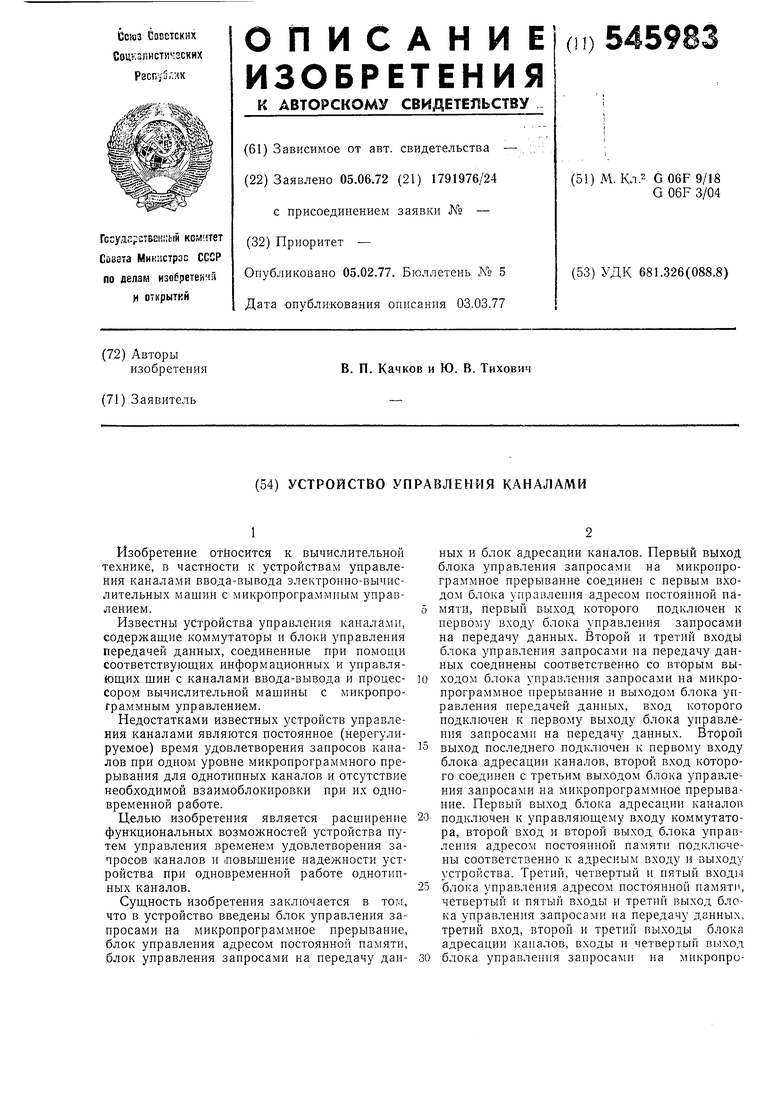

На фиг. 1 показана предложеииая схема устройства управления однотипными каналами, процессор и два управляемых канала; иа фиг. 2 - блок управления запросами на микропрограммное прерывание; на фиг. 3 - блок управления адресом постоянной памяти; на фиг. 4 - блок управления запросами на передачу данных; на фнг. 5 - блок адресации каналов.

Устройство управления 1 связано с процессором 2 и каналами шинами различного назначения.

В состав процессора входит оперативная память 3, арифметнческо-логнческое устройство 4, входные 5 и выходные 6 информационные шины, блок микропрограммного управления 7, постоянная память 8, адресный регистр 9 постоянной памяти, дешифратор микрокоманд 10.

Блок управления каналами 11 и 12 включает в себя блок управления запросами на микропрограммное прерывание 13, блок управления 14 адресом постоянной памяти, блок управления 15 запросами па передачу данных, блок адресации каналов 16, коммутатор 17 с управляющим входом 18, блок управления передачей данных 19.

На фиг. 1 показаны также входные 20 и выходные 21 информационные щины каналов, шины 22 передачи (полей) микрокоманд, щины 23 адресации каналов, шины 24 заиросоп каналов на передачу данных, шины 25 запросов каналов, щины 26 управления каналами, входные 27 и выходные 28 щины управления процессором, шины 29 запросов каналов на обслуживание, выходные 30 и входные 31 шины передачи адреса постоянной памяти.

Блок управления 13 запросами на микропрограммное прерывание (фиг. 2) содержит дещифратор запросов (каналов) на обслуживание 32, триггер 33 запросов каналов на микропрограммное прерывание, схему установки 34 триггера 33, регистр блокировки повторного прерывания 35, схемы установок 36, регистра 35, схему запроса 37 второго канала на обслуживание, схему блокировки 38 возврата адреса постоянной памяти, шииу запроса 39 первого канала на обслуживание (группа щин 29), схему И 40, щину 41 подачи сигнала такта переключения, триггер блокировки 42 повторного прерывания первого канала (в регистре 35), схему И 43, щину 44 шодачИ последнего сигнала такта переключения, шину 45 подачи первого сигнала такта возврата, схему И 46, шину 47 предварительного запроса первого канала на обслуживание (группы шин 29), схему НЕ 48, схему И 49, шину запроса 50 второго канала на обслуживание (группа шин 29), схему НЕ 51, схему И 52, триггер блокировки 53 повторного прерывания второго канала (в регистре 35), шину 54 подачи второго

сигнала такта возврата, схемы И 55, 56, схему НЕ 57.

Блок управления 14 адресом постоянной памяти (см. фиг. 3) содержит: регистр возврата 5 58 адреса постоянной памяти, схему приема 59 (в регистр 58), регистр 60 признаков запросов каналов на обслуживание, схему занесения 61 (в регистр 60), шифраторы 62 признаков запросов каналов на обслуживание, схемы управления 63 шифратором признаков запросов канала, схему формирования 64 адреса постоянной памяти, шину 65 подачи первого сигнала такта переключения, щину 66 подачи второго сигнала такта переключения, схему И 67,

15 схему ИЛИ 68, шины 69 признаков запросов каналов (группы шин 29), щину 70 подачи сигнала опроса регистра 60 (признаков запросов каналов на обслуживание), схему И 71, щину 72 подачи признака такта возврата

0 (группа щин 22), схему выдачи (содержимого регистра 58) 73, щину 74 подачи последнего сигнала такта возврата, схему И 75.

В блок управления 15 запросами на передачу данных (см. фиг. 4) входят: дещифратор 76 запросов каналов на передачу данных, триггер 77 работы первого канала, триггер 78 работы второго канала, схема срочного запроса 79 второго канала, триггер блокировки запроса

0 80 второго канала, щина запроса 81 первого канала на передачу данных (группы щин 24), схема И 82, схемы ИЛИ 83, 84, щина 85 передачи сигнала переключения на такт передачи данных, схема установки 86 (триггера 77), схема НЕ 87, схема И 88, щина запроса 89 второго канала на передачу данных (группы щин 24), схема ИЛИ 90, схема установки 91 (триггера 78), щина 92 срочного запроса второго канала на передачу данных (группы шин 24),

0 шина 93 срочного запроса первого канала на передачу данных (группы шин 24) схема НЕ 94, схема И 95, схема НЕ 96, шина 97 передачи сигнала последнего такта цикла передачи данных (такта записи), щина 98 передачи при5 знака такта записи, схема И 99.

В блок адресации 16 каналов (см. фиг. 5) входят: регистр 100 признаков канала, дешифратор 101, управляющий подключением регистров каналов к входным информационным

0 щинам процессора, дешифратор 102, управляющий подключением регистров каналов к выходным информационным щинам процессора, дешифратов 103 поля установки (отдельных триггеров), схема 104 приоритетов типа запросов каналов, дещифратор 105 приоритета признаков канала, схемы ИЛИ 106, 107, триггер признака 108 первого канала (в регистре 100), триггер признака 109 второго канала (в регистре 100), схемы И 110, схема ИЛИ 111, схема НЕ 112, схемы И 113, схема ИЛИ 114, схема НЕ 115.

Устройство управления 1 однотипными каналами предназначено для подключения к процессору одинаковых, с точки зрения использования оборудования процессора, каналов ввода-вывода и управления передачей данных между ними и процессором.

Через устройство 1 к процессору 2 могут быть подключены два однотипных канала И и 12 (селекторных или селекторный и мультиплексный, имеющий автономную память для хранения управляющих слов).

Каждый канал содержит набор регистров, управляющих триггеров, логических схем и необходимых шин.

Управление вычислительной системой, в которой применено устройство управления 1 однотипными каналами, осуществляется по программе с использовапием команд, которые реализуются по микропрограммам. Одной из основных системных функций является передача управляющей информации между подсистемами на всех этапах выполпения операций ввода-вывода (онераций передачи данных).

Операция передачи даппых начинается по инструкции, которая задает адрес канала и устройства ввода-вывода и при помощи специальных управляющих слов указывает код команды, начальный адрес оперативной памяти, количество слов данных, которые необходимо передать, и другие управляющие признаки. Капал формирует управляющее слово и хранит его в своих регистрах или в специальной памяти.

Передача управляющей информации между процессором и регистрами каналов производится через входные информационные шины 5, арифметическо-логическое устройство 4, выходные информационные шипы 6, коммутатор 17 и входные информационные щины 20 каналов.

Содержимое регистров каналов может быть микропрограммно проанализировано через выходные информационные щины 21 каналов, коммутатор 17, входные информационные шины 5 процессора и арифметическо-логическое устройство 4.

При передаче управляющей информации между регистрами каналов 11, 12 и процессором 2 указанный в микрокоманде признак регистра, в который необходимо принять или из которого необходимо выдать информацию, принимается через соответствующие щины 22 передачи (полей) микрокоманды в блок адресации каналов 16 и поступает в управляющие каналы через шипы 23.

Получив команду (необходимую управляющую информацию), канал освобождает процессор для выполнения других инструкций.

Канал 11 (12) при готовности принять или передать байт или группу байтов (слов) данных, возбуждает запрос на передачу данных, который через соответствующую щину (группу иин 24) запросов каналов на передачу данных, блок управлепия 15 запросами на передачу данных и шину запросов 25 каналов поступает в блок микропрограммного управления 7 процессора. Поэтому запросу работа процессора по выполнению текущей микропрограммы после завершения очередного цикла «чтение - обработка - запись нриостанавливается на цикл передачи данных между оперативной памятью п каналом.

Для передачи адреса оперативной памяти и информации ввода-вывода (данных) псполь зуются обычно щины и блоки, не показанные на фиг. 1.

При удовлетворении каждого запроса на передачу данных установка необходимых тактов «чтения - записи, управление коммутацией информационных шин каналов и процессора, модифицирование адреса данных и счетчика нере;1,а15аемых слов производится при помощи блока управления передачей данных 19,

который подключен к управляемым каналам через шины 26, а с блокол; микропрограммного управления 7 связан через входные 27 и выходные 28 нщны управления процессором соответственно.

Когда канал заканчивает передачу данных, он возбуждает запрос на обслуживание, который через соответствующую шину группы шин 29, блок упраилепня 13 запросамп (каналов) на микропрограммное прерывание п соответствуюн1ую шину 25 поступает в блок 7. По тому сигналу в процессоре прерывается выполнение текущей микропрограммы после заверщення очередного цикла «чтения - обработки - ... запись, есл)1 процессор не выполняет более приоритетной микропрограммы (например, обработки возникшей ощибки). Адрес след ЮП1ей микрокоманды, которая должна была выполняться, передается через выходпые шины 30 в елок управления адреCON ПОСТОЯННО 14. где он и запоминается. этом в блоке 14 формируется начальный адрес обслужпва ощей микропрограммы и передается через входные шнны 31 в адресный 9 постоянной памяти 8.

oбpaзo производится переключение на л икропрограмм ое прерыван е.

Основной функцпей обслужпвающей микропрограммы является передача управля ощей ппформации eждy регистрах капалов п процессором. Пр 1знак капала, запрос которого будет удовлетворяться. автомат 1ческп устанавливается в блоке адресации каналов 16 ио признаку канала, нолучпвшего приоритет г обслуживап 1И его запроса в блоке управления

запросами на микропрограммное прерывапие 13. Это позволяет спользовать одпу микропрограмму для обслуживания запросов различных каналов без предварительного микропрограммного переключения признака канала,

регистрами которого и процессором будет производиться обмен управляю1цей ннформации.

Микропрограл ма, обслуж ваю лая запросы капалов, про 1звод т следу 0 цпе действия:

запоминает содержимое регистров процессора, которые будут пспользовапы прп работе с каналом в специальной част оперативной памяти;считывает управля 0 цее слово (канала),

расположенное в с ец альной части оперативной памяти (недоступной программисту); при этом адрес памяти, где расположено управляющее слово, формируется в блоке микропрограммного управления 7 по признаку канала получившему приоритет в обслуживании процессором его запроса и поступающему из блока адресации каналов 16 по соответствующей входной щине 27; определяет по признаку запроса канала на обслуживание (окончание операции ввода- вывода, зацепление по данным, по комапде и т. д.), поступающему из канала в блок управления адресом постоянной памяти 14 по соответствующей шине группы шип 29, начальный адрес микропрограммы, обслуживающей данный признак; выполняет необходимые действия (окончание операции ввода-вывода, зацепление и т. д.) и записывает модифицированное или виовь сформированное (при зацеплении) управляющее слово в оперативную часть памяти; восстанавливает содержимое регистров процессора из части оперативной памяти, запомненное в начале выполнения данной микропрограммы;продолжает выполнение прерваппой микропрограммы, начиная с адреса микрокоманды, запомненного в блоке 14. Этот адрес возвращается в адресный регистр 9 ностоянной памяти по входным шинам 31. Каналы рассматриваемой вычислительной системы имеют одинаковый приоритет в обслуживании их запросов, но при одновременном поступлении запросов от разных каналов предпочтение отдается первому каналу, к когорому обычно подключаются более скоростные внешние устройства, имеющие ограниченное время ожидания удовлетворения нроцессором их запросов на обслуживание в некоторых последовательностях цепочек команд. Ко второму каналу подключаются устрой;тва; менее критичные ко времени удовлетворения их запросов на обслуживание и передачу данных. Для определения приоритета запросов каыа10В на обслуживание используется блок упзавления запросами на микропрограммное лрерывание 13, представленный на фиг. 2. При поступлении запроса на обслуживание )т первого канала по соответствующей шине 59 группы шин 29 запросов на обслуживание останавливается признак запроса первого канала на выходе схемы И 40 дешифратора при)ритетов запросов на обслуживание 32. При том через схему установки 34 триггер 33 ие)еводится в единичное состоянпе, при котором I блоке микропрограммного уиравления 7 нро|,ессора после завершения очередного цикла )бращения к оперативной памяти выполняется лециальный такт переключения адреса по;тоянной памяти. Одним из сигналов такта пе)еключения по шине 41 устанавливается через ;хему 36 в единичное состояние триггер блокиювки 42 повторного прерывания первого кагала в регистре 35. При этом через схему И 43 блокируется возможность повторной установки признака запроса на обслуживание на выходе любой схемы И дешифратора 32. Последннм сигналом такта переключения адреса постоянной памяти по шине 44 триггер запросов 33 каналов на микронрограммное прерывание переводится в нулевое состояние. Триггер 42 остается в единичном состоянии до окончания выполнения обслуживающей микропрограммы, т. е. до такта возврата адреса постоянной памяти. Первым сигналом этого такта по шине 45 через схему П 46 (по признаку такта возврата) триггер 42 переводится в нулевое состояние, и становится возможной установка запроса на обслуживание на выходе соответствующей схемы И дешифратора 32, если какой-либо канал установил занрос на обслуживание. К первому каналу нодключаются обычно более быстродействующие устройства (например, магнитные диски), имеющие ограниченное время ожидания получения новых команд в некоторых последовательностях ценочек команд. Поэтому первый канал формирует сигнал предварительного запроса на обслуживание в тот момент времени, когда ему остается передать нод управлением текуп1его управляющего слова каиала не более максимального количества байтов, на нередачу которых каналу потребуется время, несколько превышаюп1ее время, необходимое для удовлетворения запроса на обслуживание второго канала с учетом того, что при этом первый канал продолжает передачу данных и, следовательно, отнимает часть времени процессора и, таким образом, удлиняет время выполнения микропрограммы обслуживания запроса второго канала. Предварительный запрос, ноступаюший из наиболее приоритетного (первого) канала по соответствующей шине 47 группы шин запросов на обслуживание 29 через схему НЕ 48 блокирует возможность установки запроса на выходе схемы И 49 (схемы 37 запроса второго канала на обслуживание) на время ожидания установки и удовлетворения запроса первого канала на обслуживание. Если второй канал установил запрос на соответствующей шине 50 группы шин 29 и нет ни запроса, ни предварительного занроса первого канала, и процессор уже не выполняет обслуживающую микропрограмму канала, т. е. не установлен ни один триггер в регистре блокировки повторного прерывания 35, то на выходе схемы И 52 дешифратора запросов на обслуживание 32 устанавливается признак запроса второго канала, но которому (так же, как и по запросу первого канала) устанавливается в единичное состояние триггер запросов 33 каналов на микропрограммное прерывание и в такте переключения адреса постоянной амяти устанавливается триггер блокировки 3 повторного прерывания второго канала в егистре 35 через схему установки 36. Этот риггер находится в единичном состоянии до

окончания выполнения микропрограммы обслуживания запроса второго канала. При этом через схему И 43 блокируется возможность повторной установки триггера 33. В такте возврата триггер 53 сбрасывается через схему И 46.

Если к началу выполнения такта возврата какой-либо каиал установил запрос на микропрограммное прерывание на соответствующей шине (39 или 50), то первым сигналом такта возврата по шине 45 триггер блокировки повторного прерывания того канала, запрос которого удовлетворялся, переводится в нулевое состояние, а следугонщм сигналом такта возврата по шине 54 через схему И 55 и схему установки 36 переводится в единичное состояние триггер 42, если установлен запрос первого канала, или триггер 53, если установлен запрос второго канала и нет ни запроса, ни предварительного запроса первого канала. При этом блокируется возврат к прерванной микропрограмме при ИОМОП1И схемы блокировки 38 возврата адреса постоянной памяти, состоящей из последовательно соединенных схемы И 56 и схемы НЕ 57, и организуется переход непосредственно к считыванию соответствующего управляющего слова и определению признака запроса на обслуживание, минуя запоминание содержимого регистров пропессора, так как в специальной части оперативной памяти еще находятся копии содержимого регистров процессора, записанные при первом переходе к микропрограмме обслуживания.

Признак запроса формируется при иомощи блока управления адресом постоянной памяти, представленного на фиг. 3.

Первым сигналом такта переключения по шине 65, выполняемого в процессоре по запросу каналов на микропрограммное прерывание, текуппш адрес прерванной микропрограммы через выходные пшны 30 и схему приема 59 передается в регистр возврата адреса 58 постоянной памяти.

Следуюишм сигпалом такта переключения, приходящим по шине 66, по установленному запросу с триггера 33 через схему И 67 и схему ИЛИ 68, входящие в состав схемы формпроваиия адреса постоянной памяти 64, начальный адрес икропрограмм обслуживания передается па входные адресные шипы 31.

Последним сигналом такта переключения, приходящим по щнне 44, по признаку канала, получившему приоритет в обслуживании его запроса (т. е. по триггеру блокировки повторного прерывания 42 или 53) через соответствуюи1ую схему управления 63, соответствуюнхий шифратор 62 (по признаку канала, поступиваему по соответствуюпгей щине 69 группы шин 29) и схему занесения 61 в регистре 60 устанавливается признак запроса канала (окончание операции ввода-вывода, зацепление и т. д.).

Затем начинается выполнение обслуживающей микропрограммы. После завершения микропрограммы обслуживания запроса канала

выполняется такт возврата, в котором но признаку такта возврата (шина 72), поступающему по соответствующей щине передачи (полей) микрокоманды 22 после одного из сигналов такта возврата (шина 55), если в блоке 13 не установлен запрос ни одного из каналов, т. е. если возврат адреса не бпокируется схемой 38 (см. фиг. 2), адрес микрокоманды, запомненный в такте переключения, из регистра 58 через схему выдачи 73 и схему ИЛИ 68 и входные шины передачи адреса 31 передается в адресный регистр 9 и таким образом производится переход к выполнению прерванной микропрограммы.

Если к моменту заверщения микропрограммы обслуживания запроса канала будет установлен запрос этого же или другого канала, то возврат адреса постоянной памяти блокируется сигналом, поступаюиим из схемы блокировки 38. В этом случае последним сигналом такта возврата, поступающим по шипе 74, по единичному состоянию соответствующего триггера блокировки повторного прерывания (42 или 53) через схелп И 75 и соответствующую схему управления 63 и шифратор 62 (по признаку запроса, поступившему по соответствующей шине 69 группы шин 29), а также через схему занесения 61 устанавливается в регистре 60 признак запроса канала, получившего приоритет в обслуживании.

Микрокоманда, следуюшая за тактом возврата, выполняемым микропрограммно, производит переход к считыванию соответствующего управляющего слова канала, определению признака запроса и т. д. Таким образом, как бы продолжается начатая по первому запросу микропрограмма обслуживания. Это позволяет сократить время обслуживания запросов каналов, что особенно важно для устройств типа магнитных дисков (т. е. устройств, имеюн1их ограниченное время ожидания новых команд в некоторых последовательностях цепочек команд).

При одновременной работе обоих капало время выполнения обслуживаюи1их микропрограмм удлиняется из-за того, что отдельные циклы оперативной памяти и оборудование пронессора используются для удовлетворения запросов каналов на передачу данных. Для регулирования частоты удовлетворяемых процессором запросов на передачу данных при одновременной работе обоих каналов используется блок управления запросами на передачу данных 15, представленный на фиг. 4.

При поступлении запроса на передачу данных по соответствующей шине 81 группы шин запросов на передачу данных 24, если не удовлетворяется запрос второго канала (т. е. не установлен в единичное состояние триггер 78 работы второго канала) и нет признака срочного запроса второго канала (на выходе схемы 79), то на выходе схемы И 82 дешифратора запросов 76 каналов на передачу данных устанавливается признак запроса первого канала на передачу данных, который через схему ИЛИ 83 II схему ИЛИ 84 поступает через соответствующую шину 25 в процессор. По этому запросу процессор переключается на выполнение тактов «чтения - записи, во время которых осуществляется передача данных между обслуживаемым каналом п оперативной памятью. При этом по сигналу переключения, поступающему по шине 85 и выходной шине 28 управления процессором (из блока 7) через схему 86 устанавливается в единичное состояние триггер 77 работы иервого канала, который поддерживает возбужденным выход схемы ИЛИ 83 до окончания цикла передачи данных и блокирует через схему ПЕ 87 возможность установки признака запроса второго канала на передачу данных на выходе схемы И 88 дешифратора 76.

Если установлен запрос на передачу данных второго канала на соответствующей шине 89 группы шин 24 запросов на передачу данных, нет запроса первого канала н не установлен триггер 80 блокировки запроса второго канала, то на выходе схемы И 88 дешис|)ратора 76 устанавливается признак занроса второго канала, который через схему ИЛИ 90, схему ИЛИ 84 и щину занросов каналов 25 поступает в блок микропрограммного управления 7. По сигналу переключения но шине 85 в этом случае через схему 91 устанавливается триггер 78 работы второго канала, единичное состояние которого поддерживает на выходе схемы ИЛИ 90 возбужденным признак запроса второго канала на передачу данных до конца цикла передачи данных.

Если возбуждены запросы обоих каналов на передачу данных одновременно, то вначале устанавливается признак работы первого канала и удовлетворяется его занрос.

Обычно приоритет занроса первого канала на передачу данных выще, чем приоритет запроса второго канала. Но если во втором канале сформировался срочный запрос на передачу данных и поступил по соответствующей шине 92 срочного запроса второго канала группы шин 24, а срочного запроса первого канала на передачу данных нет, то на выходе схемы И 95 устанавливается призпак срочного запроса второго канала, который через схему ИЕ 96 блокирует установку запроса первого канала на передачу данных на выходе схем И 82 и ИЛИ 83, если даже запрос первого канала установлен.

Признак срочного запроса устанавливается в канале в том случае, если его буфер данных заполнен (в случае вынолнения команды считывания с внешнего носителя) или пуст (в случае выполнения команды записи).

Если оба канала установили срочные занросы, то вначале удовлетворяется запрос первого канала.

При одновременной работе обоих каналов, учитывая более жесткие требования ко времени выполнения обслуживающих микропрограмм со стороны устройств, подключенных к первому каналу, необходимо ограничивать

частоту удовлетворения запросов второго капала в течение времени выполнения микропрограммы, обслуживающей запрос первого канала. По соответствующему признаку запрос

первого канала на микропрограммное прерывание (зацепление), вырабатываемому в блоке управлепия адресом постоянной памяти 14, в такте переключения или такте возврата (описание фиг. 3) устанавливается триггер блокяровки запросов второго канала 80, единичное состояние которого блокирует установку признака запроса второго канала на передачу данных до формирования признака срочного запроса второго канала. При этом через схему

И 95, ИЛИ 90 и ИЛИ 84 в блек 7 ностунает запрос на передачу данных и, как описано ранее, при переключении на такт передачи данных триггер 78 работы второго канала устанавливается в единичное состояние. Таким образом, организуется удовлетворение только срочных запросов второго канала в течение времени выполнения процессором запроса первого канала на зацепление (получение новой команды).

Триггер 80 переводится в нулевое состояние в конце выполнения обслуживающей микропрограммы первого канала в такте возврата адреса постоянной памяти, когда триггер блокировки повторного прерывания первого канал а 42 переводится в нулевое состояние по сигналу, вырабатываемому на выходе схемы И 46 (фиг. 2).

Триггер 78, а также триггер 77 сбрасываются в нулевое состояние одним из сигналов последнего такта цикла передачн данных (такта заииси), поступающим по шине 97, по сигналу признака такта, вырабатываемому в блоке 19 и приходящему по шине 98 на схему И 99. Таки.м образом, триг ер ):аботы соотвстствующего капала находится в единичном состоянии в Te-ieiiiie ijcero никла передачи данных между оперативной памятью г- обслуживаемым каналом.

Циклы передачи дат ьх между каналами и

01ера ивной памятью выполняются процессоры независимо от тек.у)1:е.й работы. Запросы на )е)едачу данных от каналов имеют наивысщиГ, приоритет. (Зни могут приостанавливать вынолнснне .микропрограмм, обслуживаюЦ1ИХ запросы каналов, которые, в свою очередь, могут прерывать выполнение любых инструкций 3 процессоре, в том числе и инструкций ввода - вывода. Поэтому в процессе работы каналов необходимо следить за признаками, онределяющими адресацию обслуживаемого в данный момент канала. Для автома- мческого переключения признаков (обслуживаемых) каналов используется блок адресации каналов 16, представленный на фиг. 5.

При выполнении инструкций ввода - вывода нризнак адресуе :сго канала устанавливается микропрограммно в periiCTpe 100 по соответствующим сигналам, поступающим по шинам передач (полей) :;икрокоманды 22. Номера регистров каналоз, которые необходимо подключить к информационным шинам процессора (входным и выходным), указываются в микрокомандах и декодируются в дешифраторах 101 и 102 соответственно. Для переключения отдельных триггеров каналов используется дешифратор поля установки 103, управляемый микропрограммно. Выходные сигналы этих дешифраторов поступают в оба канала по шинам 23. Признаки каналов, установленные в регистре 100 (триггер признака 108 первого канала и триггер признака 109 второго канала), через дешифратор приоритета признаков 105 и соответствующие схемы ИЛИ 106 и 107 поступают в соответствующие каналы (первый и второй). Если выполнение инструкции ввода - вывода прерывается по запросу другого канала на обслуживание и процессор переходит к выполнению микропрограммного прерывания, то единичное состояние триггера блокировки повторного прерывания (42 или 53 - см. фиг. 2) через соответствуюп1ую схему И 110, схему ИЛИ 111 и схему НЕ 112 блокирует схемы И 113 и на выходе соответствуюшей схемы ИЛИ 106 (107) устанавливается признак обслуживаемого капала, Дешифраторы 101, 102 и 103 используются так же, как и при выполнении инструкций ввода - вывода. После выполнения обслуживаюгцей микропрограммы соответствующий триггер блокировки повторного прерывания (42 или 53) переводится в нулевое состояние и на выходах дешифратора 105 восстанавливается состояние, соответствуюн,ее содержимому регистра 100. Если выполнение инструкции ввода - вывода или обслуживаюшей микропрограммы каналов приостанавливается из-за запроса какого-либо канала на передачу данных, то по единичному состоянию триггера работы соответствуюшего канала (77 или 78) через схему ИЛИ 114 и схему НЕ 115 блокируются выхо5ы -схем И 110 и схем И ИЗ. При этом через схемы ИЛИ 106 или 107 в соответствуюшие каналы поступает признак обслуживаемого канала. Сигналы, необходимые для выполнения тактов передачи данных, вырабатываются в блоке управления передачей данных 19 (см. фиг. 1). После сброса триггера работы канала (первого 77 или второго 78) восстапавливается состояние схемы И ПО и И 113. Таким образом, блок адресации каналов 16 автоматически переключает признаки управляемых каналов на всех этапах выполнения операций ввода - вывода. Формула изобретения Устройство управления каналами, содержашее коммутатор и блок управления передачей данных, соединенные по входам и выходам с соответствующими входами и выходами устройства, отличающееся тем, что, с целью расширения функциональных возможностей и повышения надежности, оно содержит блок управления запросами на микропрограммное прерывание, блок управления адресом постоянной памяти, блок управления запросами на передачу даппых и блок адресации каналов, причем первый выход блока управления запросами на микропрограммное прерывание соединен с первым входом блока управления адресом постоянной памяти, первый выход которого подключен к первому входу блока управления запросами на передачу данных, второй и третий входы которого соединены соответственно со вторым выходом блока управления запросами на микропрограммное прерывание и выходом блока управления передачей данных, вход которого подключен к первому выходу блока управления запросами на передачу данных, второй выход которого подключен к первому входу блока адресации каналов, второй вход которого соединен с третьим выходом блока управления запросами на микропрограммное прерывание, первый выход блока адресации каналов подключен к управляюш,ему входу коммутатора, второй вход и второй выход блока управления адресом постоянной памяти подключепы соответственно к адресным входу и выходу устройства, третий, четвертый и пятый входы блока управления адресом постоянной памяти, четвертый и пятый входы и третий выход блока управления запросами на передачу данных, третий вход, второй и третий выходы блока адресации каналов, входы и четвертый выход блока управления запросами на микропрограммное прерывание соединены с соответствующими управляющими входами и выходами устройства.

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для управления каналами | 1974 |

|

SU520592A1 |

| Устройство управления каналами | 1973 |

|

SU518769A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ | 1973 |

|

SU386395A1 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Устройство для управления каналами | 1976 |

|

SU641436A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для управления каналами связи вычислительной системы | 1975 |

|

SU525095A1 |

| Процессор ввода-вывода | 1979 |

|

SU798782A1 |

с SJ70ffa S3

I Салона 2

38

Г лока55

Авторы

Даты

1977-02-05—Публикация

1972-06-05—Подача