(54) УСТРвЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство управления каналами | 1972 |

|

SU545983A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ | 1973 |

|

SU386395A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Селекторный канал | 1973 |

|

SU519703A1 |

| Устройство для управления каналами | 1984 |

|

SU1372329A2 |

| СШТШДА ОБРАБОТКИ ДАННЫХ1 Т Бii^f;'- ViJ- i^ О г^ ал | 1970 |

|

SU433484A1 |

| Селекторный канал | 1973 |

|

SU517019A1 |

| Устройство для управления каналами связи вычислительной системы | 1975 |

|

SU525095A1 |

| Устройство для управления диагностикой каналов | 1973 |

|

SU526876A1 |

. -. V-.. V

Иг бретёаве относится к вь1чис ||итепьг: ной технике,-,вчастности к оргйяййэайвд. структур устройств управпення каналами, и является дальнейшим усовершенствованием устройства управпення канаяами.

В основном авт. св. № 38бЗ§5 oira 7ано устройство управления каналами, содержащее бжж запросов на пёредачу яави йых, бпок формирования управляюошхсвг вааов, блок вфо(ла1шовных шив ариф метячесжого логического устройства, блок адресапви регистров я триггеров управп еыых каналов, 6«ж запросов на «лвкропрограммное прерыва ю, бяоки сбо{Жв в рмационных aiq ecnux шив в овв KJDcnee зашиты кагатов, вяоки коммутаовк информашкжжых шин каваяов в npooecsсора я бпокя упрефаеияя ко1утмуташ1ей я, формашюяшлх {ши каишюв и процессора.

Одмдако в «аееством устрогйствё ynpiaB пения канаяамя отсутствует Kontpoль его работы пря выполнения ооерадий ввьда-вы |вода. -- - - . .

Цель кзобрегеняя 1ювышение надежн вости работы каналов ва всех этапах вьй , полнения операций ввооеквывода. Для го устройство управленая каналами содер 5 нсвт блок контроля передачи управляющейинформации, блок контроля аппаратных приостановок, блок контроля микропрограмм ных П1шостановок и элемент ИЛИ, выход которого подалючен к выходу признака .

10 |сбоя устройства, первый, второй и третий входы элемевта ИЛИ соединены соЬтвет jCTseBBo с выхорамв {(шзвлжов с6оя|ёлоха («сонтроля яереовч утфавл ошей кнформацнн, {блока контроля апяаратяых пряостанЬво ;

tft 1в блока контроля микропрограммных прв ocTaiioeoK. инфо{ 4аш1оввые выходы яошишчевы к соогветствуюшим ияформаА 1Ш01ЩЫМ входам блока сборки илформапя онных шив ари етеческого к яогяческо

20 го устройства, оервый в второй вхЪаы бпо ка контроля передач управляющей ции соединены соответственно с входной i шиной группы шин управления процессора {и выходом блсжа адресааии регистров и

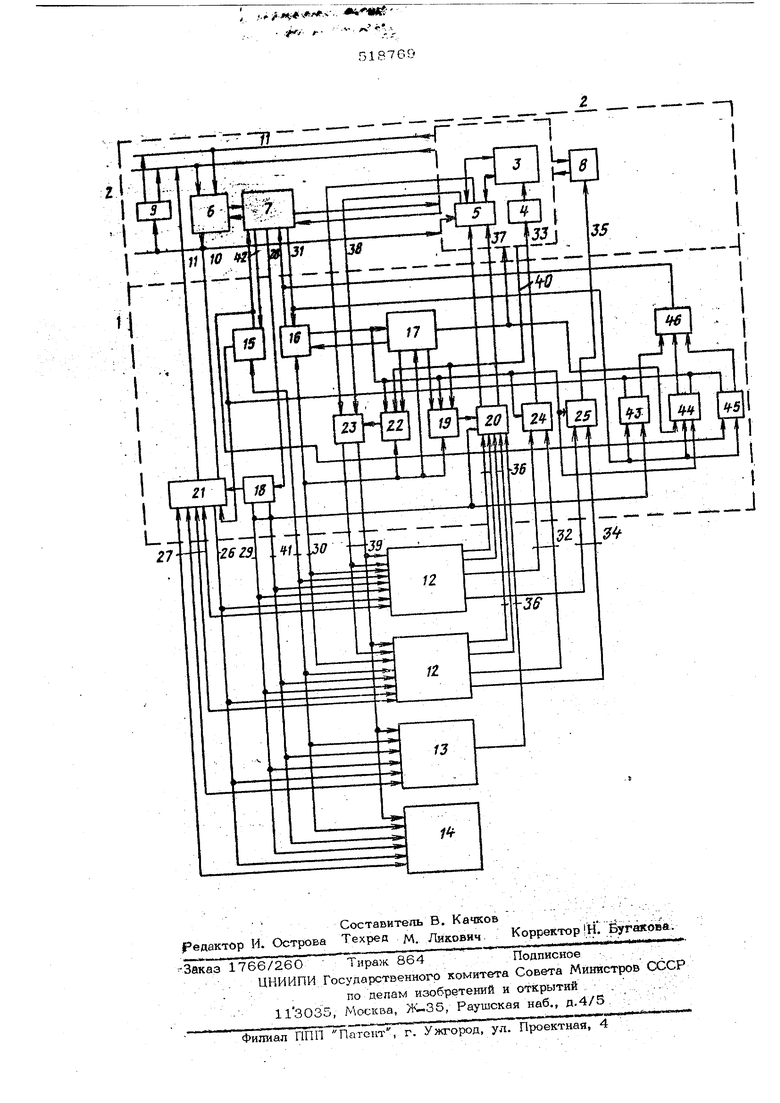

25 I триггеров управляемых каналов, первый, второй и третий входы бпоКа контроля ап(паратных п.риостановок подключены соо вегственно к выходу управления основной памятью блока формирования управляющих сигналов, выходу признаков управляемых каналов блока запросов на передачу данHbtx и соответствующей входной шине группы шин управления процессора, первый к второй входы блока контроля микропрограм мных приостановок соединены соответствен но с выходом блока запросов на микропрограммное прерывание и соответствующей входной шиной группы шин управления процессора.. ,: Это позволяет контролировать работу / устройства управления каналами на всёк этапах выполнения операций бвода-вывоДа. Устройство управления каналами пред«азначено Для. подключения к процессору Кйналов ввода вывода и управления переда чей) данных между ними. Блок-схема ус-р ройства представлена на чертеже, где 1устройство управления каналами; 2 - процессор; 3 - основная память процессора; 4- адресный регистр основной памяти; 5- информационный регистр основной памяти; 6 - арифметическое и логическое устройство; 7 - устройство Микропрограммного управления; 8 - блок зашиты памяти; 9 - блок регистров; 10 - выходные информационные шины арифметического и логического устройства ; 11 - входные информационные шины арифметического и логического устройства; 12 - селекторны канал; 13 - мультиплексный канал; 14 пульт управления; 15 - блок запросов на микропрограммное прерывание; 16 - блок запросов на передачу данных; 17 - блок формирования управляющих сигналов; 18блок адресации регистров и триггеров управляемых каналов; 19 - блок управления коммутацией информационных щин кан лов; 20 - блок коммутации информационных шин каналов; 21 - блок сборки инфор мационных шин арифметического и логйчес iKoro устройства; 22 - блок управления коммутацией информационных шин процессора; 23 - блок коммутации информацйо ных шин процессора; 24 - блок сборки ад ресных шин каналов; 25 - блок сбо1жиши ключей зашиты каналов; 26 - входные информационные шины арифметического и логического устройства каналов,; 27 - вы ходные информационные шины арифметичес кого и логического устройства каналов; 28 - первая группа шин микропрограммно го управления процессора; - первая группа шин управления каналами; 30 - вт рая группа.шин управления каналами; 31 группа шин управления процессора; 32 адресные шины основной памяти каналов; 33 - адресные шины основной памяти itpoцессора; 34 - шины ключей зашиты каналов; 35 - шины ключей зашиты процессора; 36 - выходные информационные шины , каналов; 37 - входные информационные ши-; ны процессора 38 - выходные информационные i шины npCHieccopa; 39 - входные информ ционные шины каналов; 40 - группа шин управления основной памяти; 41 - третья l pynna шин управления каналов; 42 - вторая груйпа шин микропрограммного упра&-, лейия процессора; 43 «. блок контротш передачи управляющей информации; 44 -блок, контроля аппаратных приостановок; 45 контроля микропрограммных приостаJHOBOK; 46 - элемент ИЛИ. Работа усгррйства управления каналами схзушествляется по командам, которые реализу1отся микропрограммно. Одна из основных системнь1х функций - управление передачей данных между упомянутыми подсистемами.. Операция передачи данных начинается по специальной команде, которая задает адрес канала и устройства ввод вывода и при помощи специальных управляющих слов указывает код команды ввод -вывода, начальный адрес основной памяти, количество байтов данных, которые необходимо передать, управляющие признаки и ключ зашиты. Канал формирует управляющее слово устройства и хранит его на своих; регистрах или в специальной памяти. ,,-.,, Для передачи управляющей информации между процессором и регистрами каналов служит арифметическое и логическое устройство 6, выходные информационные шины арифметического и логического устройства 10, блок сборсй информационных шин арифметического и логического устройства 21 и входные информационньте шины арифметического и-. Логического устройства кагналов 26. С Л ТоЯНИ€ ,| ГЙстров каналов может быть. мйердпр граммно цроанализи|ровано через выходШе информационные шины арифметического -HxTiorHHecKoro устройства каналов 2 7, бпо« сборки информационнь1х шин арифметического и логического устройства 21 и входные информационные пщны арифметического и логического устройства 11.i .При передаче управляющей информации мёжду.процессором 2 и регист эами каналов 12-14 признак регистра, в который необходимо принять или из которого необходимо выдать информацию, указывается в микрокоманде, принимается через соответствующие шины первой группы шин микропрограммного управления процессора 28 в блок адресации регистров и . геров управляемых каналов ife и поступает в канапы через соответотвующйе шйны адресации управляемых каналов первой группы шин управления каналами 29. Получив команду, кйнал обычно освобождает процессор для выпалнения других команд. Селекторный канал 12 при готоЬности .принять или передать байт или группу бай тов данных, возбуждает запрос на переден чу данных, который через соответствующу ю шёну запросов второй группы шин у правления каналами 30, блок вапросов на передач данных 16 и соответствующую шину группы шин управления процессора 31 поступает в процессор 2. По этому запросу работа процессора по выполнению текупфей мшсропр раммы приостанавливается на цикл передачи данньтX между ос новной памятью и каналом. При этом адрес основной памяти передаётся н канала через адресные шины основной памяти канала 32, блок сборки адресных шин (основной памяти) каналов 24 и адресные (ШИНЫ основной памяти процессора 33 в .адресный регистр основной naiviHTH 4,атак1же ключ защиты памяти из канала через шины ключей защиты памяти каналов 34, блок сборки шин ключей зашиты каналов 25 и шины ключей защиты процессора 35 поступает в блок защиты памяти 8. : Если выполняется команда ввода, то данные из канала передаются через выхо :ные информационные шины каналов 36, блок коммутации информационных шин к налов 2О и входные информационные шины процессора 37 в информационный р&гистр основной памяти 5. Если выполня- ется команда вывода, то данные из основной памяти 3 через ин4)ормационный регистр Основной памяти 5, выходные инфор мационные шины процессора 38, блок ком мутации информационных шин процессора 23 и входные информационные шины каналов 39 передаюртся в регистры канала. Блоки управления коммутацией информа ционных шин 19 VL 22 обеспечивают соответствующие пересоеди яен|1Я информацио ных шин 36 и 37f/38 «,09 каналов и процессора в блоках к6К1мутйции йви{ 6рмациОнных шин 20; .и fe зависимости от количества передаваемых байтов, четности адреса основной памйти (4р) и выпопня емой команды (прямай или обратная передача 3D). При передаче данных между мульти.плексным каналом 13 и процессором 2 или при передаче байтов состояния канал возбуждает запрос на Микропрограммное прерывание, который через соответствуюшук шину запроса каналов на микропро-; 69 граммное прерывание третьей группы шин управления каналов 41, блок запросов на микропрограммное прерьшание 15 и вторую группу шин микропрограммного управления процессора 42 поступает в уотройство микропрограммного управления процессора 7. По этому сигналу выполняется специальная микропрограмма, которая обеспечивает передачу байта данных или байта состояния в основную память 3. В каждом из управляемых устройством 1 каналов осуществляется контроль передаваемой информации по |Четности, а также контроль работы интерфейса. Одной из функций предлагаемого ус-р.ройства управления каналами является контроль за выполнением устройством операакЛ ввода-вывода на различных ее этапах: а)контроль передачи управляющей информации;б)контроль выполнения аппаратных приостановок (циклов передачи данных между селекторными каналами 12 и основной памятью 3); в)контроль выполнения микропрограк мных приостановок каналов. Для выполнения этих функций устройство управления каналами 4 содержит {блок контроля передачи управляющей информации 43, блок контроля ап ;аратных приостановок 44, блок контроля микропрограммных приостановок 45 и элемент ИЛИ 46. Каждый из каналов представляет собой набор регистров, отдельно управляемых элементов и логических , соединенных с устройством управления каналами 1 при помощи системы адресных, информационных и управляющих шин. Как уже отмечалось, для адресации регистров каналов и отдельных триггеров используют ся поля микрокоманды, управляющие noj ключением регистров к входам и выходу арифметическргю и логического устройст ва 6. Соответствующие этим полям разряды микрокоманды принимаются через соответствующие шины первой группы шин микропрограммного управления процессора 2-8 в блок адресации регистров и триггеров управляемых каналов 18, дешифруются и вместе с признаком работающего в данный момент канала передаются в каНалы ввода-вывода через соответствующие Шины адресации управляемых каналов группы шин управления каналами 29. Признаки каналов устанавливаются предварительно перед началом передачи управляющей информации между требуемым кан&лом и процессором 2 и переключаются

микропрограммно или аппаратно при пвр&-; ходе к обмену- у11равляюшей информацией ; другим каналом.

Для контроля передач управляющей нвн формации между кацапами ввода-вывода и процессором призн 1ки каналов-через СООТ- ветствующне шины первой ; г |зуппы шнн управления каналами 29 .пают в блок онтрогш передачи ущ авлякй1аёй информации 43, который проверяет правильность формирования сигналов управления переде чей управляющей информаыяя.-1ВЬли выпоп няемая микрокоманда определяет обмен информацией между одним из регистров заданного канала и процессором, а в бло ке адресации регистров и триггеров управляемых каналов 18 одновременно установ лено более одного или ни одного признака канала, то блок контроля передачи уппа& ляюшей информации 43 формирует сигнал сбоя, который через элемент ИЛИ 46 в шину признака сбоя группы шин управления процессора 31 останавливает работу процессора. При этом в блоке контроля пере« дачи управляющей информации 43 устанавливается соответствующий индикатор, определяющий состояние признаков управля&мых каналов.

После завершения передачи управляющей информации каналы 12, 13 обеспечивают управление дальнейщим выполнением операции ввода-вывода. Устройство управления кан &1ами 1 контролирует правильность выполнения циклов передачи данных между каналами при помощи блока контроля attпаратных приостановок 44.

Приоритет селекторных каналов 12 на передачу данных определяется в бпоке запросов на передачу данных 16. Если во бужден запрос на передачу данных только от одного из селекторных каналов 12, блок запросов на передачу данных 16 формирует признак работы этого канала, который чв рез блок управляющих сигналов 17 а соответствующую щину второй группы шян управления каналов ЗО поступает в обслу жнваемый канал. Этот признак остается возбужденным до конца цикла передача данных между каналом 12 в оперативной памятью 3.

ЕСЛИ возбуждены запросы на передачу данных от двух селекторных каналов одяовременно, то блок запросов на передачу данных 16 формирует признак работы более приорительного канала я выполняется ЦИКЛ передачи данных между ним и оперативной памятью 3. Обычио приоритет первого селекторного канала 1S выше запроса на передачу данных второго сежгкториого канала.

. КвжяыК йШп 1(ередачя данных между каналом 12 н оперативной памятью 3 состоит из последовательности тактов ггенив-обработкй-записи, сигналы выполнения которых формирует блок формиров ния управляющих снгвапов 17 и которые поступают в проаессор 2 и канал 12 по соответствующим управляющим шннам 4 О и 30 пропессора в каналов соответстввЕк но.

.4 . -.--.-- .- . - -- -:Йа этапе пёредв1га данных между селекторными каналами 12 и оперативной па мятью блок контроля аппаратных приостановок 44 проверает:

а) правильность формирования прязнв ков работы селекторных каналов (не должно быть одновременно установленных признаков работы обоих селекторных каналов или ни одного из них в цикле передачи данных);

: б) правильность формирования последовательности тактов в циклах передачи да ных (не должно быть двух тактов чтения подряд или трвта записи без предварительного чтения или регенерации).

Если блок контроля аппаратнь1х приоо тановок 44 обнаружит невыполнение одного из указанных вьше условий, то он

о мирует сигнал сбоя, который через элемент ИЛИ 46 и соответствующую щину признака сбоя группы шин управления npcw, цессора поступает в блок микропрограммного управления 7 и останавливает работу процессора. При этом в блоке кок троля аппаратных приостановок 44 устанавливается соответствующий причине сбоя индикатор.

Как уже ртиё 1алось, кргда каналы завершают передачу даршх, они ус ан&вл вают запросы нй .{микропрограммную npSpcfaвовку. Приоритет каналов определяется в блоке запросов на ышсропрснраммное пре{%1вавие 15. Мультиплексный канал имеет самый низкий приоритет среди , управляемых устройством 1. Приоритет обоих сел сторных каналов одинаков, ио если оба селекторных канала установила запросы на микропрограммную приостановку, то первый селекторный канал подуча ет прж(иггет перед вторым. Если уже началось обспултвавие запроса второго селекторного канала и поступил запрос от .первого селвггорного К€шала то его обслуживание буоет задержано до заве{явеш1Я ..микропрограммной приостановки второяго с лекторного канала. Таким образом, запрос на микропрограммную приостановку любого селекторного канала I может приостановить работу процессора ипи мультиплексного канала, но не может прервать микропрограк |мную приостановку другого канала.. Правильность установки приоритета запросов каналов 1Сонтроли|ЧГвт блок контроля микропрограммных приостановок 45 |который вырабатывает сигнал сбоя я уст навливавтсоответств/юпшй индикатор, еоли:.,,., , - ; а)блок запросов на микропрограммное прерывание 45 форми гет свгяал запроса на микропрограммную приостановку в пере дает его в процессор во время обслуживания запроса селекторного канала; б)при одновременном появления запро jCOB от мультиплексного и селекторного кд: налов приоритет получает мультншюксный канал. Сигнал сбоя, сформированный в бясже контроля микропрограммных приостановок 45при обнаружении любого из указанных; вьпие сбоев, поступает через элемент ИЛИ46в блок микрт программного управления 7 и останавливает работу процессора.: Влюбом из описанных случаев рста нова процессора по сбою в работе jycrpo ства управления каналов 1 более точно причину останова можно определить путем анализа состояния индикато1х в в бло ке контроля передачи управляющей янфор ;Мация 43, блоке контроля аппаратных приостановок 44 и блоке контроля мнкро-. |В|юграммных приостановок 45 через блок Информационных шин арифметнческого н т |гичвского устройства 21 и входные фермационные шины арифметнческого н лсм арического устройства 11. .; 9 10 Формула изобретения Устройство управления каналами по авт. св. N 386395, отличаю ше&« с я тем, что,с целью повышения надежности работы каналов, оно содержит блок н.... ,.. . ,.. ,i . . . .., --. - контроля Передачи управляющей информа, ции, блок контроля аппаратных приос аноetc fi. блок контроля микропрограммных прибогавовок и элемент ИЛИ,|выходкотЬ1: ого подключен к выходу признака сбоя уоТ ройства, первый, второй и третий входы алемента ИЛИ соединены соответственно f выходАмяпризнаков сбоя бткжа контроля . передач управлпюшвй информации, блока ковггродя аппаратных приостановок и блока контроля микропрограммных прностано . I «ос, информационные выходы которых под ||ключены к соответствующим информационным {входам блока сборки передач информационных шнн арифметического я логического устрой- |ства, первый я второй входы блока коитроjmi передач управляющей информации нены соответственно с выходом блока адресацни регистров и триггеров управляй емых каналов и соответствующей входной шяной группы шнн управления процессора, рервый, второй и третий входы блока троля аппаратных приостановок подключены еоотввгс ёенно к ьыхоДу управления основа ной памятью блока формировання управлЯг юших сигналов, выходу признаков управлям емых каналов блока запросов на передачу д ааных и соответствукжей входной шине пы шин у правления процессора, первый входы блока контроля микропрограмм1&Х приостановок соединены соответственно с выходом признаков запросов блока запросов на микропрограммное прерывание и соответствующей входной шиной группы ишн управления процессора.

Авторы

Даты

1976-06-25—Публикация

1973-05-03—Подача