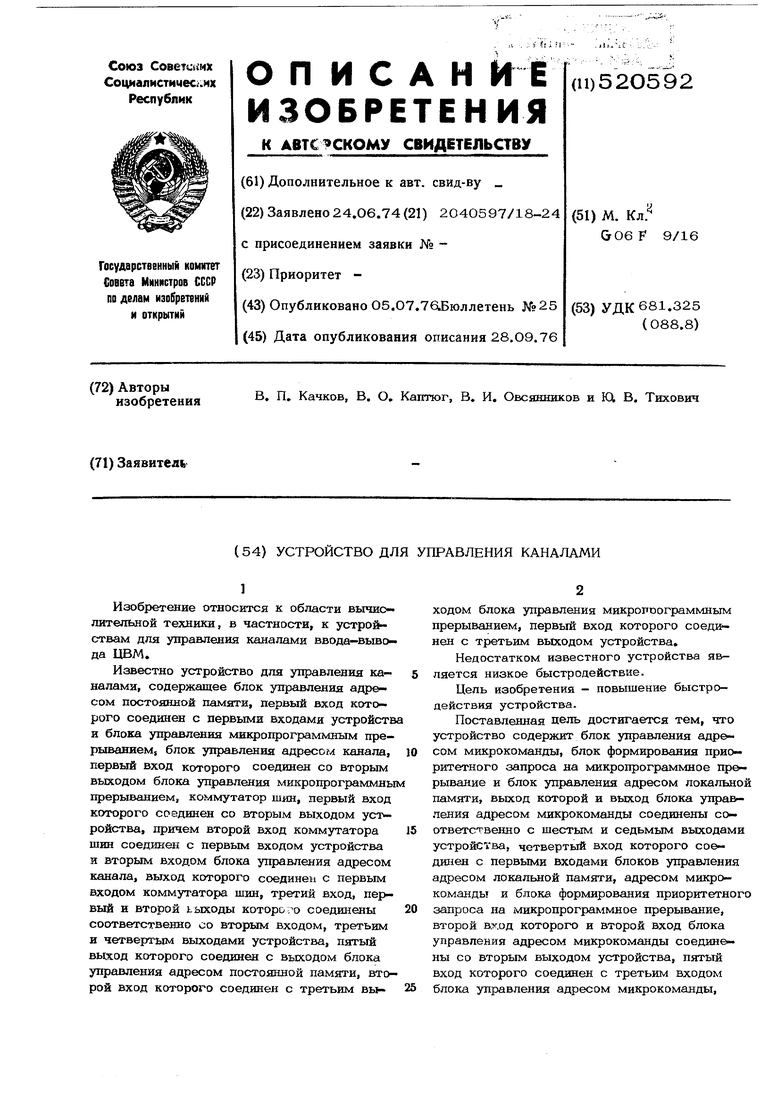

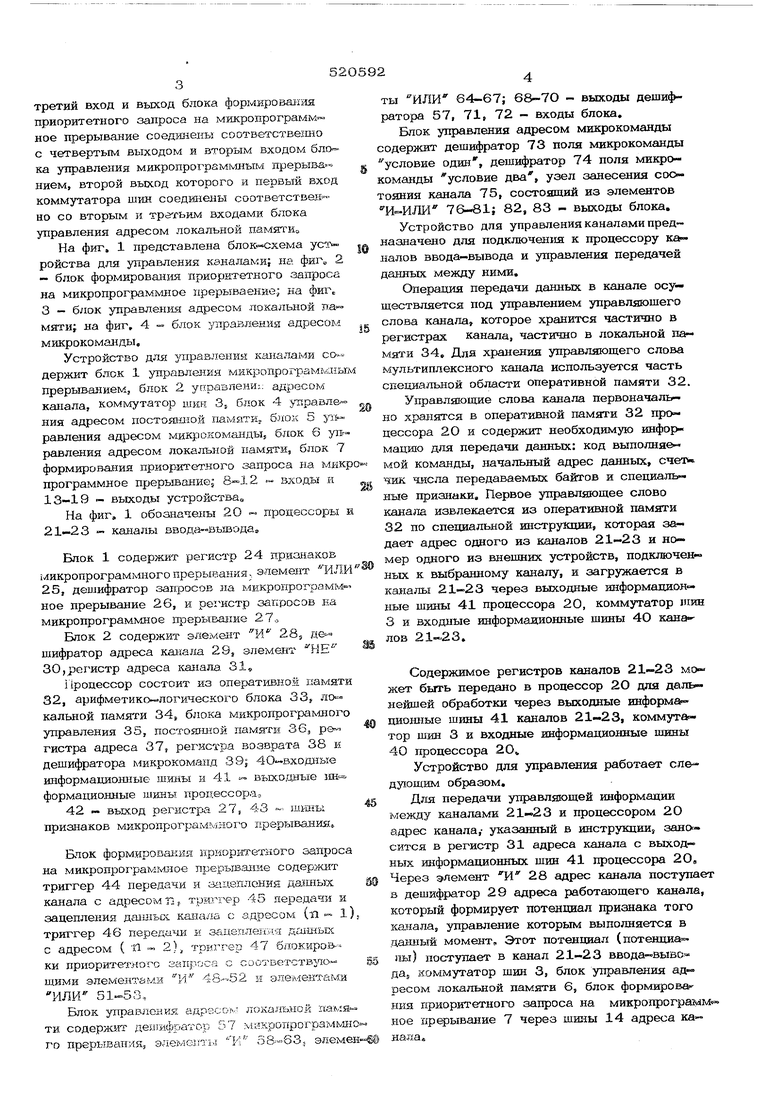

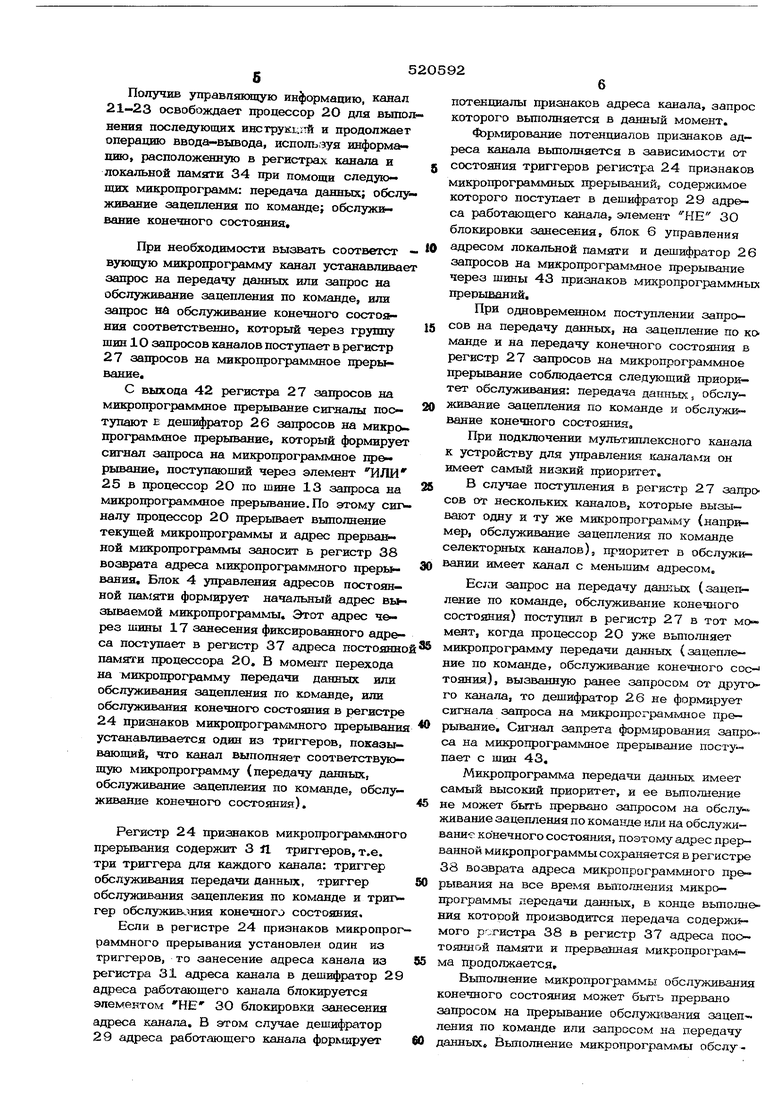

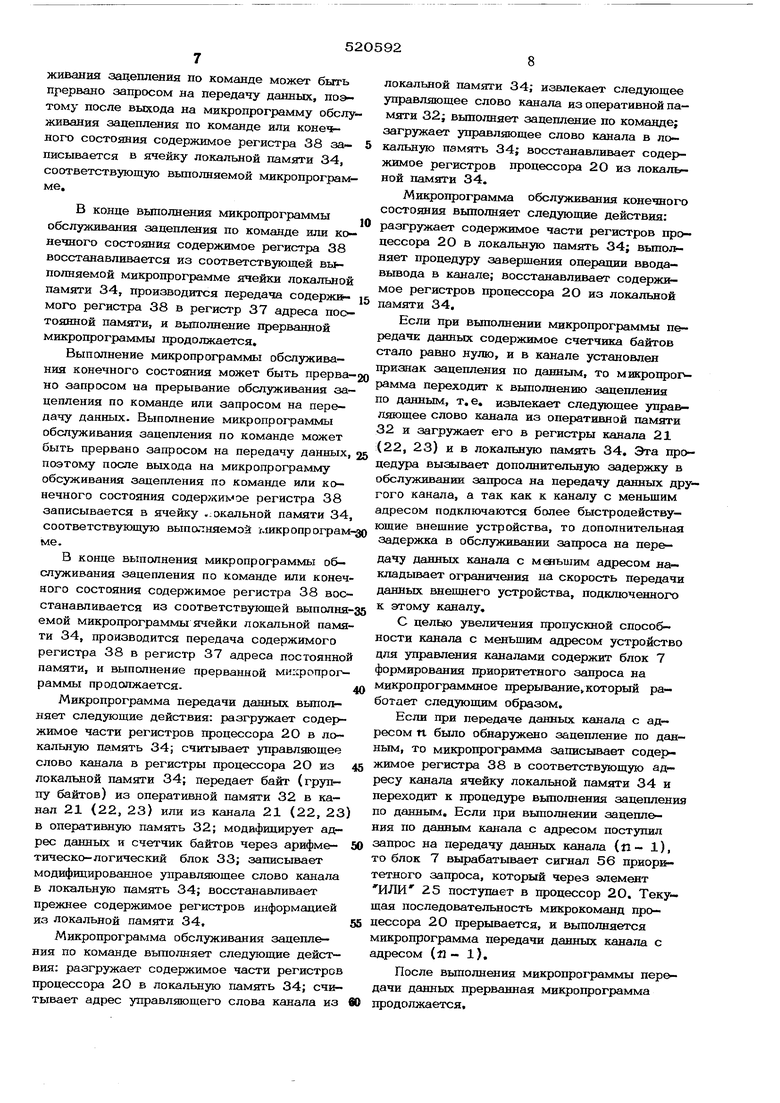

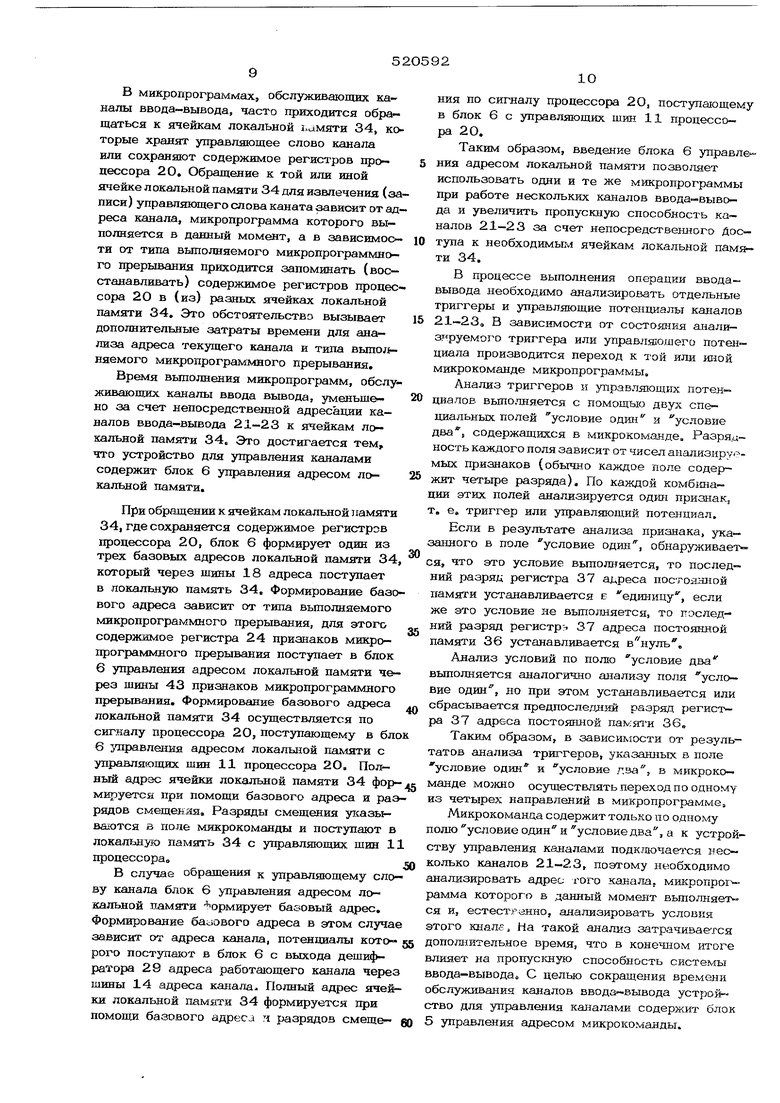

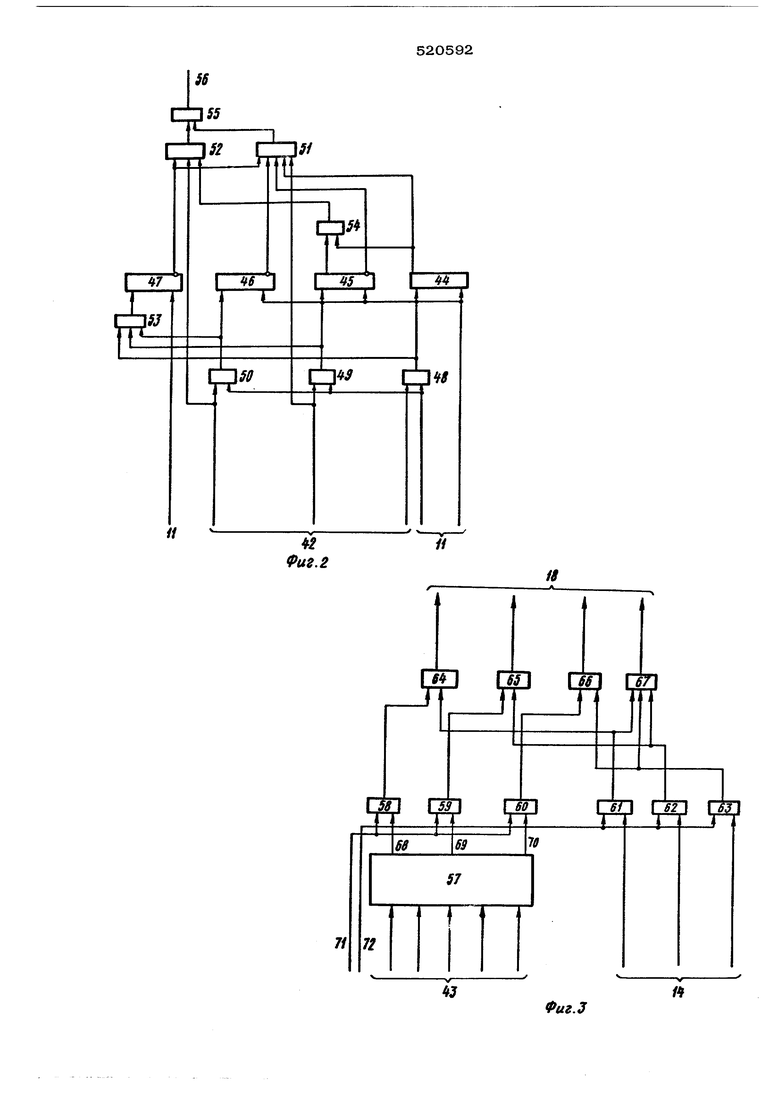

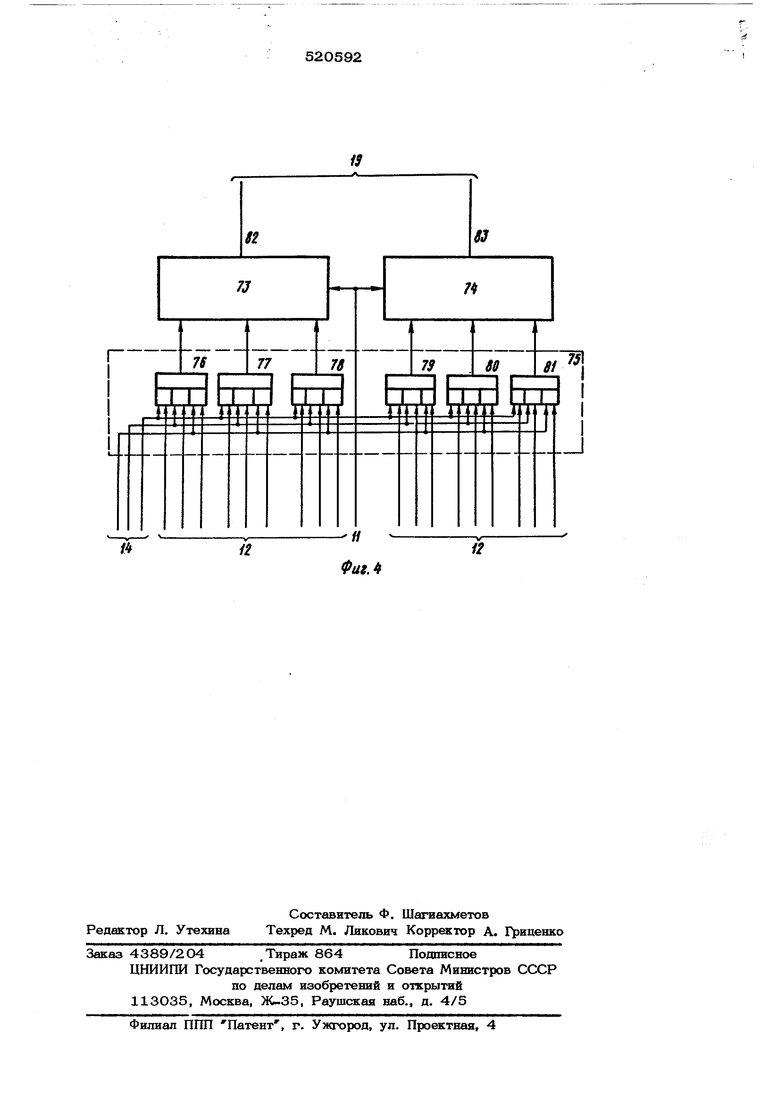

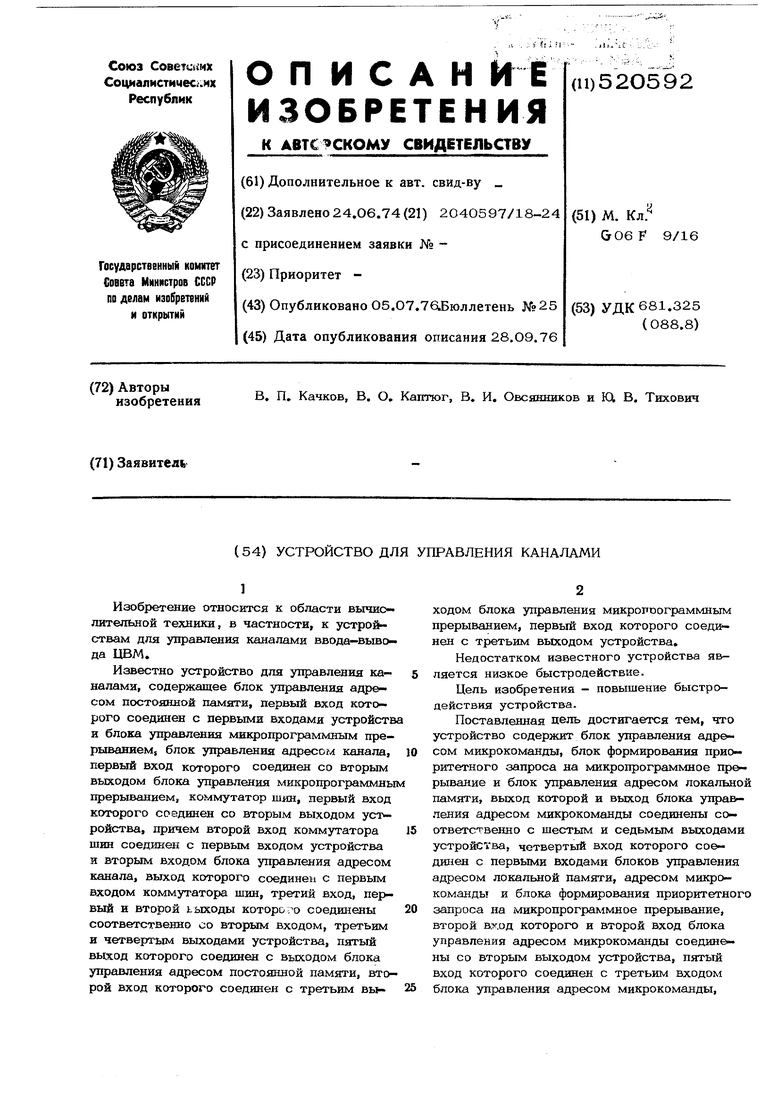

(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ КАНАЛАМИ третий вход и выход блока формирования приоритетного запроса на микропрограмм™ ное прерывание соедш1ены соответстве1шо с четвертым выходом и вторым входом бло ка управления микропрограмь-шым лрерыва- нием, второй выход которого и первый вход коммутатора шин соединены соответствен но со вторым и третьим входами блока управления адресом локальной памяти На фиг, 1 представлена блок-схема устройства для управления каналами; иа фиг„ 2 - блок формирования приор1-ггетного запроса на микропрограммное прерываение,; на фиг 3 - блок управления адресом локальной памяти; на фиг, 4 « блок лшравления адресом микрокоманды. Устройство для з-гправления каналами со держит блок 1 управления микропрограмкагы прерыванием, блок 2 упразпени : адресом канала, коммутатор шин 3, блок 4 управлеНИН адресом постояшюй памяти блок 5 jafrравления адресом микрокоманды; блок 6 уп равления адресом локальной памяти, блок 7 формирования приоритетного запроса на мик программное прерывание; 8-12 - входы и 13-19 - выходы устройства На фиг. 1 обозначены 20 процессоры 21-23 - каналы ввода-вьшода, Блок 1 содержит регистр 24 признаков микропрограммного прерыБания.. элемент ИЛ 25, дешифратор запросов на микропрограмм ное прерывание 26, и запросов на микропрограммное прерывание 2,7 о, Блок 2 содержит элемент 28, де. шифратор адреса 28, элемент НЕ ЗО,регистр адреса канала. 31, Процессор состоит из оперативной памят 32, арифметико-логического блока 33, ло- кальной памяти 34, блока микропрогракшого управления 35, постогошой памяти 36, р&« гистра адреса 37, регистра воаврата 38 и дешифратора К1икрокомапд 39; 4О -входные информационные шины и 41 ™ выходные lot формационные шины npoixeccopa, 42 выход регистра 27, 43 - ш1-шы признаков микропрограммного прерывания Блок формироаакия ириорг-ггеткого запроса на микропрограммное прерывание содержит триггер 44 передачи и з пюпления дазшых канала с адресомп. триггс р 45 передачи и зацепления дшшьсс канала с адресом (tl - 1 триггер 46 передачи и заяехАления данных с адресом ( П 2, триггер 47 бпокировн ки приоритетного защкса с соответств ао-Бдими элементами 4S.--52 и элементспми Езлок управления адресо л локальной памя ти содержит дешифратор 57 ;vi икр о прОГра м ьш 1Г 38-63, го прерывания, элемеиты ИЛИ 64-67; - выходы дешифратора 57, 71, 72 - входы блока. Блок управления адресом микрокоманды содержит дешифратор 73 поля микрокоманды условие один, дешифратор 74 поля микрокоманды условие два , узел занесения сос тояния канала 75, состоящий из элементов И-ИЛИ 82, 83 - выходы блока. Устройство для управления каналами пред назначено для подключения к процессору ка«налов ввода-вывода и управления передачей данных между ними. Операция передачи данных в канале осуществляется под управлением управляюшего слова канала, которое хранится частично в регистрах канала, частично в локальной памяти 34, Для хранения упр)авляющего слова мультиплексного канала используется часть специальной области оперативной памяти 32. Управляющие слова канала первоначал но хранятся в оперативной памяти 32 процессора 20 и содержит необходимую информацию для передачи данных: код выполняв™ мой команды, начальный адрес данных, счет чик числа передаваемых байтов и специальные признаки. Первое управляющее слово каналш извлекается из оперативной памяти 32 по специальной инструкции, которая задает адрес одного из каналов 21-23 и номер одного из внешних устройств, подключенных к выбранному каналу, и загружается в каналы 21-23 через выходные информационные шины 41 процессора 20, коммутатор JHHH 3 и входные информадионные шины 40 лов . Содержимое регистров каналов 21-23 мо жет быть передано в процессор 2О для дальнейшей обработки через выходные информационные шины 41 каналов 21-23, коммутатор шин 3 и входные информационные шины 40 процессора 204 Устройство для управления работает следующим образом. Для передачи управляющей информации между каналами 21-23 и процессором 2О адрес канала,- указанный в инструкции; заногсится в регистр 31 адреса канала с выходных информационных шин 41 процессора 20, Через элемент И 28 адрес канала поступает в дешифратор 29 адреса работающего канала, который формирует потенциал признака того канала, управление которым выполняется в дан11Ый момент. Этот потенциал (потенциа- лы) поступает в канал 21-23 ввода-выво да, коммутатор шин 3, блок управления аз ресом локальной памяти 6, блок формироваПИЯ приоритетного запроса на микропрограмм ное прерывание 7 через шины 14 адреса ка нала. Получив управляющую информацию, канал 21-23 освобождает процессор 2О для вьтол нения последуюпшх ннструкщ-тй и продолжает операцшо ввода -вывода, испош ауя информа- пвю, расположенную в регистрах канала и локальной памяти 34 при помощи следующих микропрограмм: передача данных; обслуживание зацепления по команде; обслужвн вание конечного состояния. При необходимости вызвать соответст - вующую микропрограмму канал устанавливает запрос на передачу данных или запрос на обслуживание зацепления по команде, или запрос йй обслуживание конечного состояния соответственно, который через группу шин 10 запросов каналов поступает в регистр 27 запросов на микропрограммное прерывание. С выхода 42 регистра 27 запросов на микропрограммное прерывание сигналы поступают Е дешифратор 26 запросов на микропрограммное прерывание, который формирует сигнал запроса на микропрограммное Щ)©рывание, поступаюший через элемент ИЛИ 25 в процессор 2О по шине 13 запроса на микропрограммное прерывание. По этому сиг налу процессор 20 прерывает выполнение текущей микропрограммы и адрес прервав ной микропрограммы заносит Б регистр 38 возврата адреса микропрограммного прерывания. Блок 4 управления адресов постоянной памяти формирует начальный адрес BI зываемой микропрограммы. Этот адрес ч&рез шины 17 занесения фиксированного адреса поступает в регистр 37 адреса постоянно намяти процессора 2О. В момент перехода на микропрограмму передачи данных или обслуживания зацепления по команде, или обслуживания конечного состояния в регистре 24 признаков микропрограмьшого щзерывани устанавливается один из триггеров, показывающий, что канал выполняет соо1ветствую- щую микропрограмму (передачу данных, обслуживание зацепления по команде, обслуживание конечного СОСТО5ШИЯ). Регистр 24 признаков микропрограмкшог прерьюания содержит 3 Я. триггеров, т.е. три триггера для каждого канала: триггер обслуживания передачи данных, триггер обслуживания зацепления по команде и триггер обслужив шия конечного состояния. Если в регистре 24 признаков микропрог раммного прерывания устаноншен один из триггеров, то занесение адреса канала из регистра 31 адреса канала в дешифратор 29 адреса работающего канала блокируется элементом НЕ ЗО блокировки занесения адреса канала. В этом случае дешифратор 29 адреса работающего канала форлшрует потенциалы признаков адреса канала, запрос которого выполняется в данный момент. Фзрьифование потенциалов признаков адреса канала вьшолняется в зависимости от состояния триггеров регистра 24 признаков микропрограммных прерываний, содеряшмое которого поступает в дешифратор 29 адреса работающего канала, элемент HP, 30 блокировки занесения, блок 6 управления адресом локальной памяти и дешифратор 26 запросов на микропрограммное прерывание через шины 43 признаков микропрограммных прерываний. При одновременном поступлении запросов на передачу данных, на зацепление по ко. манде и на передачу конечного состояния в регистр 27 запросов на микропрограммное прерывание соблюдается следующий приоритет обслуживания: передача данных s обслуживание зацепления по команде и обслуж вание конечного состояния. При подключении мультиплексного канала к устройству для управления каналами он имеет самый низкий приоритет. В случае поступления в регистр 27 запросов от нескольких каналов, которые вызывают одну и ту же микропрограмму (например, обслуживание зацепления по команде селекторных каналов), приоритет в обслуживании имеет канал с меньшим адресом, EcjcH запрос на передачу данных (зацегнление по команде, обслуживание конечного состояния) поступил в регистр 2.7 в тот момент, когда процессор 20 уже вьшолняет микропрограмму передачи данных (зацепление по команде, обслуживание конечного сое- тояния), вызванную ранее запросом от другого канала, то дешифратор 26 не формирует сигнала запроса на микропрограммное прерывание. Сигнал запрета формирования запро а микропрограммное прерывание поступает с шин 43. Микропрограмма передачи имеет самый высокий приоритет, и ее вьшолнение не может быть прервано запросом на обслуживание зацепления по комадде или на обслуживание конечного состояния, поэтому адрес прерванной микропрограммы сохраняется в регистре 38 возврата адреса микропрограммного пр&рывання на все время вьпюлнения микропрограммы передачи данных, в конце вьшолнения которой производится передача содерж мого регистра 38 в регистр 37 адреса постоянной памяти и прерва1шая микропрограмма продолжается. Выполнение микропрограммы обслуживания конечного состояния может быть прервало запросом на прерывание обслуживания зацеп ления по команде или запросом на передачу данных Вьшолнение микропрограммы обслу78

живания зацепления по команде может бытьлокальной памяти 34; извлекает следующее прервано запросом на передачу данных, поэ-управляющее слово канала из оперативной патому после выхода на микропрограмму обслу-мяти 32; выполняет зацепление по команде; живания зацепления по команде или конеч-загружает управляющее слово канала в ло ного состояния содержимое регистра 38 за- 5кальную память 34; восстанавливает содерписывается в ячейку локальной памяти 34,жимое регистров процессора 2О из локальсоответствующую вьшолняемой микропрограм-пой памяти 34. Микропрограмма обслуживания конечного

В конце вьшолнения микропрограммы , выполняет следующие действия:

обслуживания зацепления по команде или Kt.Разгружает содержимое части регистров пронечного состояния содержимое регистра ° локальную память 34; выполвосстанавливается из соответствующей вы- процедуру завершения операции вводаполняемой микропрограмме ячейки локальной ° «о - еливает содерж памяти 34, производится передача содерж - ,5па°мя Гз4 ° пропессора 2О из локальной мого регистра 38 в регистр 37 адреса пос-гтоянной памяти, и выполнение прерванной Р выполнении микропрограммы немикропрограммы продолжается. содержимое счетчика байтов

Выполнение микропрограммы обслужива- ™ ° «У™ « установлен

ПИЯ конечного состояния может быть прерва-го зацепления по данным, то микропрогно запросом на прерывание обслуживания за- переходит к выполнению зацепления пепления по команде или запросом на пере-иовледлс o e jriuwee уирав.-,г-fляющее слово канала из оперативной памяти

дачу данных. Выполнение микропрограммы „

г- г- I-32 и загружает его в регистры канала 21

обслуживания запепления по команде можетi гч л

быть прервано запросом на передачу данных, 25 локальную память 34. Эта пропоэтому после выхода на микропрограмму«««УР вызывает дополнительную задержку в

обсуживания зацепления по команде или ко- обслуживании запроса на передачу данных дру00 гого канала, а так как к каналу с меньшим нечного состояния содержимое регистра

„ адресом подключаются более быстродеиствузаписывается в ячейку .:окальнои памяти 34, соответствующую выполняемой микропрограм-зов конце выполнения микропрограммы об- данных канала с меньшим адресом наслуживания зацепления по команде или конеч- кладывает ограничения па скорость передачи ного состояния содержимое регистра 38 вое- Данных внешнего устройства, подключенного станавливается из соответствующей выполня-35 этому каналу,

емой микропрограммы ячейки локальной памя- целью увеличения пропускной способти 34. производится передача содержимогоности канала с меньшим адресом устройство

регистра 38 в регистр 37 адреса постоянной управления каналами содержит блок 7 памяти, и выполнение прерванной михропрог- формирования приоритетного запроса на раммы продолжается.40 микропрограммное прерывание,который раМикропрограмма передачи данных вьшол- ботает следующим образом.

няет следующие действия: разгружает содер Если при передаче данных канала с аджимое части регистров процессора 2О в ло- Ресом п было обнаружено зацепление но данкальную память 34; считывает управляющее ным, то микропрограмма записывает содерслово канала в регистры процессора 2О из 45 жимое регистра 38 в соответствующую адлокальной памяти 34; передает байт (груп- Ресу канала ячейку локальной памяти 34 и пу байтов) из оперативной памяти 32 в ка- переходит к процедуре выполнения зацепления нал 21 (22, 23) или из канала 21 (22, 23) по данным. Если при выполнении зацеплев оперативную память 32; модифицирует ад- ния по данным канала с адресом поступил рее данных и счетчик байтов через арифме- 50 запрос на передачу данных канала (п- 1), тическо-логический блок 33; записываетто блок 7 вырабатывает сигнал 56 приоримодифицированное управляющее слово канала тетного запроса, который через элемент в локальную память 34; восстанавливаетИЛИ 25 поступает в процессор 2О. Текунрежнее содержимое регистров информацией Щая последовательность микрокоманд произ локальной памяти 34.55 ueccopa 2О прерывается, и выполняется

Микропрограмма обслуживания зацепле-микропрограмма передачи данных канала с

ния по команде выполняет следующие деист- адресом (П - 1/.

вия: разгружает содержимое части регистровПосле вьшолнения микропрограммы перепроцессора 20 в локальную память 34; СЧЕ дачи данных прерванная микропрограмма тывает адрес управляющего слова канала из 80 продолжается.

52О592

по данным, т, е, извлекает следующее упоав-

ющие внешние устройства, то дополнительная

задержка в обслуживании запроса на В микропрограммах, обслуживающих каналы ввода-вывода, часто приходится обра щаться к ячейкам локальной 1 амяти 34, которые хранят управляющее слово канала или сохраняют содержимое регис1ров процессора 20. Обращение к той или иной ячейке локальной памяти 34 для извлечения (записи) управляющего слова каната зависит от адреса канала, микропрограмма которого вы- полняется в данный момент, а в зависимоети от типа выполняемого микропрограммно- го прерывания приходится запоминать (воестанавливать) содержимое регистров процессора 20 в (из) разных ячейках локальной памяти 34. Это обстоятельство вызывает дополнительные затрзаты времени для ана лиза адреса текущего канала и типа выпо/iняемого микропрограммного прерывания. Время вьшолнения микропрограмм, обслуживающих каналы ввода вывода, уменьшено за счет непосредственной адресации каналов ввода-вывода 21-23 к ячейкам локальной памяти 34, Это достигается тем, что устройство для управления каналами содержит блок 6 управления адресом локальной памяти. При обращении к ячейкам локальной памяти 34, где сохраняется содержимое регистров процессора 2О, блок 6 формирует один из трех базовых адресов локальной памяти 34, который через шины 18 адреса поступает в локальную память 34. Формирование базового адреса зависит от типа вьшолняемого микропрограммного прерывания, для этого содержимое регистра 24 признаков микропрограммного прерывания поступает в блок 6 управления адресом локальной памяти через шины 43 признаков микропрограммного прерывания. Формирование базового адреса локальной памяти 34 осуществляется по сигналу процессора 20, поступающему в бло 6 1лравлення адресом локальной памяти с управляющих шин 11 процессора 2О. Полный адрес ячейки локальной памяти 34 формнруется при помощи базового адреса и раэ рядов смещения. Разряды смещения угсазььвалотся в поле микрокоманды и поступают в локальную память 34 с управляющих щин 1 процессора В случае обращения к управляющему ело- ву канала блок 6 правления адресом локальной памяти ормирует багровый адрес. Формирование базового адреса в этом случа зависит от адреса канала, потенциалы которого поступают в блок 6 с выхода дещифратора 28 адреса работающего канала через шины 14 адреса канала Полный адрес ячей ки локальной памяти 34 формируется при помощи базового адреса я разрядов смеще-

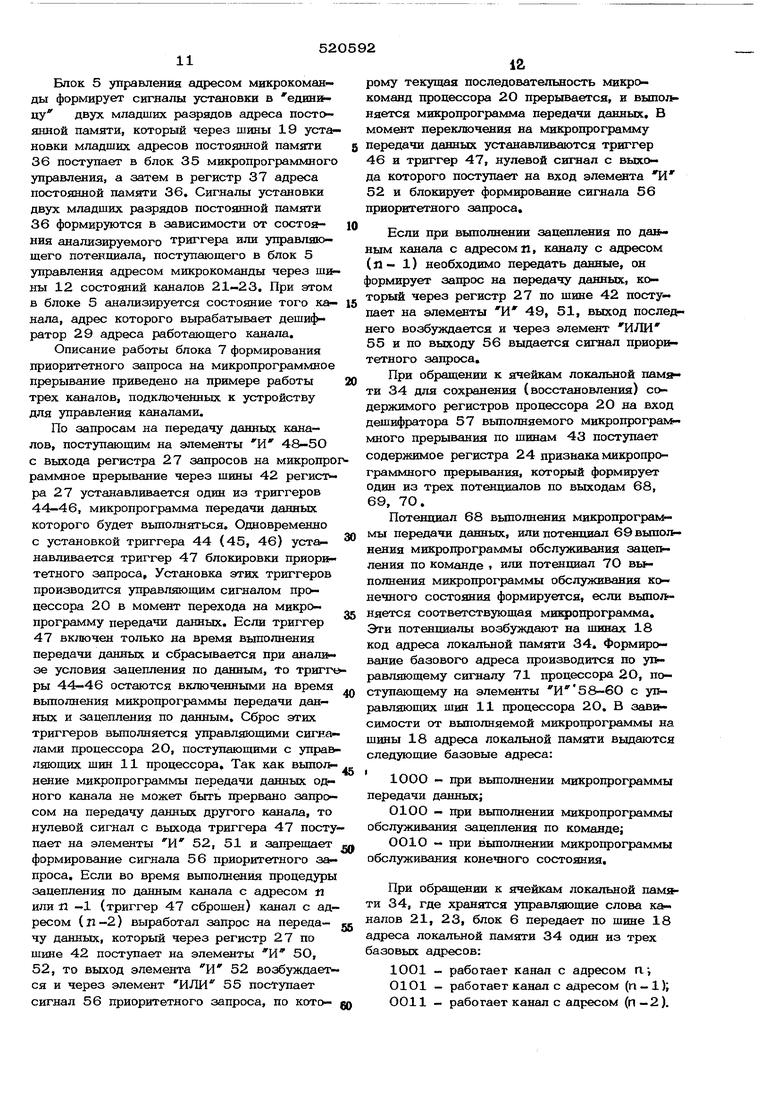

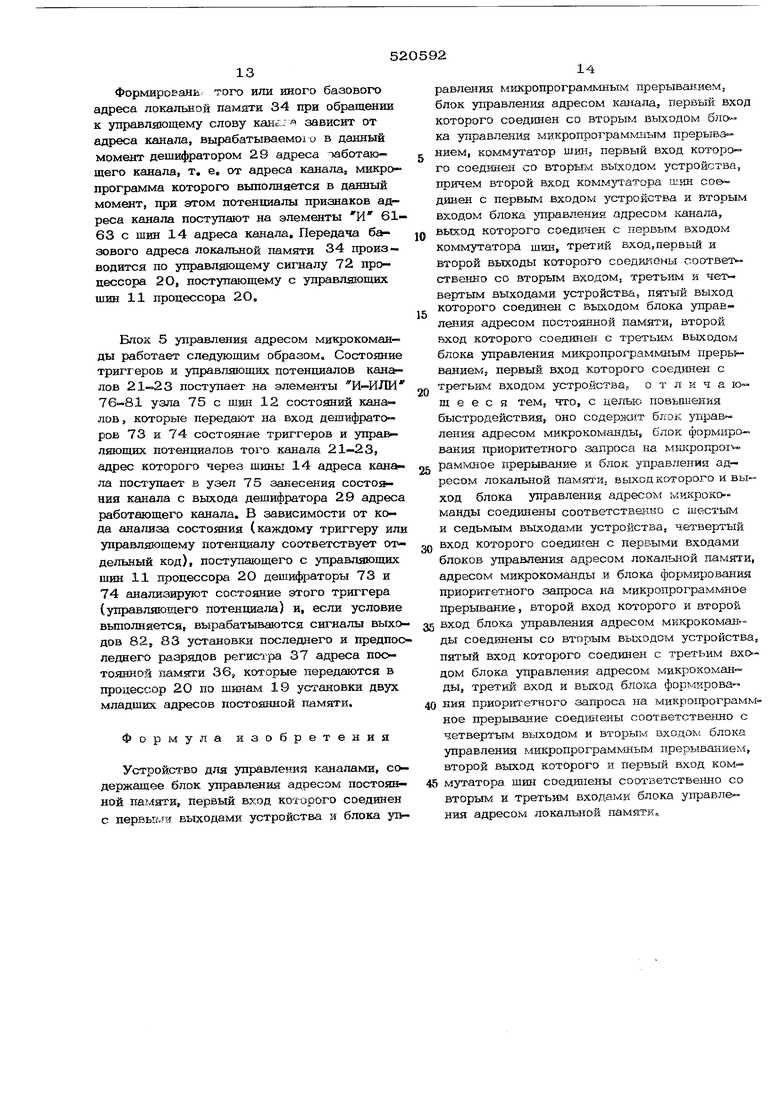

10 ния по сигналу процессора 2О, поступающему в блок 6 с управляющих шин 11 процессора 2О. Таким образом, введение блока 6 управле ния адресом локальной памяти позволяет использовать одни и те же микропрограммы при работе нескольких каналов ввода-вывода и увеличить пропускную способность каналов 21-23 за счет непосредственного Дос- тупа к необходимьп-л ячейкам локальной памяхи 34, в процессе выполнения операции вводавывода необходимо анализировать отдельные триггеры и управляющие потенциалы каналов 21-23, В зависимости от состояния анализируемого триггера или управлжошего потенциала производится переход к той или шюй. микрокоманде микропрограммы. Анализ триггеров и управляющих потен- циалов вьшолняется с помощью двух специальных полей условие один и условие два, содержащихся в микрокоманде. Разря.иность каждого поля зависит от чисел анализируемых Признаков (обычно каждое поле содержит четыре разряда). По каждой комбинаии этих полей анализируется один признак, . е, триггер или управляющий потенциал. Если в результате анализа признака, укаанного в поле условие один , обнаруживает я, что это условие вьшолняется, то последний разряд регистра 37 адреса постоянной памяти устанавливается Е единицу, если же это условие не вьтолняется, то последний разряд регистр. 37 адреса постоянной памяти 36 устанавливается . Анализ условий по полю условие два выполняется аналогично анализу поля условие один, но при этом устанавливается или сбрасывается предпоследний разряд регист- ра 37 адреса постоянной паыяп-и 36„ Таким образом, в зависимости от результатов анализа триггеров, указанных в поле условие один и условие г.ва, в микроко- манде можно осуществлять переход по одному из четырех направлений в микропрограмме Микрокоманда содержит только по одному полю условие один и условие два, а к устройству управления каналами подключается весколько каналов 21-23, поэтому необходимо анализировать адрес гого канала, микропрог рамма которого в данный момент вьшолняет ся и, естестганно, анализировать условия этого кналг. На такой анализ затрачивается дополнительное время, что в конечном итоге влияет на пропускную способность систегчсы ввода-вывода С целью сокращения времени обслуживания каналов ввода-вывода устройство для управления каналами содержит блок 5 управления адресом микрокоманды. Блок 5 управления адресом микрокоман ды формирует сигналы установки в единицу двух младших разр5вдов адреса постоянной памяти, который через шины 19 установки младших адресов постоянной памяти 36 поступает в блок 35 микропрограммного управления, а затем в регистр 37 адреса постоянной памяти 36. Сигналы установки двух младших разрядов постоянной памяти 36 формируются в зависимости от состояния анализируемого триггера или управляющего потенциала, поступающего в блок 5 управления адресом микрокоманды через шины 12 состояний каналов 21-23. При этом в блоке 5 анализиру ся состояние того канала, адрес которого вырабатывает деши-Ь ратор 29 адреса работающего канала. Описание работы блока 7 формирования приоритетного запроса на микропрограммное прерывание приведено на примере работы трех каналов, подключенных к устройству для управления каналами. По запросам на передачу данных каналов, поступающим на элементы И 48-5О с выхода регистра 27 запросов на микропро раммное прерывание через шины 42 регист ра 27 устанавливается один из триггеров 44-46, микропрограмма передачи данных которого будет выполняться. Одновременно с установкой триггера 44 (45, 46) уста навливается триггер 47 блокировки приоритетного запроса. Установка этих триггеров производится управляющим сигналом процессора 20 в момент перехода на микропрограмму передачи данных. Если триггер 47 включен только на время выполнения передачи данных и сбрасывается при анализе условия зацепления по данным, то тригго ры 44-46 остаются включенными на время вьгаоянения микропрограммы передачи данных и зацепления по данным. Сброс этих триггеров вьшолняется управляющими сигналами процессора 2 О, поступающими с управ ляющих шин 11 процессора. Так как выполнение микропрограммы передачи данных одного канала не может быть прервано запросом на передачу данных другого канала, то нулевой сигнал с выхода триггера 47 посту пает на элементы И 52, 51 и запрещает формирование сигнала 56 приоритетного запроса. Если во время выполнения процедуры зацепления по данным канала с адресом ц или « -1 (триггер 47 сброшен) канал с адресом (11-2) выработал запрос на передачу данных, который через регистр 27 по шине 42 поступает на элементы И 5О, 52, то выход элемента И 52 возбуждаетеся и через элемент ИЛИ 55 поступает сигнал 56 приоритетного запроса, по кото- рому текущая последовательность микрокоманд процессора 2О прерывается, и выполн няется микропрограмма передачи данных. В момент переключения на микропрограмму передачи данных устанавливаются триггер 46 и триггер 47, нулевой сигнал с выхода которого поступает на вход элемента 11 52 и блокирует формирование сигнала 56 приоритетного запроса. Если при выполнении зацепления по данным канала с адресом и, каналу с адресом (п- 1) необходимо передать данные, он формирует запрос на передачу данных, . « элементы И 49. 51, выход последгпает на элементы него возбуждается и через элемент ИЛИ 55 и по выходу 56 выдается сигаал приор&тетного запроса. При обращении к ячейкам локальной памяти 34 для сохранения (восстановления) ct держимого регистров процессора 2О на вход дешифратора 57 вьшолняемого микропрограммного прерывания по шинам 43 поступает содержимое регистра 24 признака микропрограммного прерывания, который формирует один из трех потенциалов по выходам 68, 69, 70. Потенциал 68 выполнения микропрограммы передачи данных, или потенциал 69 выполнения микропрограммы обслуживания задетьления по команде i или потенциал 7О вььполнения микропрограммы обслуживания конечного состояния формируется, если выполняется соответствующая мивропрограмма. Эти потенхшалы возбуждают на шинах 18 код адреса локальной памяти 34. Формирование базового адреса производится по управляющему сигналу 71 процессора 2О, поступающему на элементы И58-6О с управляющих шин 11 процессора 2 О. В зависимости от выполняемой микропрограммы на шины 18 адреса локальной памяти выдаются следующие базовые адреса: 10ОО - при выполнении микропрограммы передачи данных; 01ОО - при выполнении микропрограммы обслуживания зацепления по команде; ОО1О - при выполнении микропрограммы обслуживания конечного состояния. При обращении к ячейкам локальной памяти 34, где хранятся управляющие слова каналов 21, 23, блок 6 передает по шине 18 адреса локальной памяти 34 один из трех базовых адресов: 10О1 - работает канал с адресом п; О1О1 - работает канал с адресом (п-1); ООН - работает канал с адресом (п -2).

13

Формировали того или иного базового адреса локальной памяти 34 при обращении к управляющему слову зависит от адреса канала, вырабатываемого в данный момент дешифратором 29 адреса таботаю- щего канала, т. е, от адреса канала, микро программа которого выполняется в данный момент, при этом потенциалы признаков адреса канала поступают на элементы И 6163 с шин 14 адреса канала. Передача базового адреса локальной памяти 34 производится по управляющему сигналу 72 процессора 2 О, поступающему с управляющих шин 11 процессора 2О,

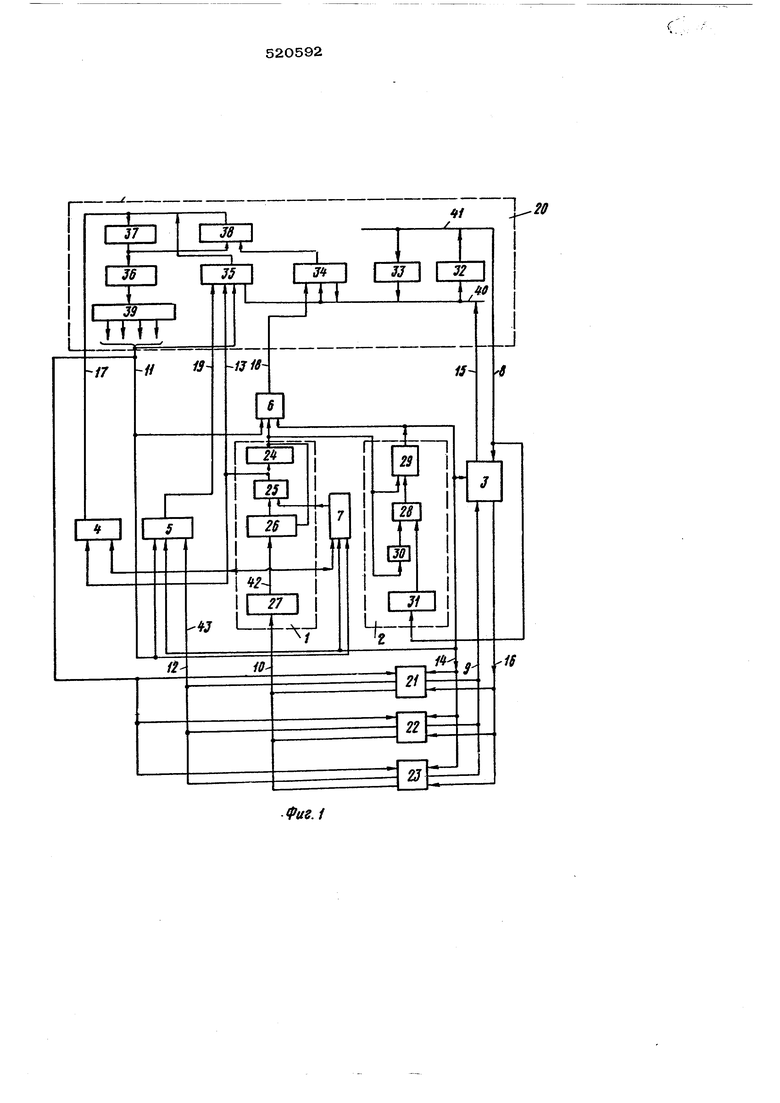

Блок 5 управления адресом микрокоманды работает следующим образом. Состояние триггеров и управляющих потенциалов каналов 21-23 поступает на элементы И-ИЛИ 76-81 узла 75 с шин 12 состояний каналов , которые передают на вход дешифраторов 73 и 74 состояние триггеров и управляющих потенциалов того канала 21-23, адрес которого через шины 14 адреса канала поступает в узел 75 занесения состояния канала с выхода дешифратора 29 адреса работающего канала. В зависимости от кода анализа состояния (каждому триггеру или управляющему потенциалу соответствует отдельный код), поступающего с управляющих шин 11 процессора 20 дешифраторы 73 и 74 анализируют состояние этого триггера (управляющего потенциала) и, если условие вьшолняется, вырабатываются сигналы выхо дов 82, 83 установки последнего и предпоследнего разрядов регишра 37 адреса поотоянной памяти 36, которые передаются в процессор 20 по 19 установки двух младших адресов постоянной памяти,

Формула изобретения

Устройство для управления каналами, содержащее блок управления адресом постоянной памяти, первый вход которого соединен с цервьн.тя выходами устройства и блока уп14

равления микропрограммным прерыванием, блок управления адресом канала, первый вход которого соединен со вторым выходом бло ка управления микропрограммным прорыва кием, коммутатор шин, первый вход которо- го соединен; со вторым выходом устройства, причем второй вход коммзтг-атора шин соединен с первым входом устройства и вторым входом блока травления адресом i-санала, выход которого соединен с первым входом коммутатора шин, третий вход, первый и второй вькоды которого соедиконы соответственно со вторым ВХОДОМ; третьим и чет вертым выходами устройства, П5ггый выход которого соединен с выходом блока управления адресом постозанной памяти, второй вход которого соединен: с третьим выходом блока управления микропрограммным прерьгванием. первый вход которого соед}юен с третьим входом устройства., о т л и ч а е е с я тем, что, с делью повъоленкя быстродействия, оно содерашт блок управ ления адресом микрокоманды, блок формирования приоритетного запроса ка м шропрог

пятый вход которого соединен с третьим вхо-дом блока управления адресом микрокоманды, третий вход и выход блока формкрова-40 ния приоритетного запроса на микрохгрограммное хферывание соещтекы соответствершо с четвертым выходом и вторым .входом блока управления микропрограмкшым прерыванием, второй выход которого и первый вход ком-

45 мутатора шин соединены соответственно со вторым и третьим входами блока управления адресом локальной памяти рам-ушое прерывание и блок управления адресом локальной памяти, выход которого и выход блока управления адресом микрокоманды соединены соответствекко с шестым и седьмым выходами устройства, четвертый вход которого соедш ен с первыми входами блоков управления адресом локальной памяти, адресом микрокоманды и блока формирования приоритетного запроса на микропрограммное прерывание, второй вход которого и второй. вход блока управления адресом мккрокоманды соединены со вторым вькодом устройства.

I

g

IJ/n

1

W

LSJ I

LL

ijie-17

-f

«/

32

ЛО

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления каналами | 1972 |

|

SU545983A1 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для управления каналами | 1976 |

|

SU641436A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Процессор ввода-вывода с коррек-циЕй ОшибОК | 1979 |

|

SU849221A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Процессор | 1984 |

|

SU1246108A1 |

Гс

Tl

2Г

I I I, . } .

iQ

L

«/СЮ

-J1

Щ

m

I L3J I

ч-

i2

iO/4

-/

S5

Й5

52

t

(

I 47

I. .«

I fn

ik

rn rn

50

и

«

Риг. 2

4 J

H

IS

иЛ

nrl

A

7

«

ft

4J

Фиг.З

Авторы

Даты

1976-07-05—Публикация

1974-06-24—Подача