1

Изобретение относится к цифровой вычислительной технике и может быть использовано для выиолнения микрооперации определения обратной величины числа.

Известио устройство, выиолняющее операцию определения отношения двух чисел. Однако это устройство не имеет достаточно быстрого действия. Наиболее близким к изобретению техническим решением является устройство, содержаш,ее п одноразрядных сумматоров, объединенных между собой иоследовательно шинами иереноса, л эле.ментов НЕ, выходы которых подключены к вторым входам соответствуюш,их одноразрядных сумматоров. Это известное устройство характеризуется низким быстродействием и большим количеством оборудования, вызванного наличием дешифраторов.

Целью изобретения является повышение быстродействия и упрош,ение устройства. В описываемом устройстве это достигается тем, что оно дополнительно содержит т одноразрядных сумматоров и k элементов И, причем доиолнительные т одноразрядные су.мматоры соединены между собой последовательно шинами переноса, выходы сумм дополнительных т одноразрядных сумматоров подключены к входам соответствующих элементов НЕ, выход переноса т-го пополнительного одноразрядного сумматора подключен к входу соответствующего элемента Hii, входные шины устройства подключены к соответствующим входам т дополнительных одноразрядных сумматоров и к входам элементов i-i, выходы которых подключены к входам соответствующих л одноразрядных сумматоров, две входные шины устройства подключены к входам соответствующих п одноразрядных сумматоров, выходы которых являются выходами устройства.

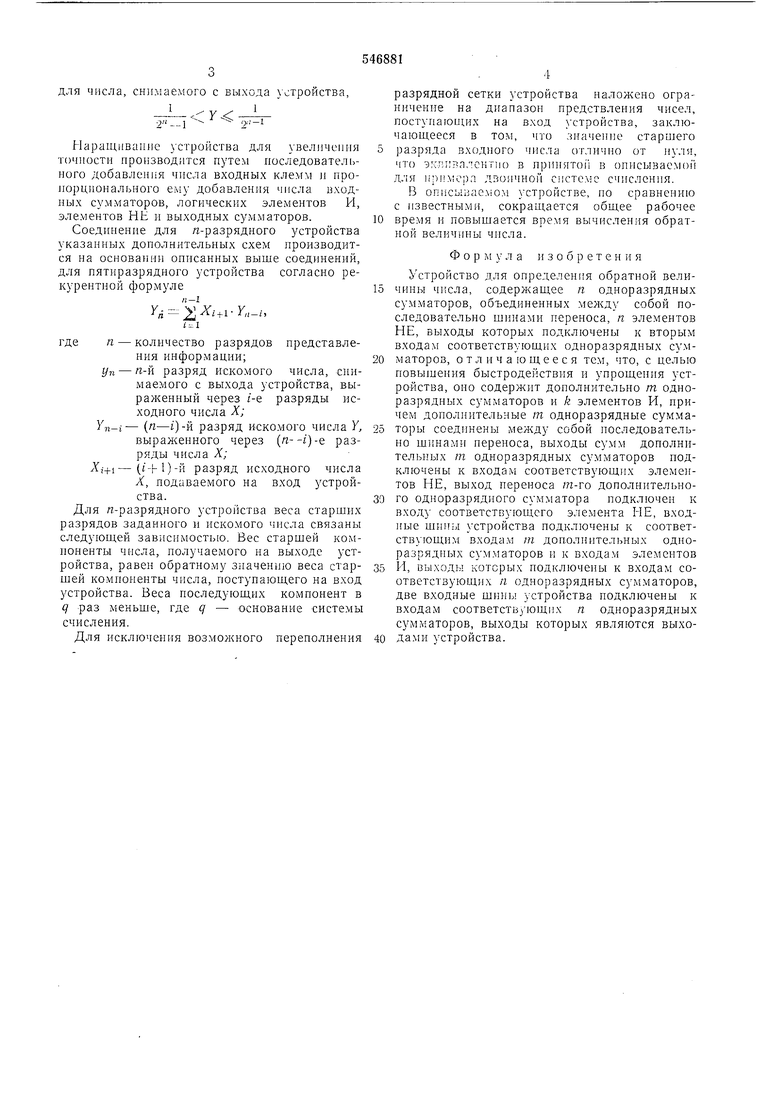

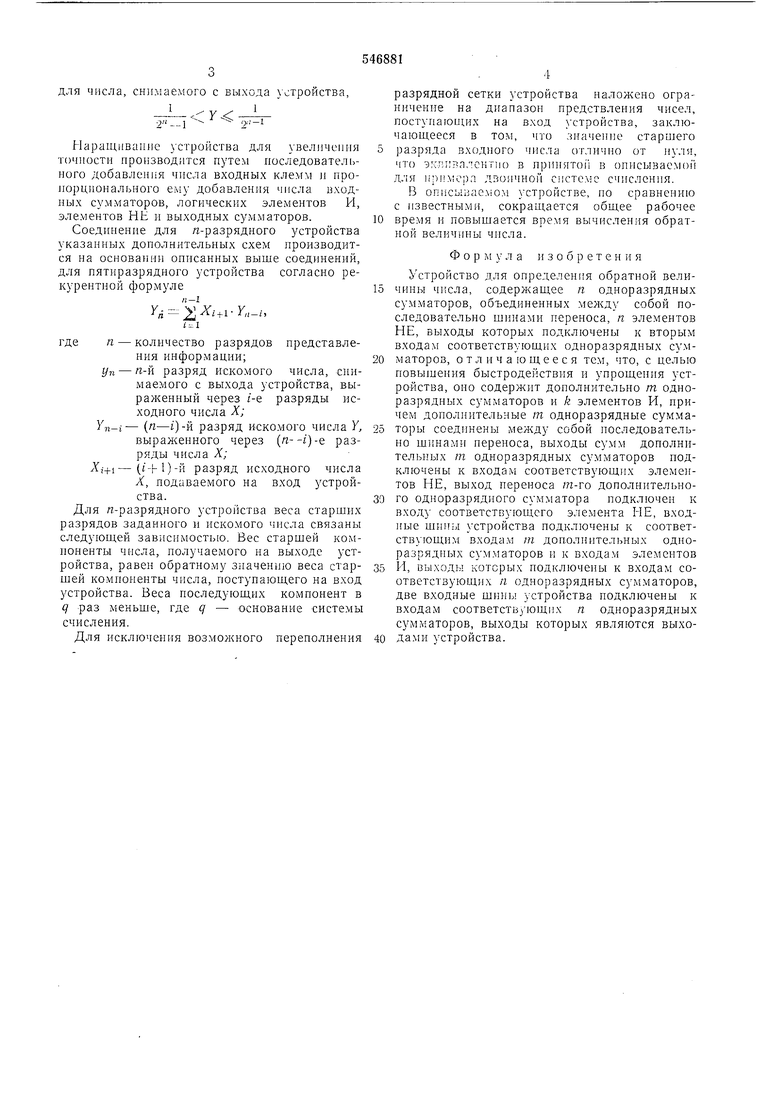

iria чертеже показана схема описываемого устройства и приняты обозначения: 1-9 - одноразрядные сумматоры; 10 и 11 - элементы И; 12-17 - элементы НЕ; 18-23 - входные шины; 24-29 - выходные шины.

Заданное число X, поданное на входные шины 18-23, поступает на входные сумматоры 7-9, логические элементы И 10 и И, элементы 12-17 и выходные сумматоры 1-6. По окончании переходного процесса в схеме устройства на шлнах 24-29 появляется значение кода числа X, равного обратной величине чис л а X.

Диапазон представления чисел для /i-paiрядного устройства: для входного числа

,

для числа, снимаемого с выхода устройства,

1 ,/ 7 L - - 2 Наращивание устройства для увеличения точности ироизводится путем гюследовательиого добавления числа входных клемм и пролорцноиальиого ему добавления числа входных сумматоров, логических элементов И, элементов НЕ и выходных сумматоров.

Соединение для л-разрядного устройства указанных дополнительных схем производится на основании описанных выше соединений, для пятиразрядного устройства согласно рекуреитиой формуле

.Y,,.n

i-I

где л-количество разрядов представления информации;

УП - п-й разряд искомого числа, снимаемого с выхода устройства, выраженный через г-е разряды исходного числа X;

Yn-i- (п-i)-H разряд искомого числа Y, выраженного через (n--i)-e разряды числа X;

Хг+1-(г-|-1)-й разряд исходного числа X, подаваемого на вход устройства.

Для л-разрядного устройства веса старших разрядов заданного и искомого числа связаны следующей зависимостью. Вес старшей комноненты числа, получаемого на выходе устройства, равен обратному значению веса старшей компоненты числа, поступающего на вход устройства. Веса последующих компонент в q раз меньше, где q - основание системы счисления. Для исключения возможного переполнения

разрядной сетки устройства наложено ограничение на диапазон предствлення чисел, поступаюн;их на вход устройства, заключающееся в том, что значение старшего

разряда входного числа отличио от нуля, что эк.т;пл.снт11о в принятой в описываемой для lipHMcpn двоичной системе счисления.

Е описываемом устройстве, по сравнению с известными, сокращается общее рабочее

время и повышается время вычисления обратной величины числа.

Ф о р м л а изобретен и я

Устройство для определения обратной величины числа, содержащее л одноразрядных сумматоров, объединенных между собой последовательно шинами переноса, п элементов НЕ, выходы которых подключены к вторым входам соответствующих одноразрядных сумматоров, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства, оно содержит дополнительно т одноразрядных сум у аторов и /г элементов И, причем дополнительные т одноразрядные сумматоры соединены между собой последовательно шинами переноса, выходы сумм дополнительных т одноразрядных сумматоров подключены к входам соответствующих элементов НЕ, выход переноеа т-го дополнительного одноразрядного сумматора подключен к входу соответствуюп1сго элемента НЕ, входные шины устройства нодключены к соответствуюшим входам т дополнительных одноразрядных сумматоров и к входам элементов

И, выходы которых подключены к входам соответствующих л одноразрядных сум.маторов, две входные шины устройства нодключены к входам соответствующих л одноразрядных сумматоров, выходы которых являются выходамн устройства.

i

4Е

PH

1 j

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения п-разрядных чисел в квадрат | 1979 |

|

SU911520A1 |

| Устройство для вычисления суммы квадратов К @ -разрядных чисел | 1981 |

|

SU993256A1 |

| Устройство для вычисления зависимости @ = @ + @ + @ | 1981 |

|

SU1019446A1 |

| Устройство для вычисления корней квадратного уравнения | 1980 |

|

SU999060A1 |

| Устройство для вычисления логарифмов чисел | 1980 |

|

SU932491A1 |

| Множительно-делительное устройство | 1980 |

|

SU920712A1 |

| Преобразователь кодов | 1973 |

|

SU526884A1 |

| -Разрядный паралельный сумматор | 1976 |

|

SU603991A1 |

| Арифметическое устройство | 1976 |

|

SU650074A1 |

| Устройство для возведения в квадрат п-разрядных двоичных чисел | 1978 |

|

SU699521A1 |

Г

f

jzz:I

fl

W

П

H26

i

гЗ г «, i8

ь

Y 24i

J I

Авторы

Даты

1977-02-15—Публикация

1974-09-16—Подача