1

Изобретение относится к области цифровой вычислительной техники, в частности, к суммируюпдим устройствам параллельного действия.

Известны комбинационные сумматоры параллельного действия с групповым переносом, в которых рационально строится схема формирования сигналов переносов, т. е. при сравнительно небольших затратах оборудования получают высокое быстродействие схемы 1, 2.

В сумматорах с групповым переносом формируются условия возникновения и распространения переноса. Вначале формируются условия для каждого разряда сумматора - условия нулевого порядка. В дальнейшем, в зависимости от разрядности сумматора и логических возможностей элементов, разряды сумматора делятся на группы первого порядка, каждая из которых объединяет несколько разрядов сумматора. Для каждой группы формируются условия первого порядка. Условия последующего второго порядка формируются с использованием . условий предыдушего первого порядка. В общем случае схемы формирования условий имеет /( последовательных каскадов, где каждый каскад - это схемы, формирующие условия одного порядка. Условия наивысшего /С-го порядка используются для последующего формирования групповых переносов этого же порядка. Групповые переносы К-го порядка используются для последзющего формирования групповых переносов (К-1)-го порядка.

Каждый каскад схемы групповых переносов (за исключением каскада нанвысшего К-го порядка) формирует групповые переносы с использованием групповых переносов предыдущего порядка и условий данного порядка.

При этом количество каскадов, формирующих групповые переносы, равно количеству каскадов, формирующих условия в группах. Групповые переносы 1-го порядка совместно с условиями нулевого порядка для всех разрядов одновременно формируют значение переносов из каждого разряда 3.

Известны сумматоры, в которых схема переносов из каждого разряда формирует значения переносов одновременно для всех

разрядов групп 2-го порядка, используя для этого значения условий 1-го порядка 4.

Наиболее близким по технической сущности к данному изобретению является суммирующее устройство, содержащее регистры

чисел и су.ммы, блоки выбора и преобразования операндов, формирования условий возникновения и распространения переносов для каждого разряда, формирования переносов для каждого разряда, двоичного су.ммирования, формирования условий возникновения и распространения переносов для групп разрядов, причем выходы регистров чисел и регистра суммы подключены к входам блока выбора и преобразования операндов, выходы которого соединены с первыми входами блока формирования условий возникновения и распространения переносов для каждого разряда, выходы которого подключены к первым входам блоков формирования условий возникновения и распространения переносов для групп разрядов, формирования переносов для каждого разряда и двоичного суммирования, вторые входы блока формирования переносов для каждого разряда подключены к выходам блока формирования условий возникновения и раснространения переносов для групп разрядов, а выходы - ко вторым входам блока двоичного суммирования, выходы которого подключены к первым входам регистра суммы, первые входы регистров чисел подключены к кодовым шинам чисел, а вторые входы регистров чисел и суммы подключены к первой тактовой шине, вторые входы блока формирования условий возникновения и распространения переносов для каждого разряда подключены ко второй тактовой шине 5J.

Обидим недостатком всех известных устройств является последовательный характер формироваиия как условий возникновения и распространения переносов, так и групповых переносов.

Целью изобретения является сокраш,ение времени формирования переносов путем уменьшения количества последовательных ступеней схемы формирования условий возникиовения и распространения переносов и отказа от схемы формирования групповых переносов.

Это достигается тем, что выходы блока выбора и преобразования операндов подключены ко вторым входам блока формирования условий возникновения и распространения переносов для групп разрядов, а сам блок формирования условий возникновения и распространения переносов для групп разрядов содержит узлы формирования основных и дополнительных условий, расположенные ступенями по одному узлу формирования основных и одному узлу формирования дополнительных условий в каждой ступени, причем входы каладого узла формирования основных условий подключены к выходам узла формирования основных условий предыдуш,ей ступени, входы узлов формирования дополнительных условий подключены к выходам узлов формирования основных и дополнительных условий всех предыдущих ступеней и к первым входам блока формирования условий возникновения и распространения переносов для групп разрядов, первые входы узлов формирования основных и дополнительных условий первой ступени подключены ко вторым входам этого блока, а вторые входы - ко второй тактовой шине.

выходы всех узлов формирования ocHOBilbiJi и дополнительных условий подключены к выходам блока формирования условий возникновения и распространения переносов для групп разрядов.

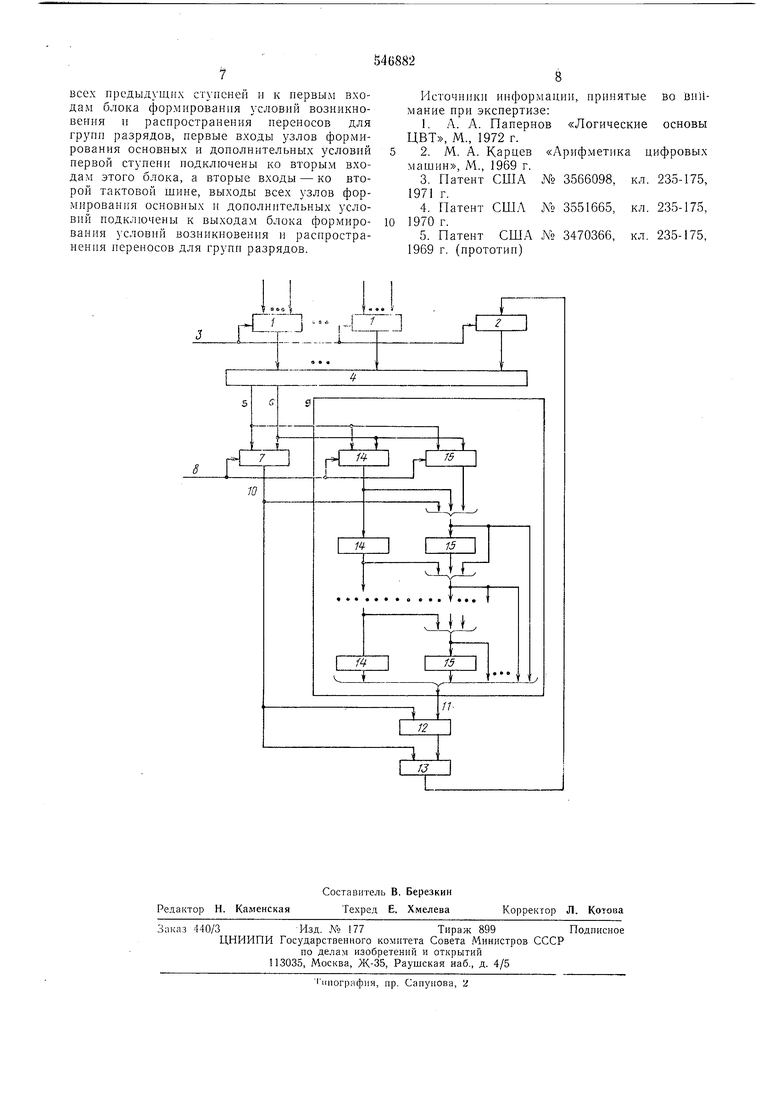

На чертеже показана блок-схема предлагаемого суммируюш,его устройства.

Устройство содержит регистры чисел 1, регистр су.ммы 2, первую тактовую шину 3,

блок 4 выбора и преобразования операндов, кодовые шины 5, 6 двух операндов, блок 7 формирования условий возникновения и распространения переносов для каждого разряда, вторую тактовую шину 8, блок 9 формирования условий возникновения и распространения переносов для групп разрядов, состояш,ий из нескольких последовательно переключаюш ихся ступеней, каждая из которых содержит узел формирования основных

условий и узел формирования фополнительных условий, причем первая ступень представлена регистрами, а вторая и все последуюш,ие - комбинационной логикой, выходную шину 10 блока 7, выходную шину 11

блока 9, блок 12 формирования переносов для каждого разряда, блок 13 двоичного суммирования, узел 14 формирования основных условий каждой ступени блока 9, узел 15 формирования дополнительных условий

каждой ступени блока 9.

Количество ступеней v блока 9 формирования условий для групп разрядов равно округленному в сторону увеличения logm

где п - разрядность суммируемых чисел,

/ - максимальная разрядность группы, условия для которой могут быть сформированы одной ступенью логических элементов, на вход которой заведены кодовые шины операндов,

т - максимальное число условий, из которых одной ступенью логических элементов может быть сформировано одно условие.

Узел 14 основных условий первой ступени формирует условия для групп разрядности

/1 6/1 0Разрядность групп, основные условия для которых формирует узел 14 любой г-й ступени (/ - 2,...., у) в Шг раз () больше разрядности групп, условия для которых формирует узел основных условий иредыдуш,ей (/-1)-й ступени, при этом количество групп, условия для которых формирует узел основных условий последней ступени, не превышает т.

Узел 15 дополнительных условий первой ступени блока 9 формирует условия для ряда групп разной разрядности, причем величина

каждой разрядности заключена в пределах между / и /1.

Узел 15 дополнительных условий каждой /-Й ступени (1 2,..., v) формирует условия ля ряда групп разной разрядности, причем

величина каждой разрядности является проМел уточной между разрядностями групп, условия для которых формируют узлы основных условий данной и предыдущей ступеней.

В общем случае количество разных разрядностей групп, условия для которых формирует узел дополнительных условий каждой стунени, достаточно для того, чтобы число основных и дополнительных условий для каждой группы, старшим разрядом которой является любой из п разрядов сумматора, а младшим - младший разряд сумматора, не превышало т.

Устройство работает следующим образом.

Регистры чисел 1 и суммы 2 запоминают данные в момент времени, определяемый синхронизирующим сигналом, подаваемым по первой тактовой шине. 3. Блок 4 выбора и преобразования операндов выбирает операнды из регистров чисел 1 и суммы 2 и производит их преобразование и предварительную обработку (инверсию, сдвиг и т. п.).

Сформированные блоком выбора и преобразования операндов два операнда по кодовым шинам 5 и 6 поступают в блок 7 формирования условий возникновения и распространения переносов для каждого разряда, формирующий условия возникновения и распространения переносов для каждого разряда в момент времени, определяемый синхронизирующим сигналом, поступающим по второй тактовой шине 8, а также на вход узлов 14 и 15 формирования основных и дополнительных условий первой ступени блока 9 формирования условий возникновения и распространения переносов для групп разрядов, формирующих условия для групп разрядов в тот же момент времени.

Ко входу каждого из узлов 14 формирования основных условий второй и всех последующих ступеней блока 9 формирования условий возникновения и распространения переносов для групп разрядов подключен выход узла 14 формирования основных условий предыдущей ступени, ко входам каждого из узлов 15 формирования дополнительных условий этих же ступеней подключены выходы узлов 14 и 15 формирования основных и дополнительных условий всех предыдущих ступеней блока 9 формирования условий возникновения и распространения переносов для групп разрядов и выходная шина 10 блока 7 формирования условий возникновения и распространения переносов для каждого разряда.

Выходы всех узлов 14 и 15 формирования основных и дополнительных условий, блока формирования условий возникновения и распространения переносов для групп разрядов объединены шиной 11.

Шины 10 и 11 подключены ко входам блока 12 формирования переносов для каждого разряда, формирующего переносы для всех п разрядов одновременно. Выход этого блока совместно с шиной 10 подключен ко входам блока 13 двоичного суммирования, где происходит формирование двоичной суммы, значение которой запоминается в регистре суммы 2. Время формирования переносов уменьшается за счет уменьшения последовательно соединенных ступеней образования значений условий возникновения и распространения переносов и значений групповых переносов, а следовательно, увеличивается быстродействие зстройства в целом.

Формула изобретения

Суммирующее устройство, содержащее регистры чисел и суммы, блоки выбора и преобразования операндов, формирования условий возникновения и распространения переносов для каждого разряда, формирования переносов для каждого разряда, двоичного суммирования, формирования условий возникновения и распространения переносов для групп разрядов, причем выходы регистров чисел и регистра суммы подключены к входам блока выбора и преобразования операндов, выходы которого соединены с первыми

входами блока формирования условий возникновения и распространения переносов для каждого разряда, выходы которых подключены к первым входам блоков формирования условий возникновения и расиространения

переносов для групп разрядов, формирования переносов для каждого разряда и двоичного суммироваиия, вторые входы блока формирования переносов для разряда подключены к выходам блока формирования

условий возникновения и распространения переносов для групп разрядов, а выходы - ко вторым входам блока двоичного суммироваиия, выходы которого подключены к иервым входам регистра суммы, первые входы

регистров чисел подключены к кодовым шинам чисел, а вторые входы регистров чисел и суммы подключены к первой тактовой шине, вторые входы блока формирования условий возникновения и распространения переносов для калчдого разряда подключены ко второй тактовой шине, отличающееся тем, что, с целью сокращения времени формирования переносов, выходы блока выбора и преобразования операндов подключены ко

вторым входам блока формирования условий возникновения и распространения переносов для групп разрядов, а сам блок формирования условий возникновения и распространения переносов для групп разрядов содержит

узлы формирования основных и дополнительных условий, раснололсенные ступеням ; по одному узл} формирования основных и одному узлу формирования дополнительных условий в ступени, причем входы кал :дого узла формирования основных условий подключены к выходам узла формирования основных условий предыдущей ступени, входы узлов формирования дополнительных условий подключены к выходам узлов формироваиия основных и дополнительных УСЛОВИЙ

всех предыдущих ступеней и к первым входам блока формирования условий возникновения п распространения переносов для групп разрядов, первые входы узлов формирования основных и дополнительных условий первой ступени подключены ко вторым входам этого блока, а вторые входы - ко второй тактовой шине, выходы всех узлов формирования основных и доиолн1 тельных условий подключены к выходам блока формирования условий возникновения п распространения переносов для групп разрядов.

Источники информации, принятые во внимание при экспертизе:

1. А. А. Папернов «Логические основы ЦВТ, М., 1972 г.

2. М. А. Карцев «Арифметика цифровых машин, М., 1969 г.

3.Патент США № 3566098, кл. 235-175, 1971 г.

4.Патент США К° 3551665, кл. 235-175, 1970 г.

5.Патент США N° 3470366, кл. 235-175, 1969 г. (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1981 |

|

SU1018113A1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| Конвейерное устройство для одновременного выполнения арифметических операций над множеством чисел | 1977 |

|

SU922726A1 |

| Арифметическое устройство | 1976 |

|

SU656059A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

Авторы

Даты

1977-02-15—Публикация

1974-10-28—Подача