вьйсод - с первым входом первого регистра частйчнь1х сумм, четве1ртый выход - С входом второго регистра частичных сумм,выход первого дополйительного элемента И сое цинён с вторЬ1м входом регистра приращений, выход которого подключен к пе эвому входу второго дополнительного элемента И, вьгход которого подключён к первому входу второго дополгательйого элемента ИЛИ, выход второго дополнительного элемента ИЛИ соединен с вттзрьйу входом второго сумматора, выход которого соединен с первым входом второго элемента задержки, первый вход третьего Дополнительного элемента И соединен с первым выходом второго регистра подынтёграл15ной функции, а выход - с первым входом тре тьего дополнительного элемента ИЛИ, выход которого соединен с первы входом элемента И-НК, выход третьего э71ёМента эадёрж :и соединен с входом второго дополнитёл ьного эЛемента ИЖ и с четвертым входом формирователя приращений, выход которого подключен к первому входу четвертого дополнительного элемента И ик первому входу первого элемента задер жки, первый вход третьего элемента задержки соединен с пёрвого сумматора, выход четвертого дополнительного элемента И соединен с вторым входом третьего дополнительного илемента ИЛИ, выход первого дополнитель746602

ного элемента ИЛИ подключен к втором входу элемента И-НЕ, первьш вход пятого дополнительного элемента И соеДинен с вьгходом второго регистра частичных сумм., а выход - с третьим входом третьего элемента Р1ЛИ, первый вход четвертого дополнительного элемента ИЛИ соединен с выходом первого элемента задержки, второй вход - с ввыходом седьмого элемента И, а выходс вторым входом второго регистра частичных сумм, первьй вход пятого дополнительного элемента ИЛИ соединен с выходом второго элемента задержки, второй вход с выходом четвертого элемента И, а выход - с вторым входом первого регистра частичных сумм, выходшестого дополнительного элемента ИЛИ соединен с вторым входом пятого элемента И, третьи входы первого регистра частичных суМм и второго регистра подынтегральной функции являются информационными входами устройства, вторыевходы первого, второго, третьего, четвертого, пятого дополнительных элементов И, второй вход первого дополнительного элемента ИЛИ, первый, второй входы шестого дополнительного элемента ИЛИ, вторые входы всех элементов задержки, пятый вход формирователя приращений, шестой и седьмой входы формирователя частного являются управляющими -входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующее устройство интегрирующей машины последовательного типа | 1974 |

|

SU526927A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Интегро-арифметическое устройство | 1979 |

|

SU783813A1 |

| Интегро-арифметическое устройство | 1977 |

|

SU744654A1 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| Цифровой интегратор для воспроизведения многомерных функций | 1974 |

|

SU519736A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ЦИФРОВОЙ МОДЕЛИ | 1967 |

|

SU223472A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

ЙНТЕГРОАРИФМЕТИЧЁ КОЁ УСТ-т РОЙСТВО, содержащее экстраполятор, сумматоры, формирователь приращений, элемент Й-НЕ, выход котброго соединен с первым входом Первого сумматора, первый и второй регистры подынтегральной функции, регистр прира щений, элементь ИЛИ, И, первый и . второй регистры частичнызс сумм, при-; чем к первому и второму входам первого элемента ИЛИ подсоединены соответственно первые выходы первого и ; второго регистров подынтегральной функ1Ц1и, а.выход первого элемейта :;.; ИЛИ подключен к це рвому входу форми- : рователя приращений, к первому входу второго суютатора, первый вход первого элемента И подключен к выходу первого элемента ИЛИ, вьпсод - к первому входу второго элемента ИЛИ, - . выход которого соединен с первыми входами регистров подынтегральной функции, первый вход второго элемент: та И соединен с вькодом второго сумматора, а выход - с вторым входом второго элемента ИЛИ, первый вход третьего элемента К подключен к вьг ; ходу первого сумматора, а выход соединен с первым входом экстраполлтора,, первый вход четвертого элемента И подключен к выходу первого сумматора, выход первого регистра частичных сумм подключен к первому входу пятого элемента И, выход которого пЬдклкг Чён к nepBcfMy входу третьего элемента ИЛИ, вьпсод которого С01едине1€ с вторым входом перйого сумматора, вь ход второго регистра частичных сумм подклйЧ|ен к первому входу шестого элемента И, выход которого подклйчен к второму входу третьего элемента ИЛИ, пёрйый вход седьмого элемента И подключен к первому выхдду первого регистра частичных сумм, второй и третий входы формирователя приращений, вторые вхЬды pierMCTpoB подынтегральной функции р еги бтра приращений и экстрапоЛятбра являются информационными входаьда устройства, вторые входы первого, второго, третьего. i Четвертого, шестого и седьмого элеMeitTOB И являются управляющими )вхоДа(Л йи устройства, вторые выходы регист-;. ров подынтегральной функции, первый выход регистра приращё:ний и выход - экстраполятора являются информационными вьрсодаьш устройства, о т л кча ю щ ё е с я . i-eM, что, сцеЛью повышения быстродействия, в него дод; полнительно введены формирователь о частного, элементы И, ИЛИ и элемен а: ТЬ задержки, причём первый вход форо мирователя Частного соединен с треt 9 тьим выходом второго регистра подЫнтегральйой функции, второй вход с выходом- первого сумматора, третий и четвёртый - с выходами первого и второго элёмёнто в задержки, соответственно пятый вход - с вторым выходом цёрвого регистра Частичных сумм, первый выход формирователи частного соединен с первым входом первого дополнительного элемента И, второй выход - с первьм входом первого дополнительного элемента ИЛИ, третий

f

Изобретение относится к области вычислительной техники и Может быть использовано з цифровых вычислительных комплексах, работающих в системах управления с высокими требованиями к скорости выполнений вь1ЧйЬлений. -,

Целью изобретения является повыraeiiMe быстродействия.

На чертеже представлена блок- схе ia йнтегро-арифмётическогЪ у р сйства,

Устройство включает первый и второй регистры 1 и 2,подь1нтегральной функции; первый сумматор 3, второй

г е - г : .

.сумматор 4, регистр 5 приращений, формирователь 6 приращений, формирователь 7 частного, элемент И-НЕ 8, элементы 9, 10 задержки. первый и второй регистры 11,

ли, первый и второй регистры ii, 12 частичных сумм, экстраполятор 13, элементы И 14-20, элементы ИЛИ 2123, дополнительные элементы И 24-28, дополниТегГёные элементы ИЛИ 29-34 Л. и элемент задержки 35.

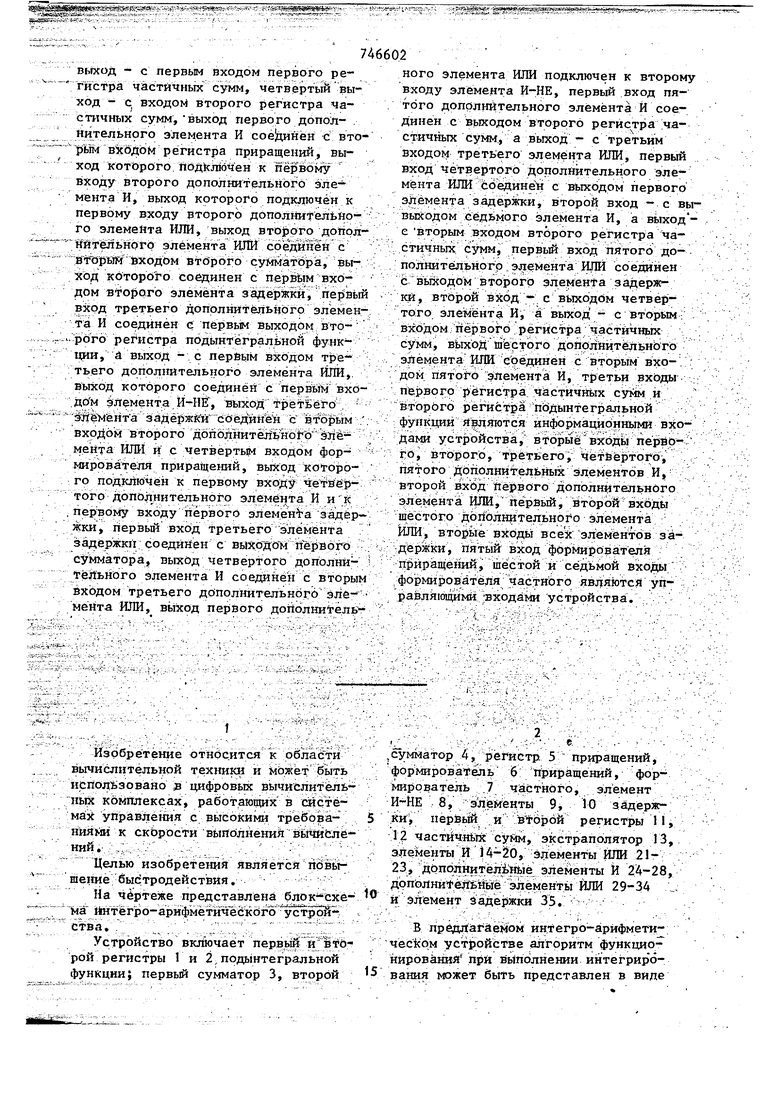

В предлагаемом интегро-арифмети-; 4eckoM устройстве алгоритм функционирования при выполнении интегрир6вания может быть представлен в виде ПрП-М1±11,еслиГ К; ,gypr(i4-l) ДУ „ vyp (i+1) Прг

ГТ)

m Vyk(i-ti.) ,

ЕВ:

АУ

,( 7S(5r(i+l) t,Spqj(i+l). ,nzk tr uy ДД VSgr(i-fl) . ЛУAy . где Прг, Ilqr - коммутационные призна ки выборки приращений леременньк Ур и yiq в г-ом интегрировании; ург(1+ +1) - значение подынтегральной функ ( i+ГУ ции ург в точке i + 1; -- :. . vyqr(i+l) . . - квантованные приращения а У . - . . . . ттодынтегральной функции и переменной интегрирования соответственно в точке i + 1; Y - квант подынтегральной функции; - - некванто - . (У . - ванное приращение интеграла, вычисленного в интегрировании в точvSgr(H-l) ке (i+1); - частичная сумма неквантрванных приращений ин ,..v VYk(i+l) тегралов в точке (i+i); -: .. . .,неквантованнре приращение переменной yk в точке (i+1); - много, - V . . . разрядное квантованное приращение пе ременной yk в точке (i-H); п - количество разрядов приращеШй в режиме vTk(i+2) короткой разрядной сетке; Ay . квантованное экстраполированное при ращение переменной yk в точке 1+2, Устройство работает следующим образом. Вычи ели т ел ьньй проц е ее выпол нения одной операции интегрирования в (i +1)-ом щаге решения. Выполнение операции начинается после поступпенйя из запоминающего устройства приvypr(i+l) в регистр приращен ращения ЛУ Vyq

vypr(i-tj.)

НИИ 5,

В формирователь

:У „ Vyq(i+l) nqr если q k j r(i+l) ДУ nqrmiiil.если q. Ч. uy. приращений 6. Подынтегральная функция ург (при короткой разрядной сетке-) или мпадщие разряды подынтегральной функции ypri (при удвоенной разрядной сетке) Поступают в первый регистр I подынтегральной функции. Старшие разряда подынтегральной функции ypri при удвоенной разрядной сетке поступают во второй регистр 2. п . , vyprd+i-oi) Подынтегральная функций . лу . (об 0,1,...,т-1, гд1е m - шаг экстраполяции) поступает в формирователь приращений 6. Кроме того, при выполнений экстраполяции и квантования в экстраподятор 13 из ЗУ поступают осOyki . vyk(i-ft.) таток V- и приращение :-- (об- 1,2,...ут). , После занесения необходимой для начала вйгчислений информации значение ординаты при короткой разрядной еетке или.младшие разряды ординаты прк удвоенной разрядной сетке с выхода первого регистра подынтегральной функции 1. и старпше разряды ординаты, при вычислениях и удвоенной разрядной с1еткой с выхода второго регистра подынтегральной функций 2 поступают через первый элемент ИЛИ 21 на первьй вход еумматбра 4. Одновре- менно на В ТОрой вход первого еумматора 3, поступает с выхода регистра приращения 5.через дополнительньй гмхемент И 25 при отсут(твии признака деления Hd и элемент ШШ 30 прираще- . НН6 -л у- С выхода сумматора 4 новое значение подынтегральной функции при; наличии признака формирования нового значения подынтегральной функции Цург поступает на первый и второй регистры функций 1.и 2. В случае наличия инверсии признака Itypr неизмеишле разряда подынтегральной функции переписываются в первый и второй регистры подынтегральных функций 1, 2. Вместе с этим разряды подынтегральной функции направляются в формирователь приращений интеграла. Полученное на -выходе формирователя приращений 6 приращение v fy передается на первьй вход элемента И-НЕ 8, где умножается на коэффици-ент (-l)nzkj при наличии признака иивёрсии приращения интеграла ITzj, поступающего на второй вход элемента Й-НЕ 8. Величина Ou li±li() , йу с выхода последнего направляется на первьй вход сумматора 3 и складывается с накопленной в предыд тцих .операциях суммой неквантованных приращений интегралов, поступагацей на второй вход сумматора 3 с выхода пер вого регистра М частичных Сумм при наличии инверсии признака удвоенной разрядной сетки Пус, При вычислениях в режиме удвоенной разрядной сетке (Пус 1) содержимое первого регистра Г1 частичных сумм поступает во .второй ре;гистр 12 час тачных сумм, При наличии инверсии признака nfkr окончания формирования переменной ; : YSGr(i+0 интегрирования сумма с . выхода сумматора 3 приходит в первый регистр 11 частичных сумм, а через иегО при удвоенной разрядной сетке (Цус 1) - во второй регистр 12 частичных сумм и запоминается до следующей операции интегрирования. При наличии признака nfkr окончания формирования переменной интегрироваvyk(i+) с выхода сумния величина

1, если sign у sign Z;. - 1,3,5,.,,

0,если sign Zi. ..- -; .

1,если signLZ;-J , ./:.....

Oj если sign : . .. 2 Zi,,+ y, если sign z;.,

2 Z;., - y-, если sign y sign z,. 1 1,2,3,

ZL 2 Z. + у

«2

;r 2 Z{, - у

R + y, ес.ли sign y sign Н

z, R - у, если sign у sign R.

7Д6602 матора 3 поступает в экстраполятор 13. По окончании операции в ЗУ заносятся значения ypri при Пург 0. или ypr(i+l) при Пург - 1,поступающие с выходов первого и второго регистров подынтегральной функции 1 и 2, . vylt(i-H) и ( значения - v|k(i±2) . Hfkr 1 и приращению поступающие в ЗУ из экс.траполятора 13, После записи результатов операции из ЗУ выбирается информация, необходимая для выполнения следующей one- . рации интегрирования. Выполнение этой операции аналогично предыдущей, Для выполнения в ИДУ операций деЛёния используется алгоритм без восстановления остатка, при котором частное от деления двух чисел произвольного знака, где R - делимое, Y - делитель, удовлетворяющих услоR 1, равно - 1 - у 0 v-z прйчем-Хд, х,/, ,,, равны 1 или О, Деление является многоциклрврй операцией, в каяодом цикле определяется однацифра частного, -. В предлагаемом интегро-арифмети- : ческом устройстве осуществляется .: ускорение выполнения деления за счет . вычисления двух цифр частного, в одном цикле операции. Выполнение операЦии деления в ИДУ производится по елeдyющё y алгоритму: где Zj, - первый остаток от деления полученный в i-OM цикле операции; второй остаток от деления полученньй в i-ом цикле операции; первая цифра ча,стного, о(5т раз рванная в i-гом цикле операции; вторая цифра частного, об разованная в i-ом цикле . Операции. ; Рассмотрим процесс вьтолнения Опе раций деления в предлагаемом ИАУ . Перед началом о перации; из ЗУ вр второй регистр 2 подынтегральной функции и в первый регистр j1 частичных сунм с Bbixo a ЗУ считываются коды де лителя в делимЬго соответственно, а регистр приращемнй 5 используется; .для записи частного. В сумматоре 3 формируется первый в цикле PC таток ,, . Ускорение выполнения делённая Ъ достигается путем структурногр рас-: параллёливания вычислений Приведенно го вьтшё алгоритма. В связи с этий необходимр вычи У1ёнйе остат1сов Z j;| . и Zjjj, совмеща-гь йо времени Так как в начале операции fще не сфррмирбван знак перврго рстатка Z; и невозмЬяр HP пррвёрйть условие sign i : - },3 йозврлякйцёе определить с каким знаком необходимо подавать делитель в суммато р для Рбразования рстатка: Z} , в cy iмafppё 4 и фЬрмиррвателё приращений 6 вычйсдяют;СЯ 2 Zj + Y и Z:, остатки Z;, MV - J- . t 2 Z:, - f ,,, - X соответственнр. BepHbA PcraTPic Рпределяй)СЯ пбслё получений знака sign Zj,-. Запрмйнаниё вычиси Zjj п|)ризвдленнь)х рстаткрв Z дится в перврм и втором регистрах ; частичных сумм сортвётс-гвенйо Как следует из апгр|5йтма запо14Инаниё остатка Z,;, не производится, хранени знака его осуществятётся в форми роватёлё частного 7. Занесение остатков zf- и Zlrt в первый и второй . регистры II, 12 частичнь1Х осуще П1ествляётся со. сдви1;6й в; сторойу старших разрядои на один такт 4ei|)e3 элементы задержки 9 и 10, благодаря чему производится умножение их на коэффициент 2 и в регистры И, 12 записываются значения: величин 2 Zl и 2 Z; . Старшие разряды остатков зaпo данaioтcя на элементах задержки 9, 10 и исНользуются в формироратёле частного 7 для определения верного остатка по следующему алгоритму: R.j ndr V Па& R1, -:R- ;, . .... . (1, если sign у sign Z;, . .--.: ;.... - -. .. :.. .- о, если; sign у sign Z;, Сформйрованны ё в формирователе частного 7 сигналы; сбросов или zJa управляют сбросом лржтк Рстаткбв Z или , записанных в регистpax П, 12 частичных сумм. Образбв аниё значения остатка ZT оеуществляётся в формирователе прирйщёний 6, с целью на егр третий вход подаётся; код делителя с Sir хода второго регистра 2 подынтегральной функции, начетвертый - с выхода сумматора 3 через элемент з адёржкн 9, Удврейньй остаток 2 Z, , а на пяттьй вход - п ризнак операции деления lid. По признаку деления в формирователеприращений организуется HHisepсия кода дейителяу В элементе И-НЕ 8 инверсия Кода делителя выполняется л ТОЛЬКО при надтйчии сигнала инверсий Дёлитёйя nz(J,i вырабатываемого в фОрмйрговатБле Частного 7 при вьтолнении слёдуйщих у.слошйг- ;: ; ,;. ; ; .-;, . ;;;nzd.l, ecJiBi..sign , .- :. ..л-:;;: sign у при nd, о й,;еслй sign Rj - sign у при . )0ванне цифр : частного осу- щёствляет формирователь частного 7, в КазкдОм цикле образуются пара цифр ч стиого, которые с первог о выхода блок Ф Р ироВйийя частного перёзаписываютсгя в регистр приращений 5. Сформированный kojEi частного nepeira сьшаётСЯ с вЦхрДй регистра приращенйй;;5;в--ЗУ.,-;: . л. , .;. Использование предлагаецргрустpoftcTBia ho3BOJMeT увеличить скорость рёйёния задач, имеюпщх смещёнчьй Характер №гчйслейия(непрерывнь1й и точечный), реализуе;мых в вычислитель- ; ных комплексах систем управления динамическими объектами.

f, -

Авторы

Даты

1980-07-05—Публикация

1977-01-24—Подача