1

Изобретение относится к области вычислительной техники и может быть использовано для реализации нелинейных зависимостей в управляющих и гибридных вычислительных системах.

Известно многоканальное устройство реализации нелинейных зависимостей для гибридных вычислительных машин 1, построенное на базе запоминающего устройства с регистром адреса, преобразователя, схем сравнения, элементов И, реверсивных счетчиков.

Недостатком устройства является ручной набор схемы реализации нелинейных зависимостей, что в значительной степени снижает производительность и коэффициент использования устройства.

Известно также наиболее близкое по техиическому решению к изобретению устройство для совместной работы цифровых и аналоговых машин 2J, содержащее регистр адреса, вход которого подключен к первому входу устройства, а выход-к входам блока памяти функций и цифро-аналогового преобразователя, выходом связанного с первым входом первой схемы сравнения, второй вход которой соединен с вторым входом устройства, а выход-с входом шифратора. Выходы блока памяти функций подключены к первому входу коммутатора, вторым входом связанного с

выходом регнстра адреса, а выход коммутатора - к входу блока реверсивных счетчиков, выход которого через блок вывода соединен с выходом устройства.

Однако такое устройство не обеспечивает автоматизации выбора заданного вида нелинейной зависимости для данного входа и вывода ее на требуемый выход, что значнтельно снижает производнтельность системы в целом.

Цель изобретения - повышение производительностн системы за счет автоматическо коммутации входов устройства, выходов блока памяти фуикцпи и входов реверсивных счетчиков, т. е. выходов лстройства.

Это достигается тем, что в устройство введены блок памяти адресов, регистр вида функций, регистр адреса нелинейностей, вторая и третья схемы сравнения, причем выходы блока памяти адресов соединены с входами регистров вида функций и адреса иелинейностей, а выходы этих регистров - с иервыми входами соответственно второй н третьей групп схем сравнения, вторые входы которых связаны с выходом шифратора, выходы второй и третьей схем сравнения подключеиы к третьему и четвертому входам коммутатора.

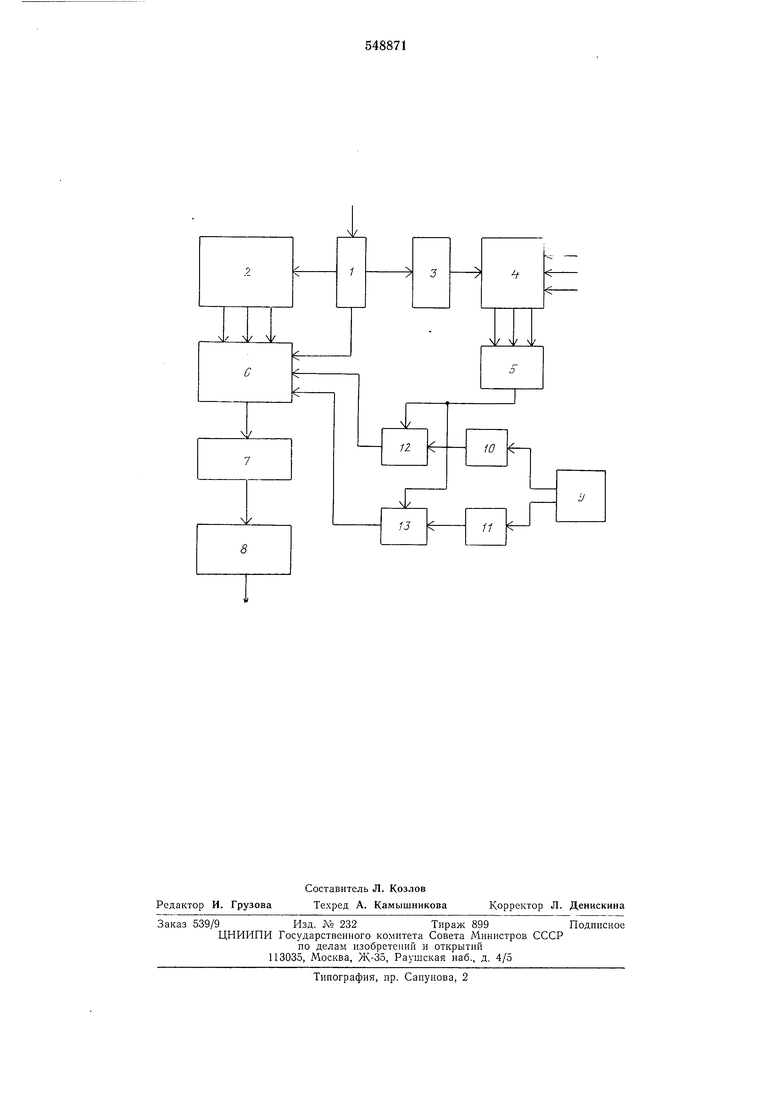

Блок-схема устройства представлена иа чертеже.

Она содержит регистр 1 адреса, блок 2 памяти функций, цифро-аиалоговый преобразователь 3, первую схему 4 сравнения, шифратор 5, коммутатор 6, блок 7 реверсивных счетчиков, блок 8 вывода, блок 9 памяти адресов, регистр 10 вида функций, регистр 11 адреса нелииейностей, вторую 12 и третью 13 схемы сравиения.

Устройство работает следующим образом.

Регистр 1 выполнен в виде кольцевого счетчика, который в соответствии с тактовыми импульсами, поступающими на первый вход устройства, последовательно формирует адреса всех ячеек блока 2. В блоке 2 записаны через равные интервалы по аргументу приращения всех нелинейных зависимостей, количество которых соответствует разрядности блока 2. В соответствии с адресами, формируемыми в регистре 1, осуществляется считывание информации, в виде приращений функций, из блока 2, которая иоступает на коммутатор 6. Связь регистра 1 с коммутатором 6 предиазначеиа для определения направления приращения по аргументу, для чего в коммутаторе анализируется предыдущее и текущее состояния двух младщих разрядов регистра 1, и если их состояние изменилось в сторону уменьшения, происходит инвертирование информации, считываемой из блока 2 по данному каналу. Коды из регистра 1 поступают также на цифро-аналоговый преобразователь 3, на выходе которого при этом формируется ступенчатое напряжение развертки, которое с помощью схемы 4 сравнивается с входными величинами. Импульсы сравнения со схемы 4 с помощью шифратора 5 преобразуются в порядковые номера соответствующих схем сравнения. Блок 9 устанавливает соответствующие коды в регистры 10 и 11.

При сравнении кодов с шифратора 5 с кодами, заданными в регистрах 10 и И, вырабатываются импульсы, управляющие коммутатором 6. Импульсы, поступающие на коммутатор 6, управляют подключением требуемой фуикции из блока 2 и выбранных функций на заданные входы блока 7.

Если, например, в устройство поступают переменные х, xz, хз, х, ..., а в разрядах ячеек блока 2 записаны приращения нелинейных зависимостей Sin х, Cos х, logz х, е, и необходимо на третий выход устройства подключить нелинейную зависимость е- , то код 002 (х2) выдается из блока 9 на регистр 10 (е-) в на регистр И. Аналогично осуществляется

выбор вида функции для остальных входных переменных и подключение выбранных функций на требуемые к выходу устройства. Устройство может работать как с аналоговыми входными сигналами, так и с цифровыми входными сигналами. Выходы устройства также могут быть как аналоговыми, так и цифровыми. 1ехиико-экономический эффект от введения

блока памяти функций, регистров вида функции, регистров адреса нелинейности, второй и третьей групп схем сравнения заключается в снижении затрат времени на набор структурной схемы устройства, что приводит к повышению производительности и коэффициента использования оборудования устройства.

Формула изобретения

Устройство для совместной работы цифровых и аналоговых машин, содержащее регистр адреса, вход которого соединен с первым входом устройства, а выход-с входами

блока памяти функций и цифро-аналогового преобразователя, выход которого соединен с первым входом первого схемы сравнения, второй вход которой соединен с вторым входом устройства, а выход-с входом щифратора,

выходы блока памяти функций соединены с первым входом коммутатора, второй вход которого соединен с выходом регистра адреса, выход коммутатора соединены со входом блока реверсивных счетчиков, выход которого

через блок вывода соединен с выходом устройства, отличающееся тем, что, с целью повыщения производительности, в него введены блок памяти адресов, регистр вида функций, регистр адреса нелинейностей, вторая и

третья схемы сравнения, причем выходы блока памяти адресов соединены с входами регистров вида функций и адреса нелинейностей, выходы которых соединены с первыми входами соответственно второй и третьей

групп схем сравнения, вторые входы которых

соединены с выходом шифратора, выходы

второй и третьей схем сравнения соединены

с третьим и четвертым входами коммутатора.

Источники информации, принятые во внимание при экспертизе:

1.Авт. св. 333566, кл. G 06G 7/26, G 06J 1/00, 1971.

2.Авт. св. 504211, кл. G 06J 3/00, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для совместной работы цифровых и аналоговых вычислительных машин | 1975 |

|

SU578646A1 |

| Устройство возведения в дробную степень | 1973 |

|

SU596941A1 |

| Устройство для программного управления | 1981 |

|

SU987579A1 |

| Устройство для возведения в дробную степень | 1974 |

|

SU571812A1 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| Устройство для коррекции характеристик измерительных преобразователей | 1982 |

|

SU1100630A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU942034A1 |

| Цифро-аналоговое вычислительное устройство | 1973 |

|

SU503258A1 |

| Устройство для вычисления функции линеаризации | 1980 |

|

SU905831A1 |

Авторы

Даты

1977-02-28—Публикация

1973-04-09—Подача