(54) УСТРОЙСТВО, ВОЗВЕДЕНИЯ В ДРОБНУЮ СТЕПЕНЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в дробную степень | 1974 |

|

SU571812A1 |

| Устройство реализации нелинейных зависимостей для гибридных вычислительных систем | 1973 |

|

SU485474A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1552381A1 |

| Третьоктавный спектральный анализатор | 1985 |

|

SU1308927A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Цифро-аналоговое вычислительное устройство | 1973 |

|

SU441658A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для совместной работы цифровых и аналоговых машин | 1973 |

|

SU548871A1 |

| Устройство для извлечения квадратного корня | 1980 |

|

SU1099318A1 |

Изобретение относится к вычислительной технике и предназначено для возведения в дробную степень в управляюн1их системах и специализированных вычислительных машинах. Известно устройство возведения в дробную степень, которое содержит цифро-аналоговые преобразователи, компаратор, схему цифрового уравновешивания, регистр показателя степени триггер операции и управляемые ключи 1 Недостатками этого устройства являются: -- ограниченные функциональные возможности, поскольку в нем реализуются функции, показатель степени которых может принимать только значения целых чисел {2, 3, ... ) или значения величин, обратных целым числам (4-, |-... ), и нельзя вычислять функции, показатель степени которых принимает значения величин, представляющих собой отпопление двух целых чисел, (l,-,-, ... ); - - низкая точность, так как в устройстве исПольдуются аналоговые блоки (коммутатор, ключи). Известно также устройство реализации нелиней)ых зависимостей, применяемое в аналоговых и гибридных вычислительных машинах, которое может быть использовано для возведения в дробную степень. Для устранения указанного недостатка содержит запоминающее устройство, регистр адреса, цифро- и аналоговый преобразователь, преобразователи последовательного кода в параллельный, вентильные схемы, триггерные регистры, блоки ключей и разрядных сопротивлений и схемы совнадения 2. Недостатком этого устройства является большой объем аппаратурных затрат, в частности большой объем памяти для хранения функций, и низкая скорость реализации нелинейных зависимостей. Прототипом изобретения является устройство возведения в дробную степень, содержапгее блок возведения в целую степень, блок извлечения корня и регистр адреса, вход которого подключен ко входу тактовых импульсов устройства, первая группа выходов соединена со входами блока памяти прираш,ений, а вторая Ipyn па выходов соединена со входами цифро-ана/югового преобразователя, выход которого соединен с первыми входами двух схем сравнения, вторые входы которых подключены к информнционным входам устройства, выходы блока памяти прираШений соединены со входами соответствуюшнх усилителей считывания, выхпцы

:.;,i:-o. :,л: u; :;:i;;--и соедикень; с лерваии йходарли

.:X;;yjiitTi:T yiOiUHX ЭЛКМч liiOB И, ВТОрЫе ВХОДЫ

KOfupbix гюдключены к выходам соотвгтст1аую.;: :;:«,.; cpaeneijH, и аыходы через cooTfierCTiV;5 -w; & цеГдг-иа последовательно соединенных онред-ле) направления ярирзш.ений, ;1адключекныА двумя другими екодамя к выходам двух младших разрядов регистра адреса. реверсивных счетчиков и блоков ключей н разРЙДВЫХ сопротивлений соединен с соогветствующими зыходами устройства 3.Недостатком зтого устройства являются еграннченр.ые функнионвльньзе возможностя, так как устройство позволяет реализовать только функции,приращения которых зап зсакы в блок памяти приращений, т. е. количестйо раалкзиуемых функций ограничено разрадностьзд блока памяти приращений.

Цель изобр-отенкЯ в расширения фукко.иоHaJibHbix возможностей устройства.

Эго т&л, что устройство содержат схему сравнения кодов, блок клюце& к разрядных стфотиэлений и третыо схему сравнемия, иераый вход которой подключен К еоот(;1етстаую цему информационному входу устройства, второй вход подключен к выходу Цлфрс зиалогового преобразователя, а выход сосхкнен с пероым управляющим входом блока аозвсдения в целую степень, второй н третий управляющие входы которого подключена к выкодам двух младших разрядов регистра адрееа, информационные входы подключены к выходам соответствующих усилителей считывания, а выходы соединены е первой группой &;;одов схемы сравнения кодоа, вторая гругиш входов iiOTopoH подключена к второй группе выходов регистра адреса, а выход соединен с нерпым управляющим.входом блона извлечения ксрнй, второй ii трегий уиравляющяе входы которого подкл очены к выходам младших рЕЗрпдоа регистра адреса, ин||)ормациоиные входы 1«одк.пиче-МЬ к выходам соответствующих усилителей считывани, а выходы через третий блок слючек и разрядиsjx соаротиолеинй соединены с cooTufiTCTiyiouubSi выходом устройства. Кроме гого, блок возведения а целую степень и блок s-i3BJie4eHiifl корня каждый содер кит регистр, деии 1рра1ч р. зле иснты И и ИЛИ, схему .;пределеиия нанравлеиия приращения и реперснйНЫЙ сгетч гк, ьыходы которого соедииейы с выходами блока, информацнониые входы кото-iioro через соотаетстаующие элементы И, подключенные входами к соответствую яим Быхо;1,.аг4 деиии)|)итора, соединены со входами элемента ИЛИ, выход KOiOporo через Tioc л вдов ате л uiio соед н i leu 11 ые COOT в етству ющие .vieHT И, подключб-иный друг-им ьходом к первому упраш1яю111,1ыу аходу o.iojia, i-i схему определения иапраиления приращения, лодклюqeuisyio двумя другиг.ш входами ко второму и тре-1ъему уиравляклдим входам блока, соединен с;о аходом реверснв1 О1о счетчика, а ьыходы регистра соединены со входами дешифратора.

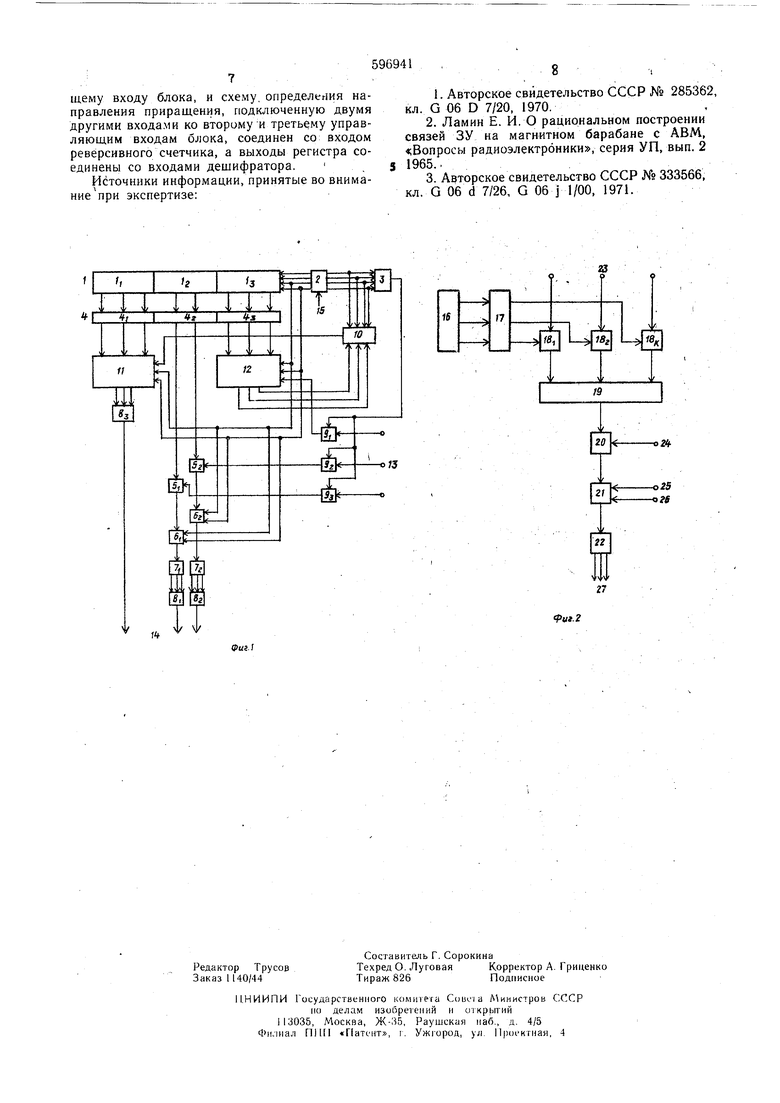

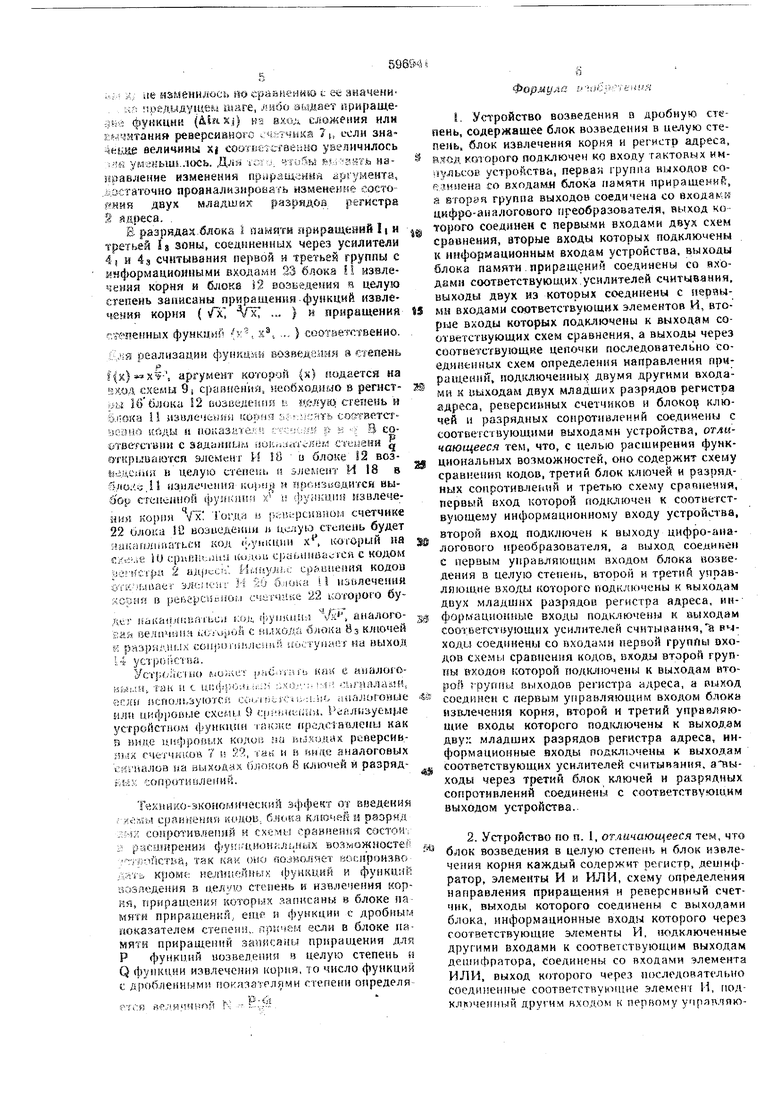

Па sl)sii 1 1редставле1 а блок-схема уст рой,cTu;i возведе 1и 1 в дробную стеиень; на ()иг. 2 - блок-с.хс.,1а нонве/ииин и целую степень .ii4t-i:il;i Kiipliil.

У.:трийстао (фиг. I) содержит блок I памяти нркращёний, разделенный по разрядам на тря зоны 1,, и. I а, в первой КЗ ноторых l| записйны пряращения функций извлечения корня, во второй li-приращения нелинейных функций ii в третьей lj- приращения степенных функций, регистр 2 f дреса, цифро-аналоговый преобразователь 3, усилители 4 считывания, разделенные по разрядам на группы 4|, 42, 4$ а соответствии с зонами блока памяти приращений 1, элементы И 5i я Sa схемы 6) и 6; определения направления приращения, реверсивные счетчики и 7з, блоки 8|, 8 и 8а, ключей н разрядных сопротивлений схемы 9i, 85 и 9з сравнения, схему 10 сравнения кодов, блок 11 извлечения корня и блок 12 возведения в целую степень, информационные входы 13 устройства, выходы 14 устройства к вкод 15 тактовых импульсов устройства.

Блоки 12 возведения в ценную степень и П извлечения корня (фиг 2) содержат регистр 16, дешифратор 17, элементы И 8i, 18 ... 18к ; емент ИЛИ Ш, элемент И 20, схему 21 определения направления приращения, реверсивный счетчик 2Й, информационные входы 23 блока, первый, второй и третий управляющие входы 24, 25 и 26 блока и выходы 27 блока.

Работает устройство следующим образом;

Устройство позволяет реализовать нелинейные зависимости, приращения которых для рав.ных интервалов независимой переменной записаны в разрядах второй зоны г блока 1 памяти приращенну1. Начальные значения функций f(xo) для заданных значений аргументов Хо наносятся и реверсивные счетчики 7|, Та и 22, а текущие значения функций {х) получаются в тех Же счетчиках путем добавления приращений функций к содержимому реверсивных счетчиков 7ь 7а и 22 в режиме слежения за H3MeHeiuies«s значений, аргументов х.

Значений аргу.-.аентов Х1задаклся на информационные входы 13 устройства и поступают на входы схем сравнения 9|, 62 и 9з- Пусть, нагфимер, Б одном нз разрааов блока памяти приращений второй зоиы i 2 занисаны приращения функций п(х), а выход этого разряда через усилитель 4а считывания второй группы сседнпен с выходом элемента И Bj. Тогда адя реализации функций In(xi) необходимо подать значение аргумента х,- на вход схемы 9а сравнения. На вход 15 тактовых импульсов устройства постугшет тактовйн частота и регистр 2 адреса работает в ре,;киме счета тактовых импульсов, В соогвэтствии с изменением кода в регистре 2 адреса лроиаводигсл выбор соответствующей ягейки блока 1 на,мяти приращений и изменение нанряжения на выходе цифро-аналогового преобразователя 3, которое сравнивается на схеме 9з сравнения с аналоговой величиной.jii . В момент сравиеиия открывается И 5| и содержимое соответствуюи1.его разряда, в котором записаны приращения функции lnx,i-той ячейки блока 1 памяти ирираихений второй зоиы i;; постуиает иа вход схемы определения нанравленни ириращения 6|, кТ)торая не иронускает приращения функини tu вход ренерсивиого ечшчака 7,, если .значение нелич 5 ;; ;-;,: tie изменялось я-о cpaiatseHHso t; № эначени:/.;: ярйдидущеьа шнге, .«ибо вйдает нриращеuiiid:-: функции (&iax,i) на вхол сложения или Е читанн реаерсианоге счг-тчика 7 , если зна4e.aie величины Xj соотвс-г&гаегию увеличилось Ш умаКЬШ4..1()СЬ. Длг ЮГи, «TiiShS 5J-3STb направлеиие изменения приращений аргумента, .а,зсгаточно проанализировагь изменение состойНйя двук младшйх разрядов регистра 2 йдреса. , Е- разрядах.Йлока I памятн ариращаднй третьей Ь зоны, соединенных через усилители 4j и 4s считывания первой и третьей группы с информационными входами 23 блока 11 извлечения корня и блока 2 возведения в целую степень записаны прнращення функций извлечения корня ( Гх, Vltl ... ) и приращения функций (к ,. х ,., ) соотаетственно. Gjiu реализации функц и возведеняг степень 1|х), аргумент которой (к) подается на йход схемы 9i сравнения, необходимо в регнстijbj 16 блока 12 аоз15едеиия в иелую сгеяень и э.пока И лзвлечйыня сооня ;. :;:;; Чь сосгтветсгзегпю KfiAU (I показа е-:is .;;-г-:м.:,;уй г:- w ..v в срШвегствин с эадаиним ijcsj. OCKpuuaiOTcn ti 8 и блоке 12 возfedjACiiHii н целую степега. ss элемент И 18 в .-у,11 цэнлечеиия KUjjEiji « Г8(.)оиз1«сдитсй выбор стеселиой (Ьузнгнп: к i фугнш.1И извлечения ко) Vx Ioi-.na u ;;;iurptHBHOM счетчике 22 блока й возиедеиая и Uii iyso степень будет Hiu{anjiii iaTiL.cn код фущ-ащн х когорый на cxri.ie iO ,.auu L(tt,ii,iu cpuijUiiBiidCsi с кодом iiO si i|Jii 2 ajijjccis l-i n yjji;i; со&ииеаия кодов uLKibiisaer itjiciiciu- Ji 20 блока I наилечекий ясоня и peiiupciiciiOij счетийе 22 которого 6уAtr ijaiiaiLriinifi-ibca KOJ;, )1)упкиН;Э Vji аналогеsaii Bejiti4 ii: a ia;-; ii uli с блона 8з ключей pa:)pi-ii..U(.x coiijsoi-iuuit HiiA иистугиигг на выход И yCSp(ji Cl;- a. Ус1poiicUio (iuiitc; |j,fiC.vi;iib iuu( с аиялогоBSiii.iH. таи i t ц|;фрО; 1;:1;; :ix,0::.:. .lii -biiiaJiasH, enjt( «споль уютси ciii.ifjtiCii;.:;: iiiiajsotOBUe Ei.iu цифровые cxeHLi 9 cui-iiHiuiaa. l ; Uiii;i.yeMjje устройстпом функции ((ро:дс1аелеии как п mint )jjo«b X Кодов jiij вгаходак pciBepcHB,11-л I . jMbuijp, 7 и ЙЙ, -сай и в tsK(«; аналоговых 1 . иалой )-л йиходах (jjintujft 8 KJiionefi и разрядI-. f)nooTtii jieifnfi, Тй/;нико-зко омяческий эффект от аяедения f :«:;,:, сраннен - Г кодов, Cjitiso ключей SJ разряд :::м} сопротивлений и схемы сравр1еиий состонг и расапфении фу п;цион;;лг.ных воаможяостей Г пг1Йсткй,, так как оно .няет воснроизводй ч кроме-: иея ик;йных функций и функций аозпедеиня в ii.e/s/.o степень и извле1 ер ня корня, гфнращенки которь-я записаны 8 блоке памнтн приращений; еще н функции с дробным ноказателем степени., причем если в блоке памяти приращений записаны прираихения для Р функинй иозведения а целую степень н Q фупкпин извлечсння корпя, то число функций с дробленным нокаязтрлями гтенеки огфеделя -.: P-tS 59 Формула i- if jiCic it.tfi 1.Устройство возведения а дробную степень, содержащее блок возведения в целую степень, блок извлечения корня н регистр адреса, йяод которого подключен ко входу тактоных имiiyjmcoB устройства, первая группа выходов соеаииена со входами блока памяти прнращениб, а вторая группа выходов соедичена со входа и цифро-аналогового преобразователя, выход ко toporo соединен с первыми входами двух схем срайнения, вторые входы которых подключены к информационным входам устройства, ыходы блока памяти. приращений соединены со входами соответствующих усилителей считывания, выходы двух из которых соединены с пер«ыми входами со«ответствуюш,их элементов И, вторые входы которых подключены к выходам соответствующих схем сравнения, а выходы через соответствующие цепочки последовательно соединенных схем определения направления приращений, подключенных двумя другими входами к «ыходам двух младших разрядов регистра адреса, реверсивных счетчиков и блоко ключей н разрядных сопротивлений соединены с соотсегствующими выходами устройства, отличающееся тем, что, с целью расширения функциональных возможностей, оно содержит схему сравнения кодов, третий блок ключей, и разрядных сопротивлений и третью схему сравнения, первый вход которой подюночен к соотиетствующему информацнонному входу устройства, второй вход подключен к выходу цифро-хчналогового преобразователя, а выход соединен с первым умравляюииш входом блока йозведения в це.чую степень, второй и третий управляющие ВХОДИ которого подключены к выходам двух младших разрядов регистра адреса, ин-формациоиные входы подключены к аыходам соот.сетстиующнх усилителей считывания,а вмходи соединены со входами первой группы DXOдов схемы сравнения кодов, входы второй групгш входон которой подключены к выходам втоpoft г-руггпь выходов регнстра адреса, а выход соединен с первым унравляюпхим входом блока извлечения корня, второй и третий управляю|дие входы которого подключены к выходам дву;: младших разрядов регистра адреса, информационные входы подключены к выходам соответствующих усилнтелей считывания, авыходы через третий блок ключей и разрядных сопротивлений соединены с соответствующим выходом устройства. 2.Устройство по п. 1, отличающееся тем, что блок возведения в целую степень н блок извлечения корня каждый содержит регистр, дешифратор, элементы И и ИЛИ, схему определения направления приращения и реверсивный счетчик, выходы которого соединены с выходами блока, информационные входы которого через соответствующие элементы И, подключенные другими входами к соответствующим выходам дешифратора, соединены со входами элемента ИЛИ, выход которого через последовятельио соеди1 енные соответствующие элемен И, подключенный другим входом к первому управляютему входу блока, и схему, определения направления приращения, подключенную двумя другими входами ко второмуи третьему управляющим входам блока, соединен со входом реверсивного счетчика, а выходы регистра соединены со входами дешифратора.

Источники информации, принятые во внимание при экспертизе:

5 1965..

ZJ

ia

го Ч:

2S

I 21 off

гг

27

fat. г

Авторы

Даты

1978-03-05—Публикация

1973-08-30—Подача