(54) УСТРОЙСТВО ДЛЯ. ВОЗВЕДЕНИЯ В ДРОБНУЮ СТЕПЕНЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство возведения в дробную степень | 1973 |

|

SU596941A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU922735A1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| Вычислительное устройство | 1983 |

|

SU1080135A1 |

| Устройство для формирования дуг и окружностей на экране телевизионного индикатора | 1990 |

|

SU1800476A1 |

| Устройство для возведения в п-ую степень | 1982 |

|

SU1132287A1 |

| Устройство управления последовательностью операций | 1981 |

|

SU1037251A1 |

| Устройство для извлечения корня @ -й степени | 1982 |

|

SU1084789A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1552381A1 |

I

Изобретение относится к области вычислительной техники и предназначено для реализаций функции возведения в дробную степень в управляющих системах и специализированных вычислительных машинах.

Одно из известных .устройств возведения в дробную степень содержит цифро-аналоговые преобразователи (ЦАП), коммутатор, схему цифрового уравновешивания, регистр Показателя степени, триггер операции и

управляемые ключи (l. Недостатками это-« го устройства являютсяограниченные функциональные возможности, поскольку в нем реализуются функции, показатели степени кСТОрых могут принимать только значения аелых чисел (2, 3...) я значения величин, обратных целым числам ( л ) нельз вычислять функции, показатель степени которых принимает значения величин, пре ставл еЕЮ1цих собой отношение Jдвyx целых чисел ( ) низкая точность, так как в устройстве используются аналоговые блоки (компаратор, ювочи).

Другое известное устройство реализации Нелинейных зависимостей для аналоговых

и гибридных вычислвтельных машин, которое может быть использовано также и для возведения в дробную степень, содержит з« поминающее устройство, регистр адреса, цифро-аналоговый преобразователь, преобразователи последовательного кода в параллельный, вентильные схемы, трнггврные регистры, блоки ключей и разрядных сопротивлений и схемы совпадения (2). Недостатклми этого устройства являются большие аппаратурные затратм, в частности большой объем памяти для хранения функций, в низка скорость реализации нелинейных аавкстлоотей.

Наиболее близким техннческям решением к изобретению является устройство для воэ ведения в дробную степень, содержащее, как и предложенное устройство, регистр адресе, вход которого подключен ко входу тактовы; импульсов устройства, -первая группа вь ходов которого соединена со входами блоке памяти приращений, a вторая группа выходов - со входамв первой группы ваюдоа вой схемы cptaBiieHHS кодов и вхсздамн ДАП, выход кото{к го соединен с йврвымв

входами двух схем сравнения, вторые входы которых Подключены к информационным входам устройства. Выходы блока памяти прирашений соединены со входами соответствующих усилителей считывания, выход одного из которых через последовательно соедине ны« первый элемент И, второй вход которогц подключен к выходу одной из схем сравнения. Два других входа схемы определения направления приращений подключены к вь ходам двух младших разрядов регистра адре са. Реверсивный счетчик и первый блок и разрядных сопротивлений соединены с одним из выходов устройства, другой выход которого подключен к выходу второго блока jj ключей и разрядных сопротивлений. Выходы соответствующих усилителей считывания сое динены с информационными входами блоков возведения в целую степень и извлечений корня, первые в вторые управляющие входы которых подключены к выходам двух младши разрядов регистра адреса. Третий управляк щий вход{блоков возведения в целую степен подключен к выходу другтзй схемы сравьэния а его первые информационные выходы сое динены со вторыми входами первой схемы сравнения кодов З. недостатком этого устройства является узкая область его применения, так как в этом устройстве реализуются только функции, приращения которых записаны в блоке памяти приращений, разрядность которого определяет число воспроизводимых функгввй. Целью изобретения является расщирение области применения устройства. Эта цель достигается тем, что предложенное устройство содержит элементы И и ИЛИ и вторую и третью схемы сравнения кодов, первые входы которых подключены к выходам регистра адреса. Вторые входы второй схемы сравнения кодов подключены ко вторым информационным выходам блока возведения в целую степень, а вторые входы третьей схемы сравнения кодов - к первым информационным выходам блока извл&нения корня, первые и вторые информационные выходы которого соответственно через второй и третий элементы И, вторые входы которых подключены соответственно к первом и второму управл5пощим выходам блока и влечения кбрня, соединены, со входами первого элемента ИЛИ, выходы которого соеди нены со входами второго блока ключей и разрядных сопротивлений. Выход первой схе мы сравнения кодов через последовательно соединенные четвертый элемент И, подключенный вторым входом к первому управляющему выходу блока возведения в целую ст& пень, и второй элемент ИЛИ подключенный вторым входом к выходу второй схемы

сравнения кодов через пятый элемент Hj второй вход которого подключен ко второму управляющему выходу блока возведения в целую степень, соединен с третьим управляющим входом блока извлечения корняр чет вертый управляющий вход которого подключен к выходу третьей схемы сравнения кодов через щестой элемент И, подключенный

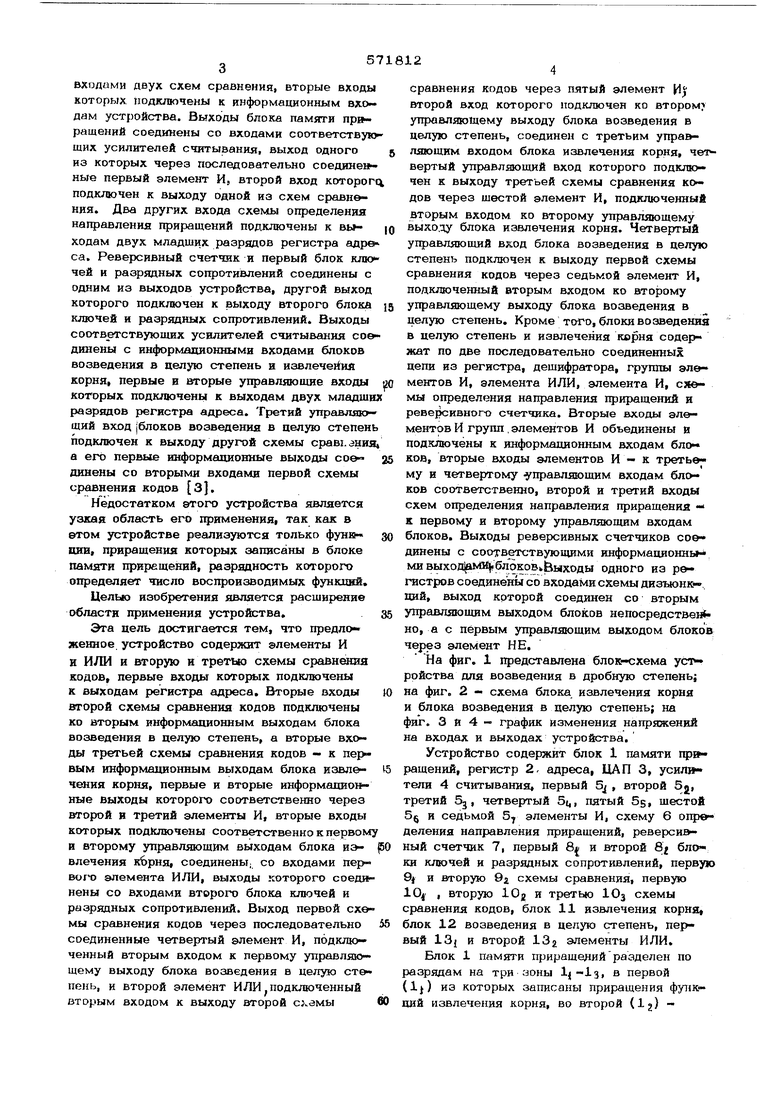

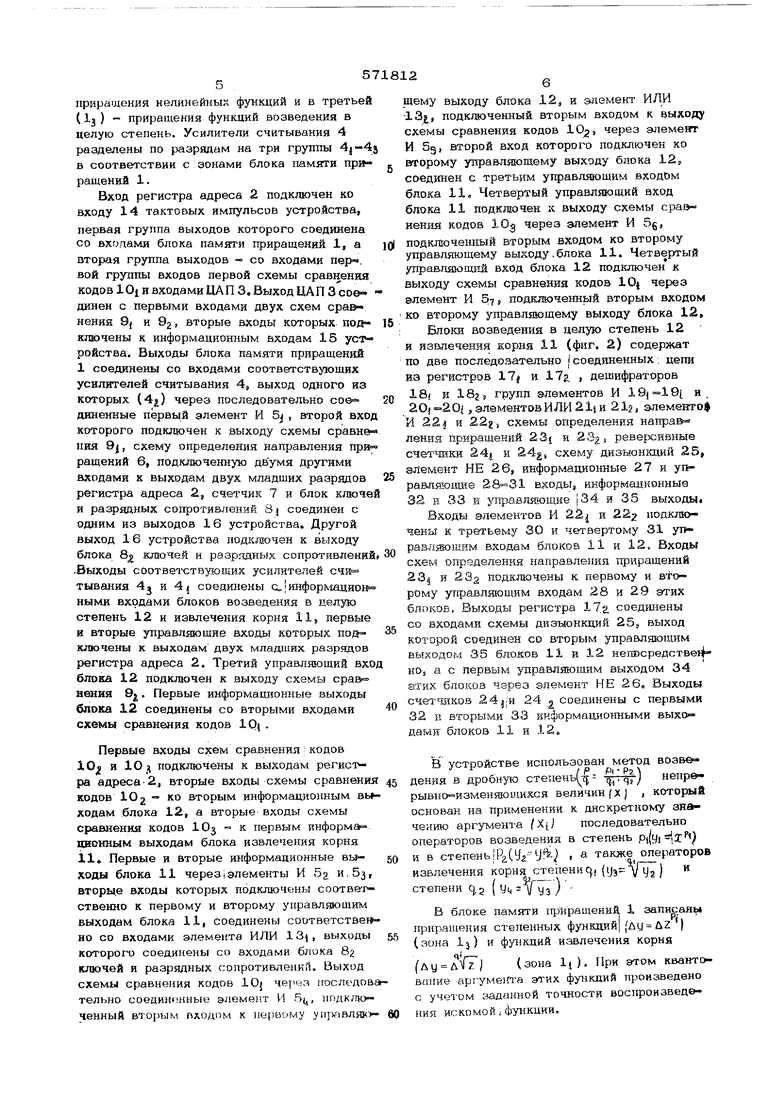

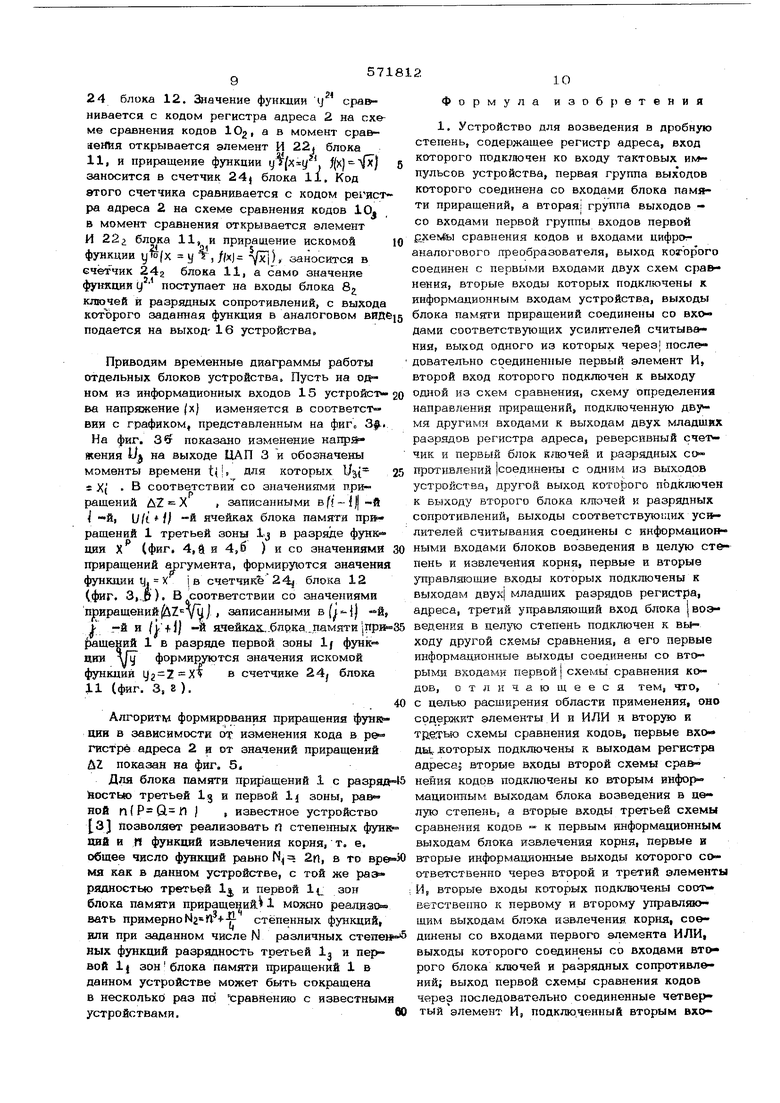

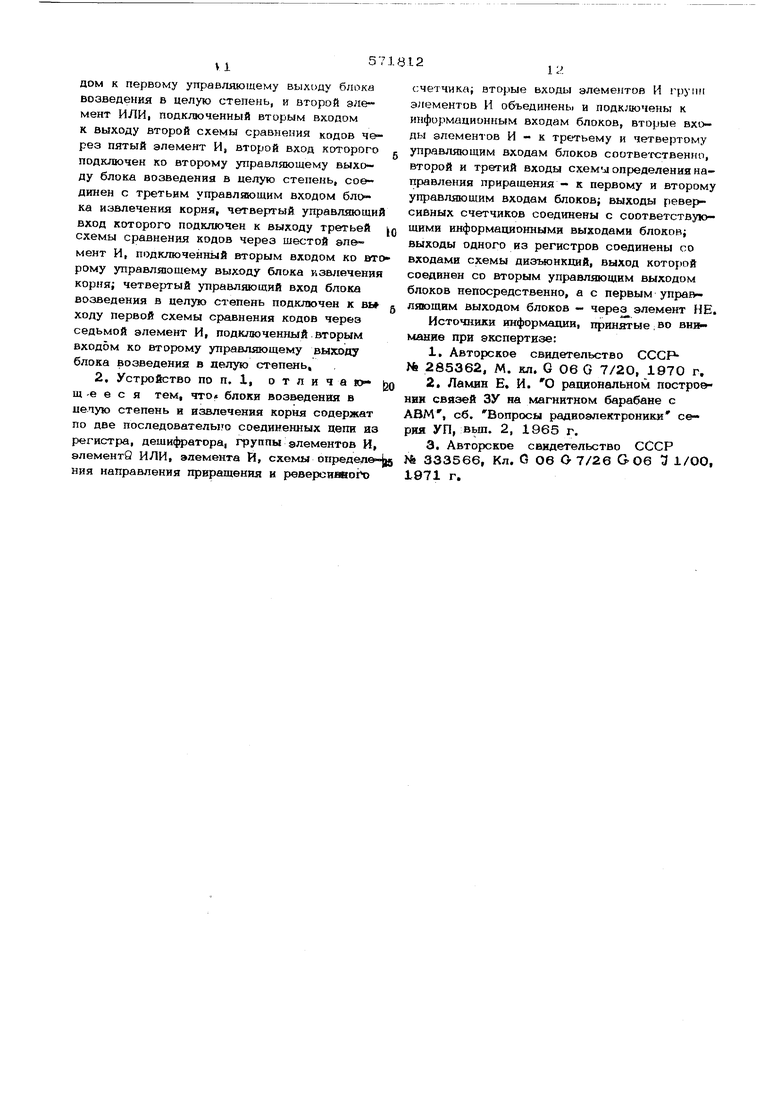

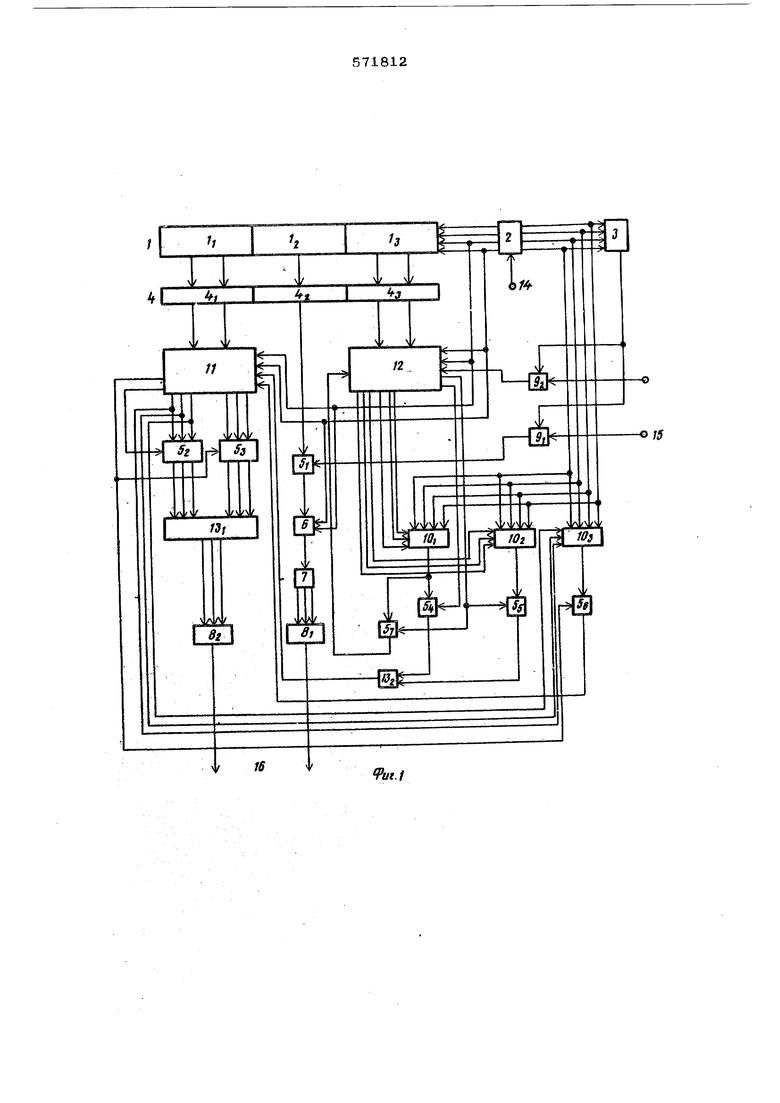

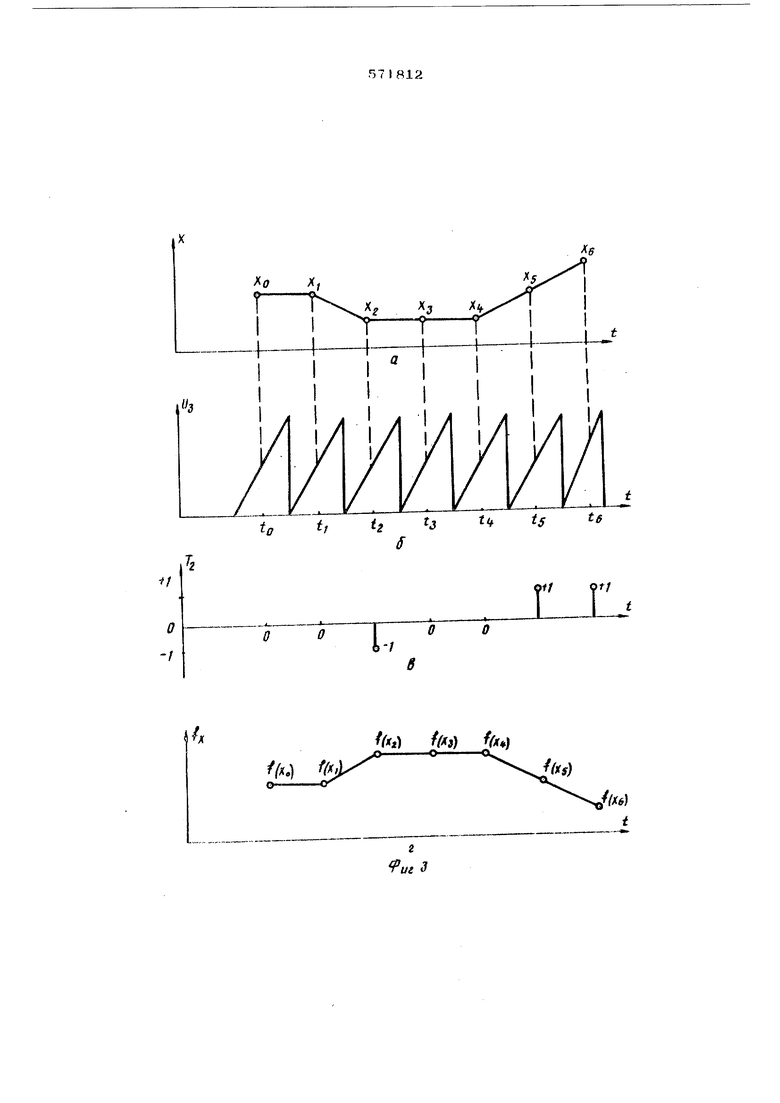

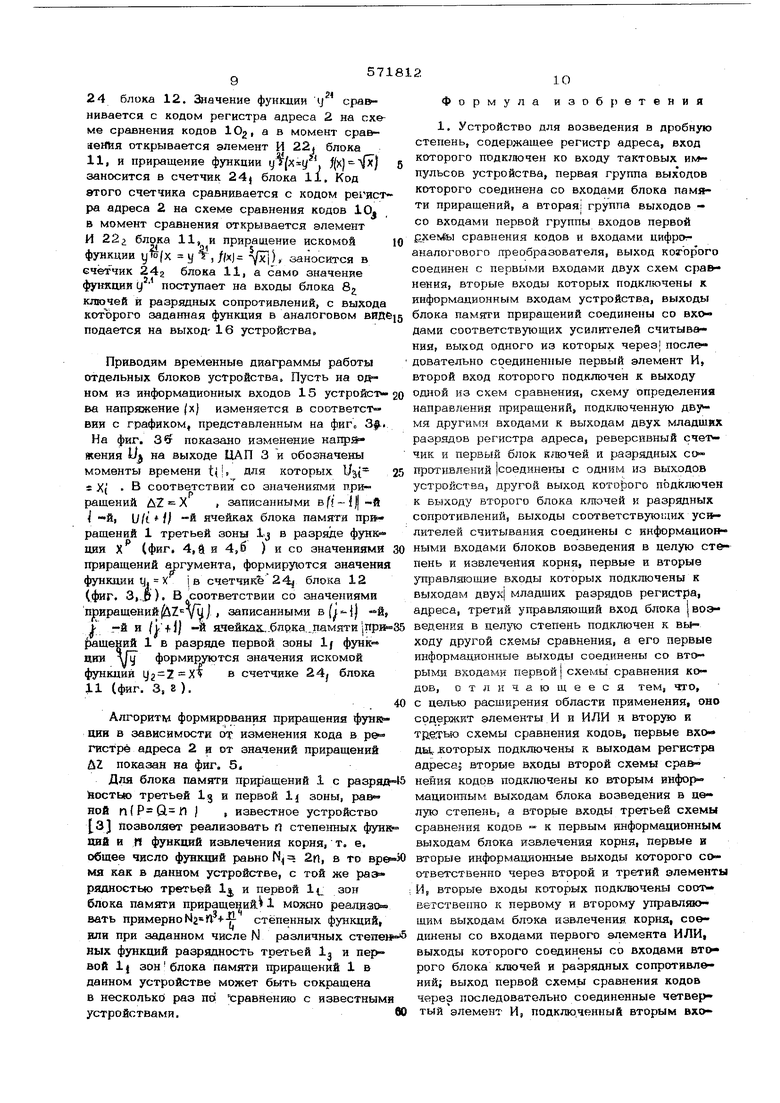

вторым входом ко второму управляющему выхо.ду блока извлечения корня. Четвертый управляющий вход блока возведения в целую степень подключен к выходу первой схемы сравнения кодов через седьмой элемент И, подключенный вторым входом ко второму управляющему выходу блока возведения в целую степень. Кроме того, блоки возведения в целую степень и извлечения содержат по две последовательно соединенных цепи из регистра, дешифратора, группы элементов И, элемента ИЛИ, элемента И, cjt&мы определения направления приращений и реверсивног-о счетчика. Вторые входы элементов И групп, элементов И объединены и подключены к информационным входам блоков, вторые входы элементов И - к третьему и четвертому управляющим входам блоков соответственно, второй и третий входы схем определения направления приращения - к первому и второму управляющим входам блоков. Выходы реверсивных счетчиков соединены с соответствующими информационнь ми выход(ама блокоЕ.1,Ьыходы одного из р&гистров соединены со входами схемы дизъюнк ций, выход которой соединен со вторым управляющим выходом блоков непосредстве но, а с первым управляющим выходом блоков через элемент НЕ. На фиг. 1 представлена бло &-схема уст ройства для возведения в дробную степень; на фиг. 2 - схема блока извлечения корня и блока возведения в целую степень; на фиг. 3 и 4 - график изменения напряжений на входах и выходах устройства. Устройство содержит блок 1 памяти приращений, регистр 2. адреса, ЦАП 3, усилители 4 считывания, первый 5j , второй Sj, третий 5д, четвертый 5t,, пятый Sg, шестой 5§ и седьмой 5-J элементы И, схему 6 определения направления приращений, реверсивный счетчик 7, первый 8 и второй 8 блоки ключей и разрядных сопротивлений, первую 9{ и вторую 92 схемы сравнения, первую 10 , вторую lOj и третью Юз схемы сравнения кодов, блок 11 извлечения корнЯ| блок 12 возведения в целую степень, первый ISj и второй 132 элементы ИЛИ. Блок 1 памяти приращений разделен по разрядам на три зоны Ij-Iji в первой (Ij) из которых записаны приращения фу7«кций извлечения корня, во второй (Ig) - приращения нелиней1Ь Х функций и в третьей (Ij ) - приращения функций возведения в целую степень. Усилители считывания 4 разделены по разрядам на три группы 4|-4 в соответствии с зонами блока памяти приращений 1. Вход регистра адреса 2 подключен ко входу 14 тактовых импульсов устройства, первая группа выходов которого соединена со входами блока памяти приращений 1, а вторая группа выходов - со входами пер-, вой группы входов первой схемы сравнения кодовЮ ивходамиЦАПЗ.ВыходЦАПЗсое динен с первыми входами двух схем сравнения 9 и Qj, вторые входы которых подключены к информационным входам 15 устройства. Выходы блока памяти приращений 1 соединены со входами соответствующих усилителей считывания 4, выход одного из которых (4|) через последовательно со& диненные первый элемент И 5j , второй вхо которого подключен к выходу схемы сравне ния 9|, схему определения направления пр№ ращений 6, подключенную двумя другими входами к выходам двух младших разрядов регистра адреса 2, счетчик 7 и блок ключе и разр5щных сопротивлений 8j соединен с одним из выходов 16 устройства. Другой выход 16 устройства подключен к выходу блока 8 ключей и разрядных сопротивлений .Выходы соотве1ч;твующих усилителей тывания 4 и 4j соединены с,|инфор1чтцио№ ными входами блоков возведения в целую степень 12 и извлечения корня 11э первые и вторые управляющие входы которых no ключены к выходам двух младших разр5здов регистра адреса 2. Третий управляющий вхо блока 12 подключен к выходу схемы срав нения 9|. Первые информационные выходы блока 12 соединены со вторыми входами схемы сравнения кодов 10( . Первые входы схем сравнения кодов iOe и 10ц подключены к выходам регист- ра адреса-2, вторые входы схемы сравнения кодов 102 вторым информационным вь ходам блока 12, а вторые входы схемы сравнения кодов 10 к первым информ ционным выходам блока извлечения корня 11. Первые и вторые информационные вь ходы блока 11 через элементы И ба и.5з, вторые входы которых подключены соответственно к первому и второму управляющим выходам блока 11, соединены соответстве но со входами элемента ИЛИ 13,, выходы которого соединены со входами блока Вг ключей и разрядных сопротивлений. Выход схемы сравнения кодов lOj чете: последов тельно соединенные элеме)т И б,, ппдклю™ ченный вторым пход| м к иервор у у111 1вля5. щему выходу блока 12 j и элемент ИЛИ -13|, подключенный вторым входом к выходу схемы сравнения кодов lOj, через элемент И 5д, второй вход которого подключен ко второму управшношему выходу блока 12; соединен с третьим управляющим входом блока 11, Четвертый управляющий вход блока 11 подключен х выходу схемы сравнения кодов 10 через элемент И 5g, подкгаоченный вторым входом ко второму управляющему выходу,блока 11. Четвертый управляющий вход блока 12 подключен к сравнения кодов 10 через подключенный вторым входом ко второму управляющему выходу блока 12, Блоки возведения в целую степень 12 и извлечения корня 11 (фиг, 2) содержат по две последовательно | соединенных. цепи из регистров 17| и 17, , дешифраторов 18( и 18г, групп элементов И и, J элементов И ЛИ 2 li и 2l2j злементоф И 22 j и 22iPs схемы определения напрзв ления приращений 23 и 232t реверсивные счетчики 24| и 2.4, схему дизъюнкций 25, элемент НЕ 26, информационные 27 и управляющие входы, кнформадионные 32 и 33 3 jTipasnsB0mHe |34 я 35 выходы, Входы элементов И 221 и 222 подключены к третьему ЗО и четвертому 31 ут равлщощим. входам блоков 11 и 12 „ Входы схем определения направления приращений 23 и 232 подключены к первому и второму управляощим входам 28 и 29 этих блоков. Выходы регистра 17.2. соединены со входами схемы дизъюнкций 265 выход которой соединен со вторым управляющим выходог. 35 блоков 11 и 12 непвсредстве но, а с первым управляющим выходом 34 эггкх блоков через элемент НЕ 26, Выходы счетчиков 24);и 24 соединены с первыми 32 и вторыми 33 информационными выхо даын блоков 11 и 12. ё устройстве использован метод , и Рг Дешш в дробщто степень( . qtj пепр рывно-изменяющихся величин (х) , который основан на применении к дискретному SHaiчению аргумента fX{J последовательно операторов возведения в степень Pijyj Мзг и в степень|p2.( , а также операторов извлечения корня стопенно, () н IOi, , VI V J3 ч 4Z I степени (з У ( V Уз ) В блоке памяти прирашеннй 1 записаны приращения степенных функций , (зона Ij) и функций Ичзвлечения корня i- (лу дчг (зона Ij), При этом кванте вание аргумеНта этих функций произведено с учетом заданной точности воспронзвед ния искомой Функции. Для к(аксиьлальной частотной cocraenflKw щей ( f ) функции ZfX/ и представления искомой функции П - разрядным кодом с погрешностью, не превышающей единицы младшего разряда, шаг квантования Ь аргумента /х) определяется из соотношения 2nf-2n , , Для заданных значений f и п можно определить точностные параметры искомой функции из формулы Число N ячеек блока пймяти прирашений 1 для представления функции с заданной точностью определяется из соотноШШ1ИЯI.;tf2. Поскольку соседние значения I -и фувкцго отличаются одно от другого на единицу млапшего разряда, то в m -разрядной jrteft ке блока памяти приращений 1 можно зап сатЬ m различных функций для бинарного представления приращений функций. Для тактовой частоты входных импульсо I разрядности представления аргумента Я fe числа N ячеек блока памяти прир щенки 1, устройство позволяет обрабать вать. входные сигналы Л 3t } с частотой NX) 4 ZoiN-I Так для /ц - 1 мп Я 8, Н « 1000 устройство позволяет следить за измев ние аргумента с частотой .1 Гц, При этом воспроизводятся (tl различных функций одновре менно. Устройство работает следующим обравом Для рвализапвн функций | возведения в целую степень F( f н бходвмо в регистры 17j и 17д блока 12 записать кбды сомволштелей Р| и IJ числителя показатв ля степени Р F} - Pj , а в регистры 17| и 17 блока 11 необходимо записать коды со шожителей и ( знаменателя по казателя степени , Числитель Р н знаменатель «j. показателя степени § 1фед показателя степени варительно разлагают на такие сомножятели (If Fj ) и (J, ), приращения ветствуюших им степенных функций (х , к ) и функций извлечения корня (/)Г , ЗГ) д;ш KOTOpkx содержатся в третьей 1, и первой 1/ бонах блока памяти приращений 1. Например, если в третьей 1| и первой 1| зонах блока памяти приращения 1 заш саны приращения функций,, для которых Р( 4,5, 7 и 9t.,«5, 7, то ;ДЛЯ рвализации функций /fX) необходимо Bjpeгистры 17) и 172 блока 12 записать коды PJ « 4 и FI 4, а в регистры и 17- блока 11 - коды ( 3 и « 7. Го да в счетчиках 24, и 24j, блока 12 и счетчиках 24 и 242 блом И накопятся коды х , X , хТ и х ооответствешш. Если числитель и знаменатель показателя задашюй степенной функции соответствуют непосредственно заш1са1шым в блоке памяти приращений 1 функциям, например Р 3, « 7, то в регистры 17 и 17 блока 11 и блока 12 записываются нулевые коды для ( 1 и F 1, Тогда на выходах схем диэьюнкции 25j и 25 управляющие сигналы отсутствуют, а управляющий сигнал на выходе элемента НЕ 26 блока 12 открывает элемент И 5( и с выхода схемы сравнения кодов lOf импульс поступает через второй элемент ИЛИ ISj на второй вход элемента И 221 блока 11, Управляющий I импульс с выхода элемента НЕ 26 блока 11 открывает элемент И 5, не первых информадиошйлх выходов 32 блока 11 информация поступает через элемент ИЛИ I3j на входы блока 83 ключей и разрядных сопротивлений, с выхо да которого результат подается на выход 16 устройства. Рассмотрим функционирование устройства на примере вычисления степенной функции f(J . Значение аргумента у с ин рмадионного ... . L входа 15 устройства подается на вход схемы сравнения 9 на другой вход которой с выхода ЦАП 3 поступает аналоговое знач&Higfe напряжения, изменяющегося по пилоо&разному закону. Числитель показателя степени (21) зйе данной функции у раскладывается на npofeтые множители (3 и 7), которые заносятся в регистры 17j и 17г; блока 12, а простые множители (2 и 5 энаменагеля (Ю) по казателн степени заданной функции заносятся в регистры 17j и iTj блока 11. В cooi ветствии со шачением показателя степени открываются соответствзтощие группы элементов И 10i н 2b(, f ( 2,5) в блоке 11 я группы элементов И 19i и 2 Of (| 3,7) в блоке 12, подключенные ч&Р усилители считывания 4 к разрядам блока памяти приращений 1, в которых записаны приращения функций извлечения корня (т и V5t) и функции введения в степень (х а х ). В момент сравнения напряжений на вь ходах ЦАП 3 и входной величины I/ схема сравнения 9 выдает сигнал, который открывает элемент И 22 блока 12, и приращение функции у (х Уг) ,|ffx) X заносится в сЧетчик 24 блока 12. При сравнении кодов на выходах счетчика 24j и регистра адреса 2 с схемы ера нения кодов lOj открывается элемент И 22 блока 12, и приращение функции yV y ffx) Х, заносится в счетчик 24 блока 12. Качение функции сравнивается с кодом регистра адреса 2 на схеме сравнения кодов lOg, а в момент оравяеНйя открывается элемент И 22 блока 11, и приращение функции () б заносится в счетчик 24j блока li. Код этого счетчика сравнивается с кодом регист ра адреса 2 на схеме сравнения кодов 10, в момент сравнения открывается элемент И 22г блока 11, и приращение искомой Ю функции у(х ), заносится в ечетчик 242 блока 11, а само значение функции поступает на входы блока 8, ключей и разрядных сопротивлений, с выхода котЪрого заданная функция в аналоговом BHHej5 подается на выход- 16 устройства Приводим временные диаграммы работы отдельных блоков устройства. Пусть на о№ном из информационных входов 15 устройст-20 ва напряжение |х) изменяется в соответстВИИ с графиком, представленным на фиг 3f... На фиг. 3 показано изменение напражения Uj на выходе ЦАП 3 и обозначены моменты времени t{ |. Для которых 25 S Х( -В соответствии со значениями приращений Д2 Х , записанными Bff-i| -и -и, L//i f/ й ячейках блока памяти првращений 1 третьей зоны Ij в разряде фунюции Х (фиг. 4, И 0 4,6 ) и со значениями 30 приращений аргумента, формируются значения функции у. X i в счетчикЬ 24 блока 12 (фиг. 3,.). В .соответствии со значениями приращений Z Vyj записанными в(-{) , V -и и (у-) -и MHetKa.&,-6acKa..naivf.qTn щений 1 в разряде первой зоны 1/ функции ЧГу формируются значения искомой функций в счетчике 24i блока 11 (фиг. 3, 8 ), Алгоритм формирования приращения в зависимости от изменения кода в ре« гистрё адреса 2 и от значений приращений UZ показан на фиг. 5i Для блока памяти приращений 1 с разряд-15 йостью третьей Ig и первой Ij зоны, {зав ной п( ) , известное устройство Позволяет реализовать п степенных ций и О функций извлечения корня, т. в. общее число функций равно N 5 2п, в то ) мя как в данном устройстве, с той же ра рядностью третьей 1 и первой зон : блока памяти приращений 1 можно реализо вать примерно Мгап- -- - степенных функций, или при заданном числе N различных степе№ й ных функций разрядность третьей 1, и Ij зон блока памяти приращений 1 в данном устройстве может быть сокращена в несколько раз noi сравнению с известными устройствамя. 60 40 -10 Формула изобретения - Устройство для возведения в дробную степень, содержащее регистр адреса, вход подключен ко входу тактовых иь пульсов устройства, первая группа выходов которого соединена со входами блока памя приращений, а вторая группа выходов входами первой группы входов первой сравнения кодов и входами цифро:аналогового преобразователя, выход когЬрЪго соединен с первыми входами двух схем сравнения, вторые входы которых подключены к информационным входам устройства, выходы блока памяти приращений соединены со входами соответствующих усилителей считывания, выход одного из которых через последовательно соединенные первый элемент И, второй вход которого подключен к выходу одной из схем сравнения, схему определения направления приращений, подключенную дву мя другими входами к выходам двух младших разр5щов регистра адреса, реверсивный и первый блок ключей и разрядных со прот1шлений соединены с одним из выходов устройства, другой выход подключен к выходу второго блока ключей и разрядных сопротивлений, выходы соответствующих ус лителей считывания соединены с информационными входами блоков возведения в целую степень и извлечения корня, первые и вторые управляющие входы которых подключены к выходам двук| младших paapsmoB регистра, адреса, трегий управляющий вход блока |воэведения в целую степень подключен к вы-, ходу другой схемы сравнения, а его первые информационные выходы соединены со вто- рымй входами первой схемы сравнения кодов, отличающееся тем, что, с целью расширения области применения, оно содержит элементы И и ИЛИ и вторую и третью схемы сравнения кодов, первые вхоД 4 «оторых подключены к выходам регистра адреса вторые входы второй схемы сравнения кодов подключены ко вторым инфор-. мационным выходам блока возведения в целую степень, а вторые входы третьей схемы сравнения кодов - к первым информационным выходам блока извлечения корня, первые в вторые информационные выходы которого соответственно через второй и третий элементы И, вторые входы которых подключены соот- ветствеино к первому и второму управляющим выходам блока извлечения корня, соединены со входами первого элемента ИЛИ, выходы которого соединены со входами вто рого блока ключей и разр5щных сопротивл ний; выход первой схемы сравнения кодов через последовательно соединенные четвертый элемент И, подключенный вторым входом к первому управляющему выходу блока возведения в целую степень, и второй элемент ИЛИ, подключенный вторым входом к выходу второй схемы сравнения кодов через пятый элемент И, второй вход которого подключен ко второму управляющему выходу блока возведения в целую степень, сов динен с третьим управляющим входом блока извлечения корня, четвертый управляющий вход которого подключен к выходу третьей схемы сравнения кодов через шестой эп& мент И, подключенный вторым входом ко второму управляющему выходу блока извлечения корня; четвертый управляющий вход блока возведения в целую степень подключен к вы ходу первой схемы сравнения кодов через седьмой элемент И, подключенный вторым входом ко второму управляющему выходу блока возведения в делую степень,

счетчика; вторые входы элементов И Ipyiin элементов И объединены и подключены к информационным входам блоков, вторые входы элементов И - к третьему и четвертому управляющим входам блоков соответственно, второй и третий входы схемы определения направления приращения - к первому и второму управляющим входам блоков; выходы реверсивных счетчиков соединены с соответствующими информационными выходами блоков; выходы одного из регистров соединены со входами схемы дизъюнкций, выход которой соединен со вторым управляющим выходом блоков непосредственно, а с первым ynpaivляющим выходом блоков - через элемент НЕ

Источники информадии, принятые , во внимание при экспертЕзе:

№ 333566, Кл. G Об О 7/26 G Об 3 1/ОО 1971 г.

32 2

О О о о

{х.} fftj,

Oit Off LJ

Ь-1 8

jft) ffX}} /(Or)

)

г игЗ .r-I

,,,,; ,4..:«ц.Л I V. ,a.

V f

УметШит.я i-

Bbi6ep(i-f)- и ячейки fffffffa

. ..-vtv.v.e : ---- Т

(|Л

c

tft

Н«

регистра

адреса

Увеличилса

dbi6op(i-fl) и Я ч ей ни SfiBHol /}/.4//,/

Авторы

Даты

1977-09-05—Публикация

1974-02-01—Подача