3

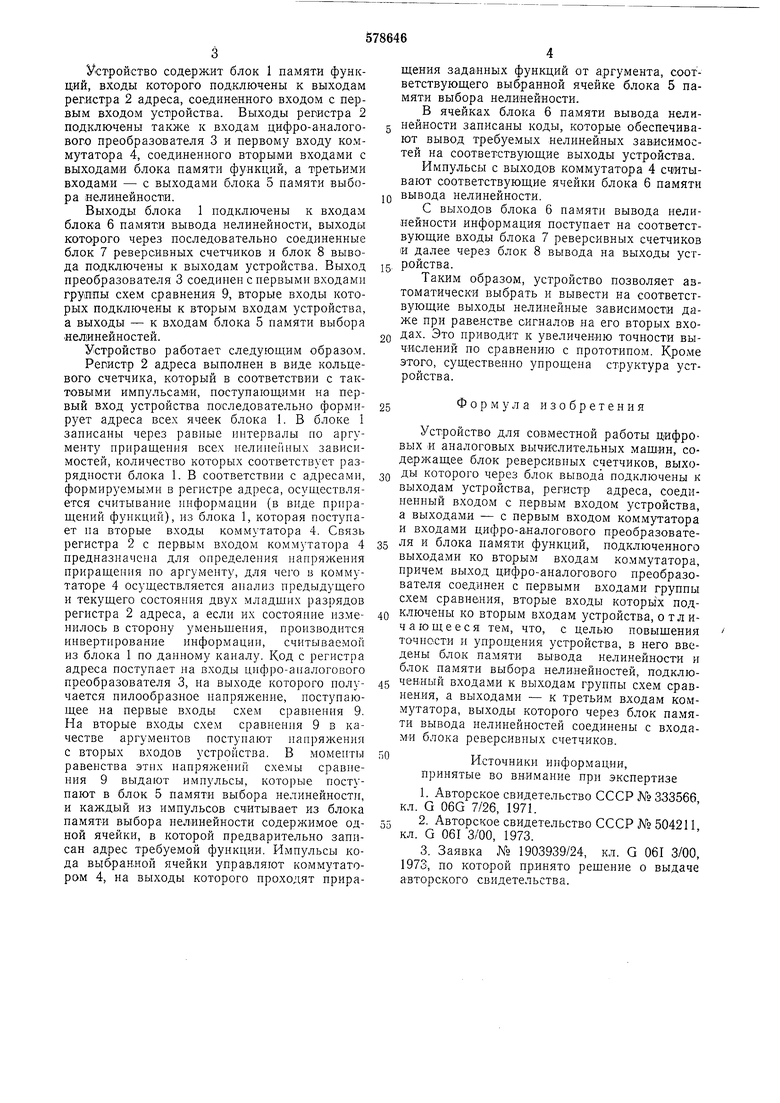

Устройство содержит блок 1 памяти функций, входы которого подключены к выходам регистра 2 адреса, соединенного входом с первым входом устройства. Выходы регистра 2 подключены также к входам цифро-аналогового преобразователя 3 и первому входу коммутатора 4, соединенного вторы.ми входами с выходами блока памяти функций, а третьими входами - с выходами блока 5 памяти выбора нелинейности.

Выходы блока 1 подключены к входам блока 6 памяти вывода нелинейности, выходы которого через последовательно соединенные блок 7 реверсивных счетчиков и блок 8 вывода подключены к выходам устройства. Выход преобразователя 3 соединен с первыми входами группы схем сравнения 9, вторые входы которых подключены к вторым входам устройства, а выходы - к входам блока 5 памяти выбора нелинейностей.

Устройство работает следующим образом.

Регистр 2 адреса выполнен в виде кольцевого счетчика, который в соответствии с тактовыми импульсами, поступающими на первый вход устройства последовательно формирует адреса всех ячеек блока . В блоке 1 записаны через равные интервалы по аргументу приращения всех нелинейных зависимостей, количество которых соответствует разрядности блока 1. В соответствии с адресами, формируемыми в регистре адреса, осуществляется считывание информации (в виде приращеиий функций), из блока 1, которая поступает па вторые входы коммутатора 4. Связь регистра 2 с первым входом коммутатора 4 предназначена для определения напряжения приращения по аргументу, для чего в коммутаторе 4 осуществляется анализ предыдущего и текущего состояния двух младщих разрядов регистра 2 адреса, а если их состояние изменилось в сторону уменьшения, производится инвертирование информации, считываемой из блока 1 по данному каналу. Код с регистра адреса поступает на входы цифро-аналогового преобразователя 3, на выходе которого получается пилообразное напряжение, поступающее на первые входы схем сравнения 9. На вторые входы схем сравнения 9 в качестве аргументов поступают напряжения с вторых входов устройства. В моменты равенства этих напряжений схемы сравнения 9 выдают импульсы, которые поступают в блок 5 памяти выбора нелинейности, и каждый из импульсов считывает из блока памяти выбора нелинейности содержимое одной ячейки, в которой предварительно записан адрес требуемой фуикции. Импульсы кода выбранной ячейки управляют коммутатором 4, на выходы которого нроходят нриращения заданных функций от аргумента, соответствующего выбранной ячейке блока 5 памяти выбора нелинейности.

В ячейках блока 6 памяти вывода нелиg нейности занисаны коды, которые обеспечивают вывод требуемых нелинейных зависимостей на соответствующие выходы устройства.

Импульсы с выходов коммутатора 4 считывают соответствующие ячейки блока 6 памяти Q вывода нелинейности.

С выходов блока 6 памяти вывода иелинейности ииформация поступает на соответствующие входы блока 7 реверсивных счетчиков и далее через блок 8 вывода на выходы устjg, ройства.

Таким образом, устройство позволяет азтоматически выбрать и вывести на соответствующие выходы нелинейные зависимости даже при равенстве сигналов на его вторых вхо2Q дах. Это приводит к увеличению точности вычислений по сравнению с прототипом. Кроме этого, существенно упрощена структура устройства.

Формула изобретения

Устройство для совместной работы цифроых и аналоговых вычислительных машин, соержащее блок реверсивных счетчиков, выходы которого через блок вывода подключены к выходам устройства, регистр адреса, соединенный входом с первым входом устройства, а выходами - с первым входом коммутатора и входами цифро-аналогового преобразователя и блока памяти функций, подключенного выходами ко вторым входам ко.ммутатора, причем выход цифро-аиалогового преобразователя соединен с первыми входами группы схем сравнения, вторые входы которых подключены ко вторым входам устройства, отличающееся тем, что, с целью повыщения точности и упрощения устройства, в него введены блок памяти вывода нелинейности и блок памяти выбора нелинейностей, подключенный входами к выходам группы схем сравнения, а выходами - к третьим входам коммутатора, выходы которого через блок памяти вывода иелинейностей соединены с входами блока реверсивных счетчиков.

Источники информации,

принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 333566, кл. G 06G 7/26, 1971.

2. Авторское свидетельство СССР ДЬ 504211, кл. G 061 3/00, 1973.

3. Заявка Я 1903939/24, кл. G 061 3/00, 1973, по которой принято рещение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для совместной работы цифровых и аналоговых машин | 1973 |

|

SU548871A1 |

| Устройство возведения в дробную степень | 1973 |

|

SU596941A1 |

| Аналого-цифровой нелинейный процессор | 1988 |

|

SU1575194A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| ЦИФРО-АНАЛОГОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УПРАВЛЯЮЩЕЕ | 1973 |

|

SU386409A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| Устройство для возведения в дробную степень | 1974 |

|

SU571812A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Функциональный генератор | 1981 |

|

SU962997A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

Авторы

Даты

1977-10-30—Публикация

1975-07-15—Подача