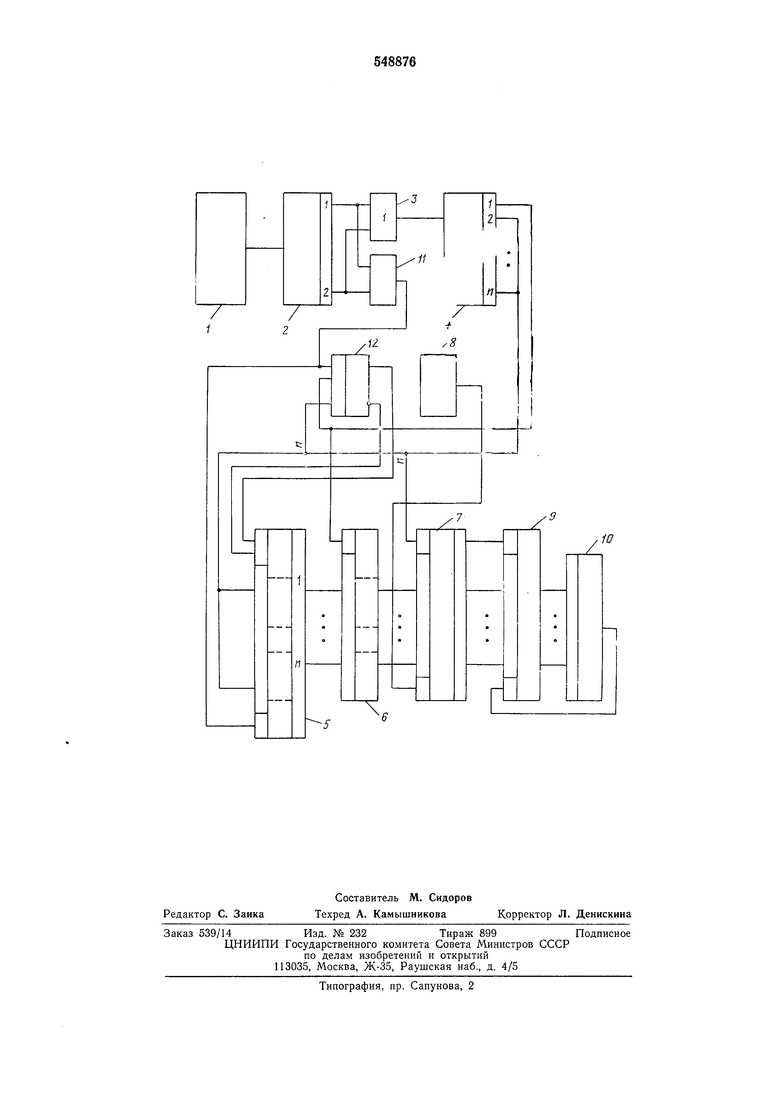

синхронизации в зависимости от способа поступления информации. Для выделения сигналов кода и синхронизации к выходам блока усилителей 2 подключены логические элементы И И и ИЛИ 3, при этом на выходе элемента ИЛИ 3 всегда будут формироваться сигналы синхронизации, а на выходе элемента И 11-сигналы кода. Сигналы синхронизации с выхода элемента ИЛИ 3 поступают на вход первого коммутатора 4, вызывая его переключение.

Первый распределенный импульс с выхода первого коммутатора 4 производит сброс регистра 6 в исходное состояние, а также поступает на первый вход триггера 12 и совместно с сигналом кода с выхода элемента И 11 производит переключение триггера в состояние «Начало (логическая единица на прямом выходе триггера 12), если информация через блок ввода информации 1 поступает в прямом порядке. В противном случае состояние триггера 12 не изменяется.

Выходы триггера 12 управляют вторым коммутатором 5 таким образом, что информация, последовательно поступающая из блока ввода 1, записывается в соответствующие ячейки памяти регистра 6, независимо от ее направления поступления. С появлением последнего синхроимпульса на выходе первого коммутатора 4 происходит сброс в исходное состояние триггера 12 и перезапись информации из регистра 6 в блок формирования массивов информации 7.

В соответствии с программой, вводимой через блок 8 задания программы, блок 7 формирования массивов информации производит обработку информации, поступившей через блок ввода 1. По окончании обработки информации с выхода блока формирования массивов информации выдается сигнал готовности информации или результатов ее обработки для их регистрации. 3tot сигнал, поступали на вход блока 9 управления производит выдачу информации с выходов блока 7 формирования массивов информации блоком вывода информации 10 с помощью блока управления 9 и сигналов синхронизации, поступающих с выхода блока вывода информации 10 на вход блока управления 9.

Технико-экономический эффект от изобретения заключается в возможности оперативиого формирования и вывода массивов информации согласно выбранной программе.

Формула изобретения

Устройство для регистрации информации, содержащее блок ввода, подключенный через последовательно соединенные блок усилителей и логический элемент ИЛИ к первому коммутатору, соединенному с вторым коммутатором, регистром и триггером, подключенным к логическому элементу И и второму коммутатору, выходы которого соединены с входами регистра, и блок управления, подключенный к блоку вывода информации, о т личающееся тем, что, с целью расширения области применения устройства, оно содерл ит блок формирования массивов информации и блок задания програм.мы, выход которого подключен к первому входу блока формирования массивов информации, второй вход которого соединен с выходом первого коммутатора, третьи входы подключены к выходам регистра, а выходы соединены с входами блока управления.

Источники информации, принятые во внимание при экспертизе:

1.Авт. св. № 398993, кл. G 07С 9/02, 1972.

2.Авт. св. № 490124, кл. G 06F 11/00, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для программного управления | 1984 |

|

SU1198461A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

Авторы

Даты

1977-02-28—Публикация

1974-10-18—Подача