Изобретение относится к вычислительной технике и может быть использоваио при построении различных специализированных вычислительных устройств и машин.

Известны устройства умножения, состоящие из трех регистров и системы функциональных сумматоров, соединенных по матричной схеме 1, 2). При вычислении суммы парных произведений в известных устройствах необходимо вместо третьего регистра использовать сумматор. При этом время вычисления суммы k парных произведений га-разрядных чисел можно представить в виде

Т сум. + ( + 1) сум. (4 /г + 4 + /в) X Х(«-1)+(А- 1)сум. ,

где /сум - время суммирования двух 2«-разрядных чисел;

/а - время суммироваиия на однозначном сумматоре;

/ь - время прохождения сигнала через элемент И.

Однако известные устройства имеют низкое быстродействие, обусловленное временем распространения сигнала переноса ио длинной цепочке сумматоров (вдоль строкп н столбца матрицы). Наиболее близким к изобретению по технической сущности является устройство для вычисления сумм произведений, содержащее регистры множимого и множителя, сумматор и матрицу модулей сложения, выходы которой соедииены с первыми входами сумматора, а первые входы матрицы модулей сложеиия соединены с прямыми выходами регистра множимого 3. Это устройство предназиачеио для вычисления суммы произведений только положительных чисел. В широком же классе задач, в частности при решении системы линейных алгебраических уравиеппй, возникает необходимость в перемножении матриц, элементы которых - числа с различными знаками. Целью изобретения является расширение

класса решаемых задач. В описываемом устройстве это достигается тем, что оио содержит блок анализа знака, блоки элементов «И и блок элементов «2И-ИЛИ, информациоиные входы которого соединены с прямыми и пнверсными выходами регистра множителя, а выходы соединены со вторыми входами матрицы модулей сложения, третьи входы которой иодключены к выходам иервого блока элементов «И, информационные входы которых соединены с прямыми выходами регистра множимого, подключенного инверсными выходами к информационным входам второго блока элементов «И, подключенных выходами ко вторым входам сумматора, входы блока

анализа знака соедииены с выходами знаковых разрядов регистров множимого и множителя, а выход подключен к управляющим входам первого и второго блоков элементов «И, блока элементов «2И-ИЛИ и ко входам знакового, дополнительных и младшего разрядов сумматора.

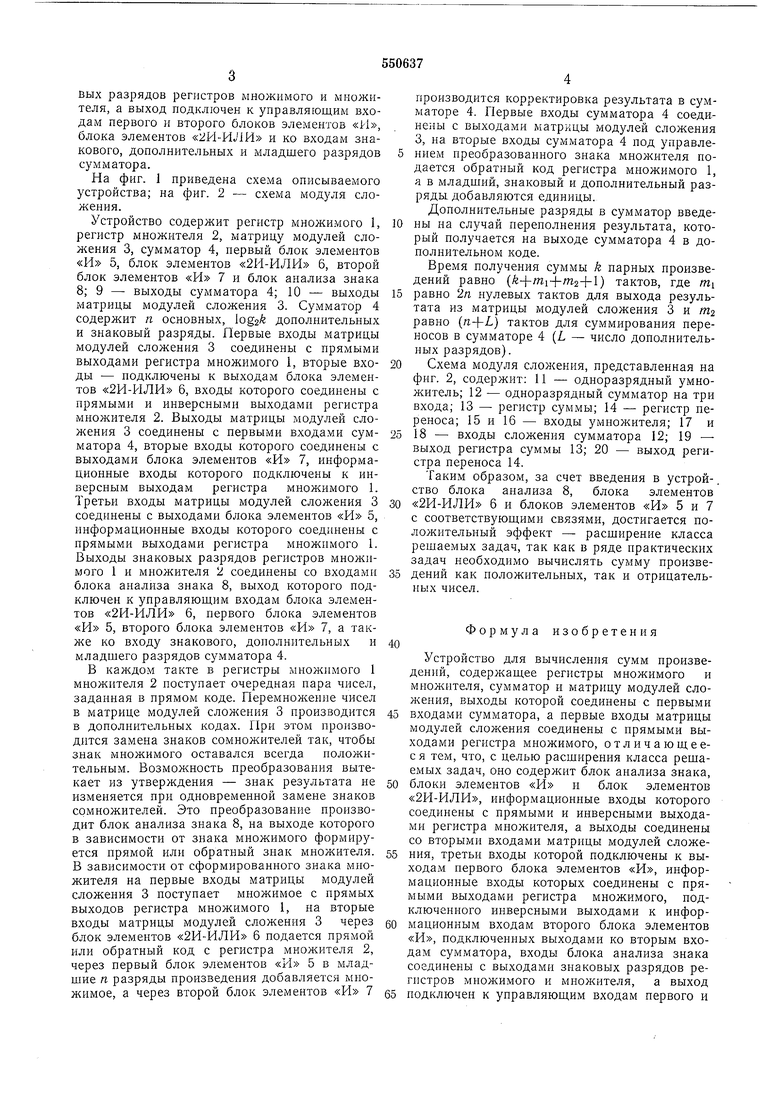

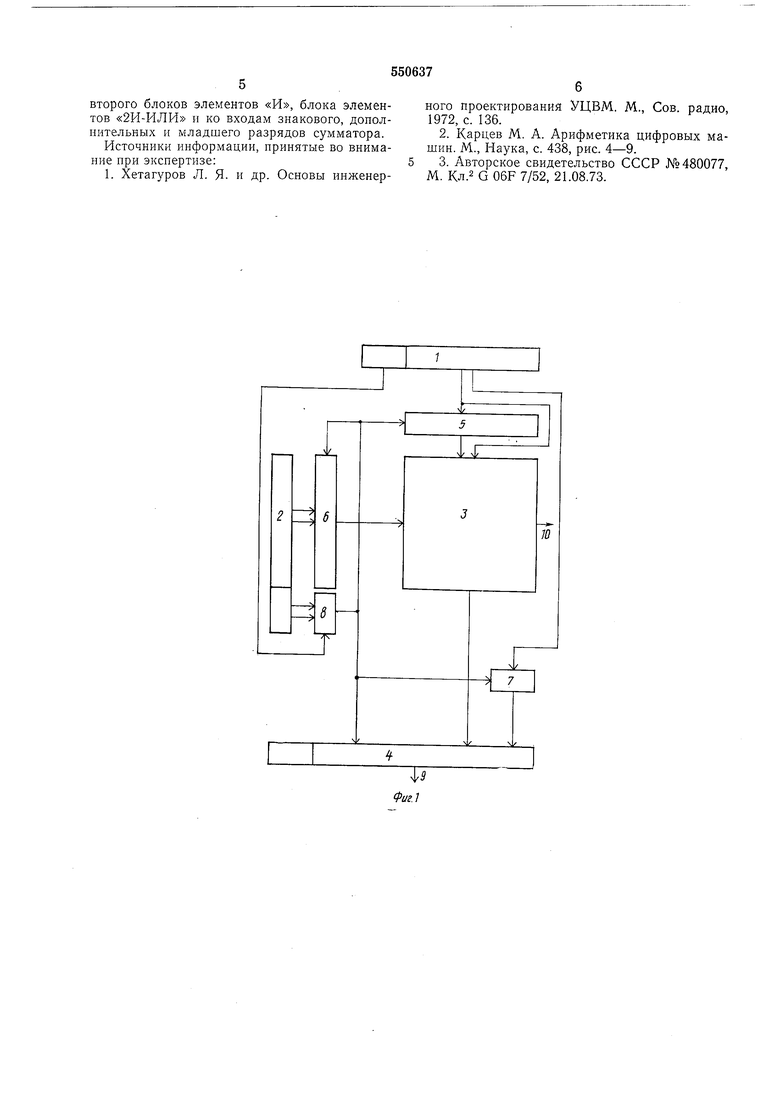

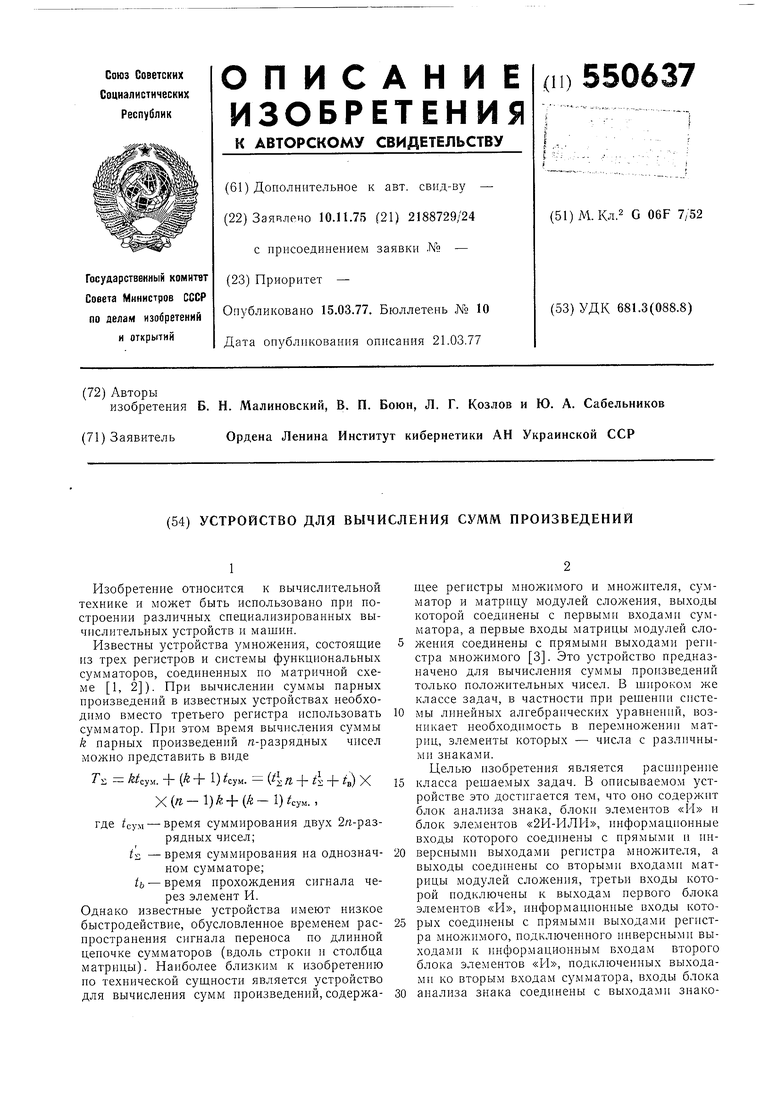

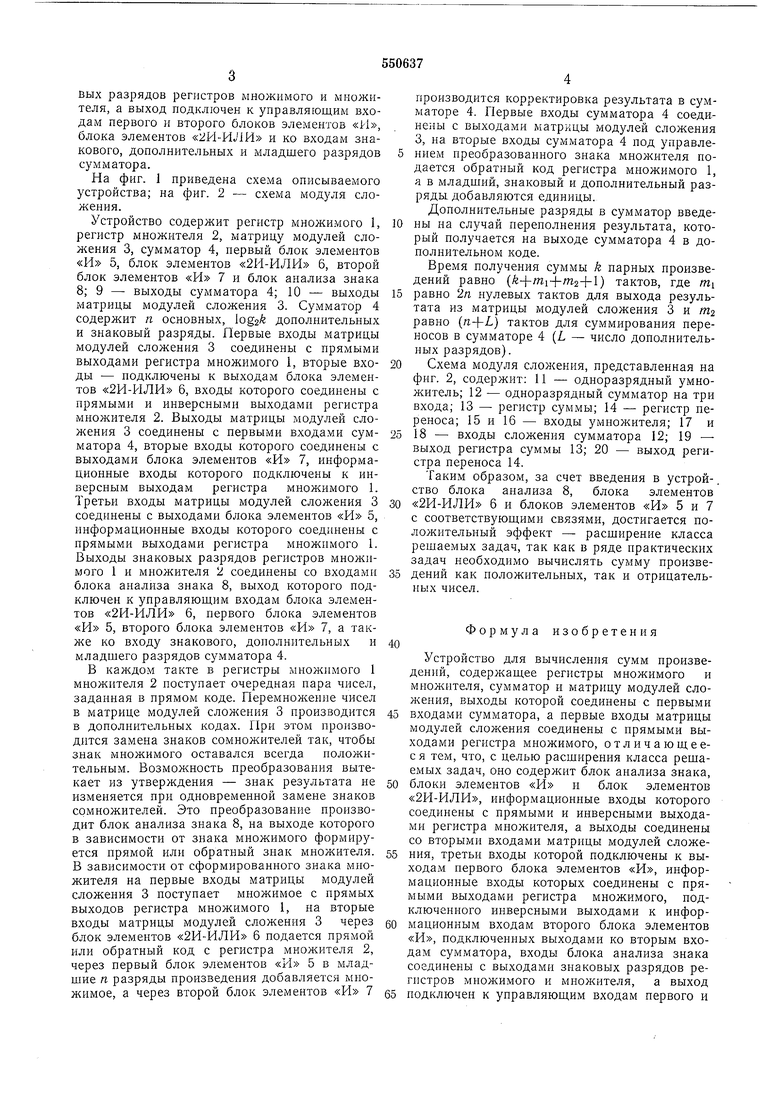

На фиг. 1 приведена схема описываемого устройства; на фиг. 2 - схема модуля сложения.

Устройство содержит регистр множимого 1, регистр множителя 2, матрицу модулей сложения 3, сумматор 4, первый блок элементов «И 5, блок элементов «2И-ИЛИ 6, второй блок элементов «И 7 и блок анализа знака 8; 9 - выходы сумматора 4; 10 - выходы матрицы модулей сложения 3. Сумматор 4 содержит я основных, Iog2 дополнительных и знаковый разряды. Первые входы матрицы модулей сложения 3 соединены с прямыми выходами регистра множимого 1, вторые входы - подключены к выходам блока элементов «2И-ИЛИ 6, входы которого соединены с прямыми и инверсными выходами регистра множителя 2. Выходы матрицы модулей сложения 3 соединены с первыми входами сумматора 4, вторые входы которого соединены с выходами блока элементов «И 7, информационные входы которого подключены к инверсным выходам регистра множимого 1. Третьи входы матрицы модулей сложения 3 соединены с выходами блока элементов «И 5, информационные входы которого соединены с прямыми выходами регистра множимого 1. Выходы знаковых разрядов регистров множпмого 1 и множителя 2 соединены со входами блока анализа знака 8, выход которого подключен к управляющим входам блока элементов «2И-ИЛИ 6, первого блока элементов «И 5, второго блока элементов «И 7, а также ко входу знакового, дополнительных и младщего разрядов сумматора 4.

В каждом такте в регистры множимого 1 множителя 2 поступает очередная пара чисел, заданная в прямом коде. Перемножение чисел в матрице модулей сложения 3 производится в дополнительных кодах. При этом производится замена знаков сомножителей так, чтобы знак множимого оставался всегда положительным. Возможность преобразования вытекает из утверждения - знак результата не изменяется при одновременной замене знаков сомножителей. Это преобразование производит блок анализа знака 8, на выходе которого в зависимости от знака множимого формируется прямой или обратный знак множителя. В зависимости от сформированного знака множителя на первые входы матрицы модулей сложения 3 поступает множимое с прямых выходов регистра множимого 1, на вторые входы матрицы модулей сложения 3 через блок элементов «2И-ИЛИ 6 подается прямой или обратный код с регистра множителя 2, через первый блок элементов «И 5 в младщие я разряды произведения добавляется множимое, а через второй блок элементов «И 7

производится корректировка результата в сумматоре 4. Первые входы сумматора 4 соединены с выходами матрицы модулей сложения 3, на вторые входы сумматора 4 под управлением преобразовапного знака множителя подается обратный код регистра множимого 1, а в младщий, знаковый и дополнительный разряды добавляются единицы. Дополнительные разряды в сумматор введены на случай переполнения результата, который получается на выходе сумматора 4 в дополнительном коде.

Время получения суммы k парных произведений равно (k+mi+m -i-l) тактов, где mi

равно 2п нулевых тактов для выхода результата из матрицы модулей сложения 13 и /Пг равно (n-}-L) тактов для суммирования переносов в сумматоре 4 (L - число дополнительных разрядов).

Схема модуля сложения, представленная на фиг. 2, содержит: 11 - одноразрядный умножитель; 12 - одноразрядный сумматор на три входа; 13 - регистр суммы; 14 - регистр переноса; 15 и 16 - входы умножителя; 17 и

18 - входы сложения сумматора 12; 19 - выход регистра суммы 13; 20 - выход регистра переноса 14.

Таким образом, за счет введения в устрой-. ство блока анализа 8, блока элементов

«2И-ИЛИ 6 и блоков элементов «И 5 и 7 с соответствующими связями, достигается положительный эффект - расширение класса решаемых задач, так как в ряде практических задач необходимо вычислять сумму произведений как положительных, так и отрицательных чисел.

Формула изобретения

Устройство для вычисления сумм произведений, содержащее регистры множимого и множителя, сумматор и матрицу модулей сложения, выходы которой соединены с первыми

входами сзмматора, а первые входы матрицы модулей сложения соединены с прямыми выходами регистра множимого, отличающееся тем, что, с целью расширения класса рещаемых задач, оно содержит блок анализа знака,

блоки элементов «И и блок элементов «2И-ИЛИ, информационные входы которого соединены с прямыми и инверсными выходами регистра множителя, а выходы соединены со вторыми входами матрицы модулей сложения, третьи входы которой подключены к выходам первого блока элементов «И, информационные входы которых соединены с прямыми выходами регистра множимого, подключенного инверсными выходами к информационным входам второго блока элементов «И, подключенных выходами ко вторым входам сумматора, входы блока анализа знака соединены с выходами знаковых разрядов регистров множимого и множителя, а выход

подключен к управляющим входам первого и второго блоков элементов «И, блока элементов «2И-ИЛИ и ко входам знакового, дополнительных и младшего разрядов сумматора. Источники информации, принятые во внимание при экспертизе: 1. Хетагуров Л. Я. и др. Основы инженеркого проектирования УЦВМ. М., Сов. радио, 1972, с. 136. 2.Карцев М. А. Арифметика цифровых машин. М., Наука, с. 438, рис. 4-9. 3.Авторское свидетельство СССР №480077, М. Кл. G 06F 7/52, 21.08.73.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1978 |

|

SU860062A1 |

| Накапливающий перемножитель | 1981 |

|

SU987618A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| Устройство для вычисления сумм произведений | 1975 |

|

SU561963A2 |

| Устройство для умножения @ -разрядных чисел | 1984 |

|

SU1256018A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

ФигЛ

J3

Авторы

Даты

1977-03-15—Публикация

1975-11-10—Подача