(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Устройство для умножения | 1981 |

|

SU999043A1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| Устройство для умножения | 1979 |

|

SU960804A1 |

| Вычислительное устройство | 1981 |

|

SU997030A1 |

| Устройство для умножения | 1981 |

|

SU991414A1 |

| Устройство для умножения | 1981 |

|

SU1005035A1 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Устройство для вычисления суммы произведений | 1981 |

|

SU978144A1 |

1

Иэобретеиие относится к цифровой вычислительной технике и может Gttib . использовано при построении специал91зированных устройств.

Известно устройство для умножения, содержащее регистры множимого и множителя, сумматор и матрицу модулей, выход которой соединен со входом сумматора, а входы подключены к клсодам регистров Ul .

Недостаток этого устройства - малое быстродействие.

Более высоким быстродействием обладает устройство, содержгщее регистры, сумматор, матрицу модулей и блок анализа 2.

Однако данное устройство предназначено для вычисления произведений положительных чисел.

№1иболее близким к предлагаемому является устройство щя умножения, содержащее регистры множимого и множителя, сумматор, матрицу модулей сложения, блок анализа знака, блоки , элементов И и блок элементов 2И-ИЛИ. Выходы матрищ модулей сложения соединены с первыми входами сумматора, а первые входы - с прямыми выходами регистра множимого. Информационные входыблока элементов 2И-ИЛИ соединены с прямыми- и инверсными выходакш регистра множителя, а выходы соединены со вторыми входами- матрицы модулей сложения, третьи входы которой подключены к выходам первого блока элементов И, информационные входа КОТ01ЯЛХ сое юнены с прямьчда выходами регистра кшожимого, подключенного инверсными выходами к информационtoным входам второго блока элементов И, Подключенных выходами ко вторим входам сумматора. Входы блока анализа знака соединены с выходами знаковых разрядов регистров, а выход

15 подключен к управляющим входам первого и второго блоков элементов И, блока элементов 2И-ИЛИ и ко входам знакового, дополнительных и младшего разрядов сумматора f3 .

20

Недостаток этого устройства - невысокое быстродействие, которое связано с невозможностью получения результата старшими разрядгши вперед (вначале вычисляются значения мпад25ших раэрядов результата).

Цель изобретения - повьниение быстродействия.

Поставленная цель достигается тем, что в устройство, содержащее

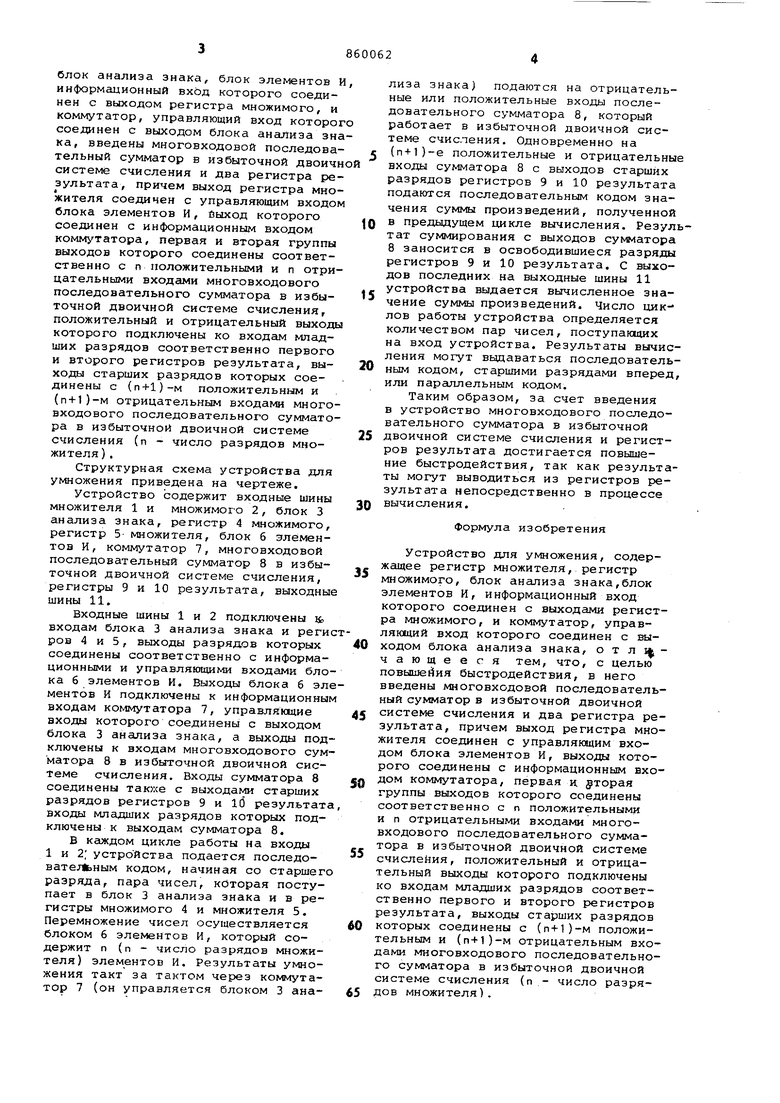

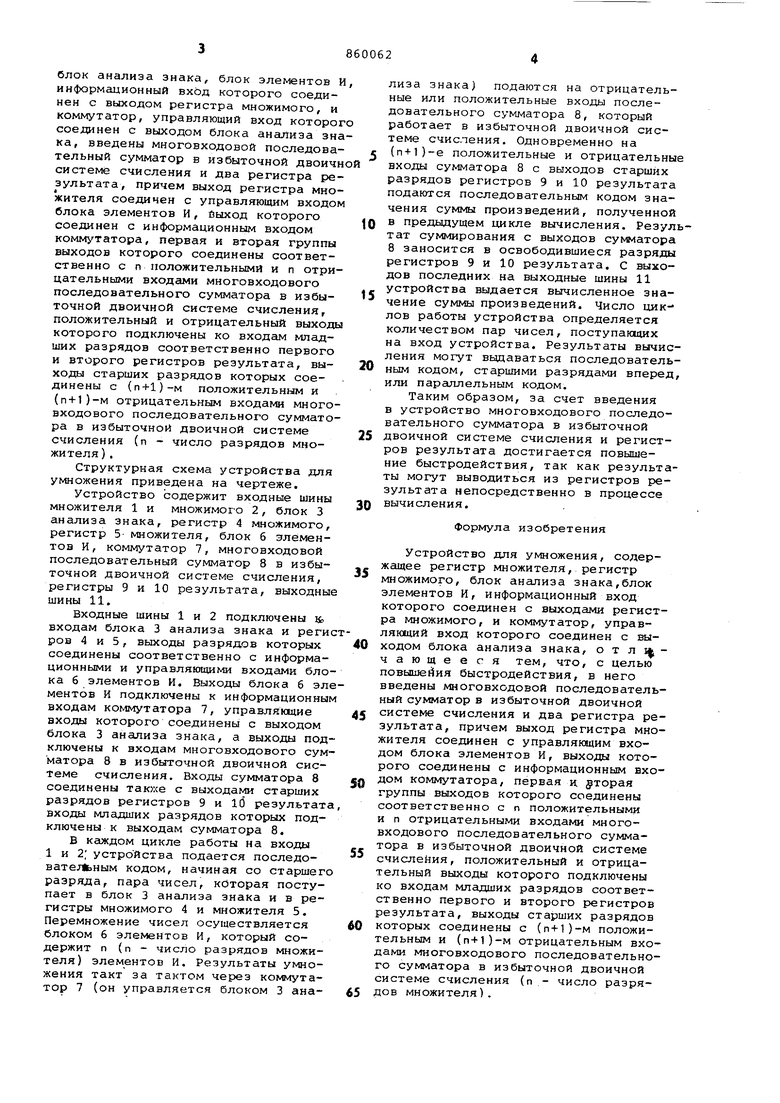

30 регистр множителя, регистр множимого. блок анализа знака, блок элементов информационный вход которого соединен с выходом регистра множимого, и коммутатор, управляющий вход которо соединен с выходом блока анализа зн ка, введены многовходовой последова тельный сумматор в избыточной двоич системе счисления и два регистра ре зультата, причем выход регистра мно жителя соединен с управляющим входо блока элементов И, быход которого соединен с информационным входом коммутатора, первая и вторая группы выходов которого соединены соответственно с п положительными и п отри цательными входами многовходового ггоследовательного сумматора в избыточной двоичной системе счисления, положительный и отрицательный выход которого подключены ко входам младших разрядов соответственно первого и второго регистров результата, выходы старших разрядов которых соединены с (п+1)-м положительным и (п+1)-м отрицательным входами много входового последовательного суммато ра в избыточной двоичной системе счисления (п - число разрядов множителя ) . Структурная схема устройства для умножения приведена на чертеже. Устройство содержит входные шины множителя 1 и множимого 2, блок 3 анализа знака, регистр 4 множимого, регистр 5- множителя, блок 6 элементов И, коммутатор 7, многовходовой последовательный сумматор 8 в избыточной двоичной системе счисления, регистры 9 и 10 результата, выходны шины 11. Входные шины 1 и 2 подключены ifc входам блока 3 анализа знака и реги ров 4 и 5, выходы разрядов которых соединены соответственно с информационными и управляющими входсми бло ка 6 элементов И. Выходы блока 6 эл ментов И подключены к информационны входам коммутатора 7, управляющие входы которого соединены с выходом блока 3 анализа знака, а выходы под ключены к входам многовходового сум матора 8 в избыточной двоичной системе счисления. Входы сумматора 8 соединены также с выходами старших разрядов регистров 9 и 10 результат входы младших разрядов которых подключены к выходам сумматора 8, В каждом цикле работы на входы 1 и 2; устройства подается последовательным кодом, начиная со старшег разряда, пара чисел, которая поступает в блок 3 анализа знака и в регистры множимого 4 и множителя 5. Перемножение чисел осуществляется блоком 6 элементов И, который содержит п (п - число разрядов множителя) элементов И. Результаты умножения такт за тактом через кокмутатор 7 (он управляется блоком 3 анализа знака) подаются на отрицательные или положительные входы последовательного сумматора 8, который работает в избыточной двоичной системе счисления. Одновременно на (п+1)-е положительные и отрицательные входы сумматора 8 с выходов старших разрядов регистров 9 и 10 результата подаются последовательным кодом значения суммы произведений, полученной в предыдущем цикле вычисления. Результат суммирования с выходов сумматора 8 заносится в освободившиеся разряды регистров 9 и 10 результата, С выходов последних на выходные шины 11 устройства выдается вычисленное значение суммы произведений. Число циклов работы устройства определяется количеством пар чисел, поступающих на вход устройства. Результаты вычисления могут выдаваться последовательным кодом, старшими разрядами вперед, или параллельным кодом. Таким образом, за счет введения в устройство многовходового последовательного сумматора в избыточной двоичной системе счисления и регистров результата достигается повышение быстродействия, так как результаты могут выводиться из регистров результата непосредственно в процессе вычисления. Формула изобретения Устройство для умножения, содержащее регистр множителя, регистр множимого, блок анализа знака,блок элементов И, информационный вход которого соединен с выходами регистра множимого, и коммутатор, управляющий вход которого соединен с выходом блока анализа знака, о т л i чающееся тем, что, с целью повышения быстродействия, в него введены лтоговходовой последовательный сумматор в избыточной двоичной системе счисления и два регистра результата, причем выход регистра множителя соединен с управлякадим входом блока элементов И, выходы которого соединены с информационным входом коммутатора, первая к §торая группы выходов которого соединены соответственно с п положительными и п отрицательными входами многовходового последовательного сумматора в избыточной двоичной системе счисления, положительный и отрицательный выходы которого подключены ко входам младших разрядов соответственно первого и второго регистров результата, выходы старших разрядов которых соединены с (п+1)-м положительным и (п-И)-м отрицательным входами многовходового последовательного сумматора в избыточной двоичной системе счисления (п - число разрядов множителя).

Источники информации, принятые во внимание при экспертизе

свидетельство СССР 06 F 7/52, 191.

свидетельство СССР 06 F 7/52, 1977

Авторы

Даты

1981-08-30—Публикация

1978-10-11—Подача