: Изобретение относится к запоминаю щим устройствам и может быть использовано при построении систем, имеющих несколько блоков ввода данный. Известно устройство, содержащее накопитель, подключенный к блокам приема и выдачи чисел, датчику кода адреса и блоку контроля, элементы задержки, элементы И, ИЛИ и блок переключения l . Недостатком данного устройства яв ляется наличие элементов задержки, двойное контрольное считывание, а также прием инфсфмации только от однего источника, что снижает его наде ность. Из рзвестных устройств наиболее близким техническим ранением к предлагаемому является устройство, содер жащее нес1 олько связанных через общую шину (магистраль) устройств обра ботки (УО), запоминающее устройс;гво (ЗУ) для хранения групп символов от любого УО, кодер (схема анализа запа нения блока ЗУ), обеспечивакщий зада ные двоичные значения нескольких битов контрольного кода, когда бит про верки на четкость указывает на наличие ошибки в непроверенных битах, де кодер (схема анализа заполнения блока ЗУ), вырабатывающий несколько с &вокупностей сигналов для локализации ошибки в битах данных. В этом устройстве применяется способ запоминания данных с битами тфоверки на чёткость, поступеоощих от нескольких устрсЛств ввода-вывода. Несколько совокупностей сигналов, вьч абатываемые декодером, характеризуются первым заданшлм параметром, указыванедим, когда группа записанных в ЗУ нвпроверенгалх дан{а1Х от любого УО не удовлетворяет требованиям четности, и обвспечивакадим съем данных с шины 2. Недостатком этого устройства является слсякная система выявления ошибки, что снижает «йдстродействие и надежность устйрйства. Цель изобретения - повыиение надежности устройства. . Поставленная цель достигается тем, что запоминшовкее устройство с самоконтролем, содержащее накопитель, выполненньА на регистрах сдвига, блок контроля на нечетность, первый элемент И, пороговый элемент, блок индикации, информгщнонные шины, шину разрешения записи, выходные шины и шину сигналов считывания, причем одни выходы регистров сдвига подключены ко

ходу порогового элемента, выход котоого соединен с первым входом первого элемента И, введены группа триггеров, блок местного управления, элеент ИЛИ, второй элемент И, два триггера, формирователь сигнала конца заиси, две группы формирователей сигналов признака, группа элементов И, ины конца записи и шину сигналов сбоя, причем одни из входов триггеров группы подключены к информационным шинам и первому входу блока местного управления, единичные выходы к первым входам регистров сдвига соответственно, а нулевые выходы - ко входу блока контроля на нечетность, выход которого соединен с первым входом первого триггера, второй вход которого подключен ко вторым входам регистров сдвига, первому входу второго триггера и шине разрешения записи, третий вход - к другим входам триггеров группы, выходу блока местного управления и первому входу элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, а выход - с третьими входами регистров сдвига, единичный выход первого триггера подключен к первому входу блока индикации, а нулевой выход ко второму входу блока местного управления и первым входам формирователей сигналов признака первой группы, вторые входы которых соединены с выходом порогового элемента и первым входом первого элемента И, третьи входы соответственно с шинами конца записи и входами формирователя сигнала конца записи, выход которого подключен ко второму входу первого элемента И, выхрд которого соединен с четвертым входом первого триггера, второй вход второго триггера подключен к шине сигналов считывания и первому входу второго элемента И, а третий вход - ко второму входу блока индикации и шине сигналов сбоя, единичный выход второго триггера соединен со , вторым входом второго элемента И и первыми входами элементов И группы, вторые входы и выходы которых подключены соответственно к другим выходам регистров сдвига и к первым входам формирователей сигналов признака звторой группы, выходы которых соед1 нены с выходными шинами, нулевой второго триггера соединен с четвертыми входами формирователей сигналов признака первой группы, выход одного из которых подключен ко второму входу одного из формирователей сигналов признака второй группы, а выход другого - ко вторым входам других формирователей сигналов признака второй группы.

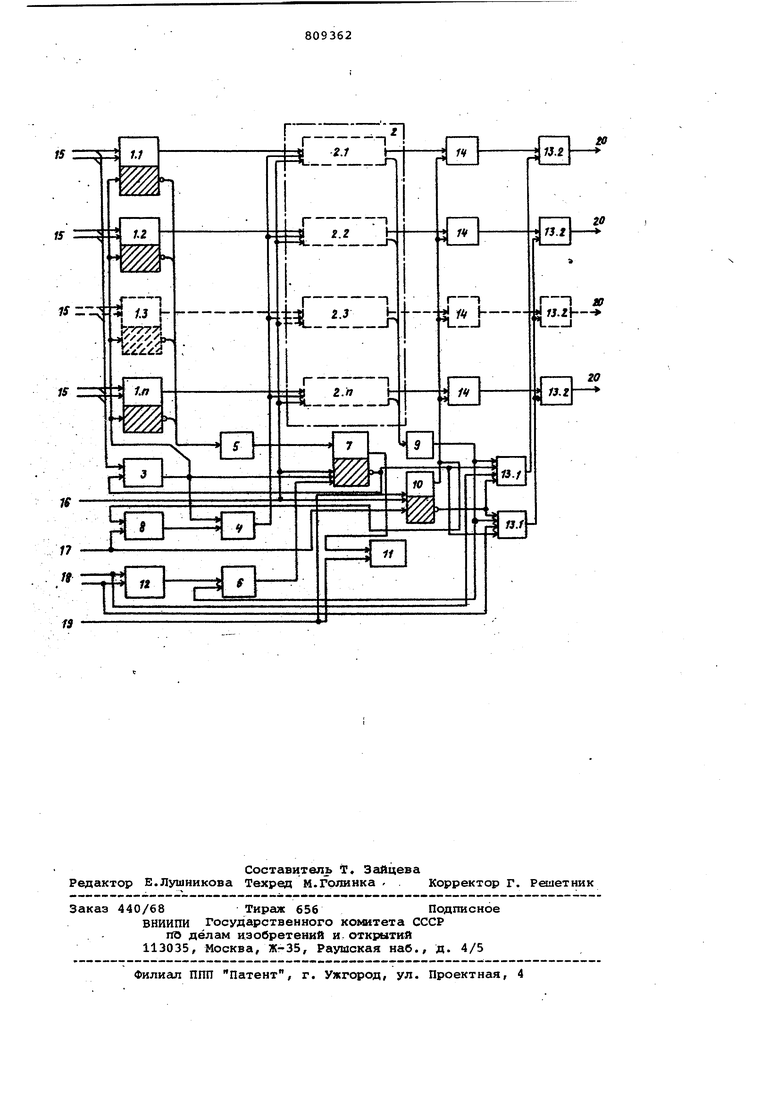

На чертеже представлена функциональная схема устройства.

Устройство содержит группу триггеров 1.1-1,п, являющихся R-S триггерами, накопитель 2, выполненный на регистрах 2.1-2.П сдвига, блок 3 местного управления, элемент ИЛИ 4, блок 5 контроля на нечетность, первый элемент , И 6, первый триггер 7, являющийся J-K триггером, второй элемент И 8, пороговый элемент 9, второй триггер 10, являющийся J-K триггером, рлок 11 индикации, формирователь 12 сигнала конца записи, первую 13.1 и вторую 13.2 группы формирователей сигналов признака, группу элементов И 14 шины 15 информационные, шину 16 разрешения записи, шину 17 сигналов считывания, шины 18 конца записи, шину 19 сигналов сбоя и выходные Ьины 20.

Одни выходы регистров 2.1-2. п сдвига подключены ко входу порогового элемента 9, выход которого соединен с первым входом первого элемента И 6. Одни из входов триггеров 1.1-1. п группы подключены к информационным шинам 15 и первому входу блока 3 местного управления. Единичные выходы триггеров 1.1-l.n группы подключены к первым входам регистров 2.1-2.П сдвига соответственно, а нулевые выходы - ко входу блока 5 контроля на нечетность, выход которого соединен с первым входом первого триггера 7, второй вход которого подключен ко вторым входам регистров 2.1-2.п,сдвига, первому входу второго триггера 10 и шине 16 разрешения записи. Третий вход первого триггера 7 подключен к другим входам триггеров 1.1-l.n группы, выходу блока 3 местного управления и первому входу элемента ИЛИ 4, второй вход которого соединен с выходом второго элемента И 8, а выход - с третьими входами регистро 2.1-2.П сдвига. Единичный выход первого триггера 7 подключен к первому входу блока 11 индикации, а нулевой выход - ко второму входу блока 3 местного управления и первым входам формирователей 13.1 сигналов признака первой группы, вторые входы которых соединены с выходом поро1 Ьвого элемента 9 и первым входом первого элемента И 6. Третьи входы формирователей 13.1 сигналов признака первой группы соединены соответственно с шинами 18 конца записи и входами формирователя 12 сигнала конца записи, выход которого подключен ко второму входу первого элемента И 6, выход которого соединен с четвертЕлм входом первого триггера 7. Второй вход второго триггера 10 подключен к шине 17 сигналов считывания и первому входу второго элемента И 8, а третий входко второму входу блока 11 индикации и шине 19 сигналов сбоя. Единичный выход второго триггера 10 соединен со вторым входом второго элемента И 8 и первыми входами элементов И группы 14, вторые входы и выходы которых подключены соответственно к другим входс1М регистров 2.1-2.П сдвига и к первым входам формирователей 13.2 сигналов признака второй группы, выходы которых соединены с выходными шинами 20. Нулевой выход второго три гера 10 соединен с четвертыми входами формирователей 13.1 сигналов-пpиз ка первой группы, выход одного из ко торых подключён ко второму входу одного из формирователей 13.2 сигналов рризнака второй группы, а выход другого - ко вторым входам других форми рователей 13.2 сигналов признака вто рой группы. Устройство работает следующим образом. Символы информации поступают по информационным шинам 15 в параллельном коде. Каждый символ имеет хотя б один значащий бит, причем одновременность поступления и идентичность по длительности битов каждого символ не обязательна. В исходном состоянии R-S триггеры 1-группы 1.1-1.П находятся в нуле вом положении (верхний по схеме выхо имеет состояние логического нуля), накопитель 2 свободен от информации, первый 7 и второй 10 триггеры находя ся в нулевом состоянии, так как шина 16 разрешения записи имеет состоя ние логического нуля. Йторой элемент И 8, формирователи сигналов признака первой 13.1 и второй 13.2 групп и элементы И группы 14 также находятся в состоянии логического нуля. При подаче потенциала логической единицы на шину 16 разриаения записи подготавливаются к работе регистры 2.1-2. п сдвига накопителя 2 и первый 7 и второй 10 триггеры.Затем по информационным шинс1М 15 посимвольно поступает информация для записи в накопитель 2. Количество битов в кэ1ждом, сиМ воле зависит от кода и значимости его При этом R-S триггеры 1 группы 1.11.п, на входах которых появляется сигнал логического нуля, устанавливаются в единичное состояние. На установочных входах соответствующих регистров 2.1-2. п сдвига и на выходе блока 3шестбго управления появляется логичес кая единица, а после окончания послед него бита, входящего в данный символ - логический нуль. Поступивший на вход символ записывается в первые ячейки памяти регистров 2.1-2.П сдвига г После поступления второго символа, первый сдвинется на одну позицию вправо, а второй запишется на его место и т.д. После записи т-го символа на единичных выходах регистров 2.1-2.п сдви га появляются логические единицы, соответствующие первому символу. На выходе порогового элемента 9 появляется логическая единица, которая подготавливает к работе формирователи сигналов признака первой 13.1 и второй 13.2 групп и закрывает первый элемент И 6. Затем на шину 18 конца записи поступает сигнал логической единицы, по которому на выходах формирователей сигналов признаки групп 13.1 и 13.2 появляется символ призна-, ка информации, принадлежащей одному из блоков ввода, являющийся одновременно заявкой на обслуживание накопителя 2 (на чертеже изображена схема для случая подключения двух блоков ввода, не показанных на чертеже). После этого по шине 17 сигналов считывания поступают импульсы, количество которых должно быть (т+1), для вывода информации из накопителя 2. Первым импульсом выводится символ признака и переключается второй триггер 10, который единичным выходом от крывает элементы И группы 14 и второй элемент И 8, Остальные m импульсов поступают через элемент И 8 и элемент ИЛИ 4, на входы регистров 2.12.п сдвига и последовательно выводят информацию из накопителя 2. Затем на шину 16 разрешения записи подается сигнал логического нуля, устанавливающий в исходное состояние триггер 10. Если на входы блока 5 контроля на нечетность поступает символ, имеющий четное число бит, то на первом (установочном) входе первого триггеpa 7 появляется логическая единица, а по заднему фронту последнего бита, входящего в данный символ, происходит переключение триггера 7. При этом включается блок 11 икдиксщии, закрывается блок 3 местного управления, запрещая дальнейшую запись информации в накопитель 2, и закрываются формирователи сигналов признака групп 13.1 и 13.2. После этого на шину 16 разрешения записи поступает сигнал логического нуля и устройство устанавливается в исходное состояние. Вели количество записанных в накопитель 2 символов окажется меньше т, то пороговый элемент 9 не изменяет своего состояния, а появление сигнала конца записи на шине 18 клзывает срабатывание фсфмирователя 12 сигнала конца записи, первого элемента И 6 и триггера 7. После появления сигнала логического нуля на шине 16 устройство устанавливается в исходное состояние. Если количество поступивших символов окажется больше т, то срабатывают пороговый элемент 9 и триггер 7. После появления сигнала логического нуля на шине 16 устройство устанавливается в исходное состояние. Если при выводе информации из накопителя 2 произойдет сбой кангша передачи даншлх, то на шине 19 сигналов сбоя появится сигнал, который включает блок 11 индикации, фиксирующий ошибку, и переключает в исходное состояние триггер 10, который закрывает элементы И группы 14, служащие для вывода информации из накопителя 2, Во всех случаях включения блока 11 инднКсщии требуется повторение записи информации Б накопитель 2. Технико-эконолшческие преимущества предлагаемого устройства заключаются в том, что оно позволяет записывать информацию с нескольких блоков ввода данных, а также применяемый в нем спо соб обнаружения ошибок в записываемой информации и возможность выполнения устройства на интегральных схемах с высоким уровнем интеграции снижают время обнаружения ошибок, что повышает надежность работы устройства. Формула изобретения Запоминающее устройство с самоконтролем, содержащее накопитель, выполненный на регистрах сдвига, блок контроля на нечетность, первый элемент И, пороговый элемент, блок индикации, информационные шины, шину раз решения записи, выходные шины и шину сигналов считывания, причем одни выходы регистров сдвига подключены ко входу порогового элемента, выход которого соединен с первым входом первого элемента И, отличающе еся тем/ что, с целью повышения надежности устройства, оно содержит группу триггеров, блок местного упра ления, элемент ИЛИ, второй элемент И два триггера, формирователь сигнала конца записи, две группы формировате лей сигналов признака, группу элемен .тов И/ шины .конца записи и шину сигналов сбоя,причем одни из входов три гёров группы подключены к инфо мационным шинам и первому входу блока местного упра.чления, еди11ичны1 „,ьыг . |Ходы - к первым входам регистр6в сдв га соответственно, а нулевые выходыко входу блока контроля на нечетност выход которого соединен с первым вхо рцом первого триггера, второй вход ко Topoi o подключен ко-вторым входам ре гистров сдвига, первому входу второ-го триггера и шине разрешения записи, третий вход - к другим входам триггеров группы, выходу блока местного управления и первому входу элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, а выход с TpeTbHNM входами регистров сдвига, единичный выход первого триггера подключен к первому входу блока индикации , а нулевой выход - ко второму входу блока местного управления и первым входам формирователей сигналов признака первой группы, вторые входы которых соединены с выходом порогового элемента и первым входомпервого элемента И, третьи входы соответственно с шинами конца записи и входами формирователя сигнала конца записи, выход которого подключен ко второму входу первого элемента И, выход которого соединен с четвертым входом первого триггера, второй вход второго триггера подключен к шине сигналов считывания и первому входу второго элемента И, а третий вход- ко второму входу блока индикации и шине сигналов сбоя, единичный выход второго триггера соединен со вторым входом второго элемента И и первыми входами элементов И группы, вторые входы и выходы которых подключены соответственно к другим выходам регистров сдвира и к первым входам форл1ирователей сигналов признака второй группы, выходы которых соединена с выходными mHHafvoi, нулевой выход второго триггера соединен с четвертыми входами формирователя сигналов признака первой группы, выход одного из которых подключен ко второму входу одного из формирователей сигналов признака второй группы, а выход, другого - ко вторым входам других формирователей сигналов признака второй группы. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 600618, кл. G 11 С 29/00, 1976. 2.Патент США № 3672853, кл. G 11 С 29/00, опублик. 1972 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2144267C1 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168282C1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Логическое запоминающее устройство | 1979 |

|

SU790017A1 |

| Генератор двоичной последовательности | 1990 |

|

SU1709505A1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

Авторы

Даты

1981-02-28—Публикация

1979-05-04—Подача