1

Изобретение относится к вычислительной технике и предназначено для применения в мультинрограммных вычислительных системах.

Известно устройство для защиты памяти, недостатком которого является то, что размеш,ение программ в памяти мультипрограммных вычислительных систем, использующих это устройство, возможно только внутри зоны памяти, заданной граничными адресами 1.

Известно также наиболее близкое к изобретению по техническому рещению устройство для защиты памяти, содержащее носледовательпо соединенные дещифратор адресов зон и блок сравнения, входы которых подключены к первому и второму входам устройства 2.

Однако такое устройство не обеспечивает дифференцированной защиты зон памяти в мультипрограммных вычислительных системах, каждая из которых предназначена только для определенного характера обращения, что не нредохраняет от искажений информации при ощибочных обращениях, например при обращении на запись или считывание с гащением в зону, предназначенную для считывания с восстановлением, и, следовательно, приводит к необходимости применения программных способов защиты, усложняющих мультипрограммирование, к увеличению объема памяти и времени выполнения программ.

Цель изобретения - повышение иадежности устройства.

Это достигается тем, что в устройстве установлены дополнительные блоки сравнения, входы которых соединены с выходом дещифратора адресов зон и вторым входом устройства, подключенный к третьему входу устройства регистр признака обращения, соединенный с выходом данного регистра дещифратор признака обращения и элементы И и ИЛИ. Иервые входы каждой пары элементов И связаны с выходами соответствующего блока сравнения, вторые входы - с выходами дешифратора признака обращения, а выходы - с соответствующими входами первого и второго элементов Р1ЛИ, подключенных своими выходами к выходам устройства.

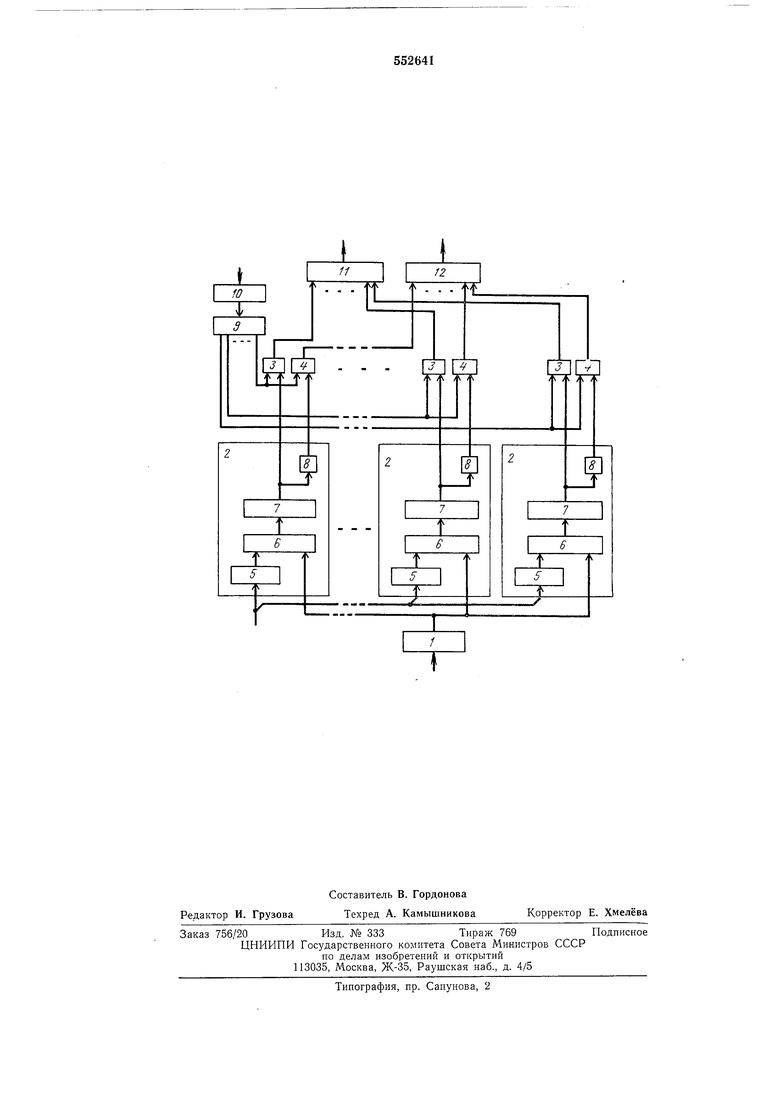

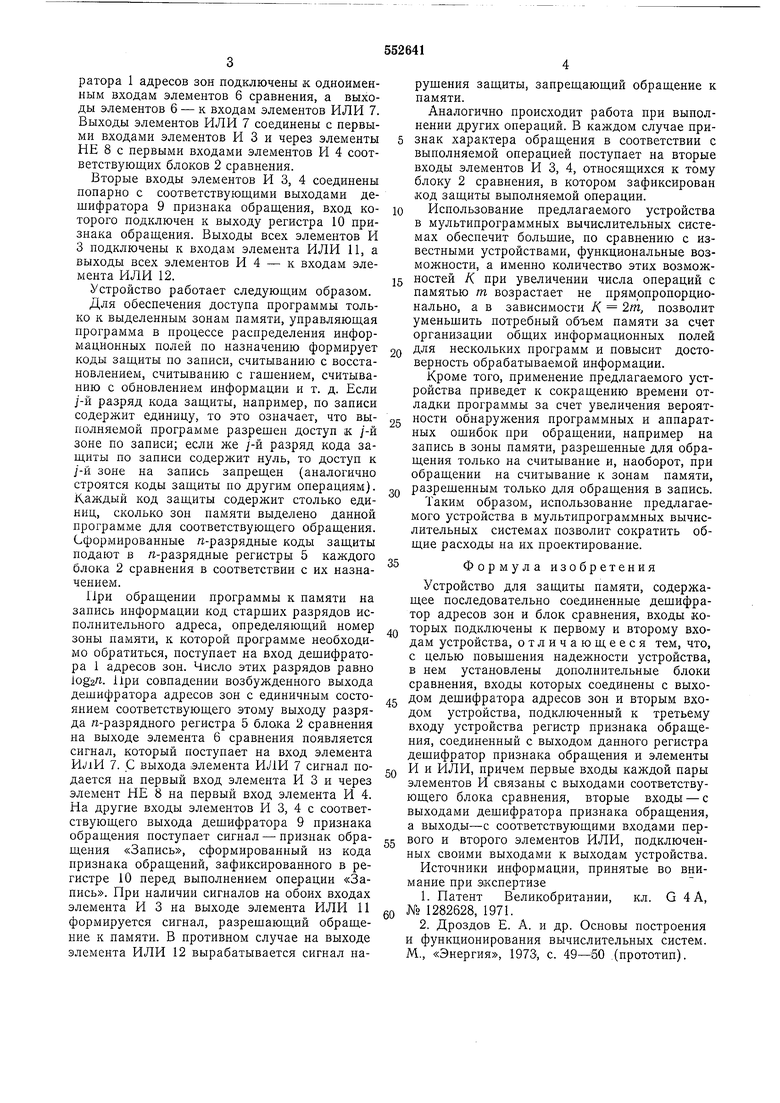

На чертеже представлена функциональная схема устройства.

Предлагаемое устройство содержит дещифратор 1 адресов зон, блоки 2 сравнения, общее число которых соответствует числу операций с памятью (записи, считывания с восстановлением, считывания с гащением, считывания с обновлением и т.д .), соответствующие им пары элементов И 3, 4. Каждый блок 2 сравнения состоит из п-разрядного регистра 5, элемита 6 сравнения, элемента ИЛИ 7 и элемента НЕ 8. Выходы п-разрядных регистров 5 и соответствующие им выходы дещифратора 1 адресов зон подключены к одноименным входам элементов 6 сравнения, а выходы элементов 6 - к входам элементов ИЛИ 7. Выходы элементов ИЛИ 7 соединены с первыми входами элементов И 3 и через элементы НЕ 8 с первыми входами элементов И 4 соответствующих блоков 2 сравнения.

Вторые входы элементов И 3, 4 соединены попарно с соответствующими выходами дешифратора 9 признака обращения, вход которого подключен к выходу регистра 10 признака обращения. Выходы всех элементов И 3 подключены к входам элемента ИЛИ 11, а выходы всех элементов И 4 - к входам элемента ИЛИ 12.

Устройство работает следующим образом.

Для обеспечения доступа программы только к выделенным зонам памяти, управляющая программа в процессе распределения информационных полей по назначению формирует коды защиты по записи, считыванию с восстановлением, считыванию с гашением, считыванию с обновлением информации и т. д. Если У-Й разряд кода защиты, например, по записи содержит единицу, то это означает, что выполняемой программе разрешен доступ к /-и зоне по записи; если же /-Й разряд кода защиты по записи содержит нуль, то доступ к у-й зоне на запись запрещен (аналогично строятся коды защиты по другим операциям). Каждый код защиты содержит столько единиц, сколько зон памяти выделено данной программе для соответствующего обращения. Сформированные п-разрядные коды защиты подают в я-разрядные регистры 5 каждого блока 2 сравнения в соответствии с их назначением.

При обращении программы к памяти на запись информации код старших разрядов исполнительного адреса, определяющий номер зоны памяти, к которой программе необходимо обратиться, поступает на вход дешифратора 1 адресов зон. Число этих разрядов равно iog2«. При совпадепии возбужденного выхода дешифратора адресов зон с единичным состоянием соответствующего этому выходу разряда л-разрядного регистра 5 блока 2 сравнения на выходе элемента 6 сравнения появляется сигнал, который поступает на вход элемента Или 7. С выхода элемента ИЛИ 7 сигнал подается на первый вход элемента И 3 и через элемент НЕ 8 на первый вход элемента И 4. На другие входы элементов И 3, 4 с соответствующего выхода дешифратора 9 признака обращения поступает сигнал - признак обращения «Запись, сформированный из кода признака обращений, зафиксированного в регистре 10 перед выполнением операции «Запись. При наличии сигналов на обоих входах элемента И 3 на выходе элемента ИЛИ 11 формируется сигнал, разрешающий обращение к памяти. В противном случае на выходе элемента ИЛИ 12 вырабатывается сигнал нарушения защиты, запрещающий обращение к памяти.

Аналогично происходит работа при выполнении других операций. В каждом случае признак характера обращения в соответствии с выполняемой операцией поступает на вторые входы элементов И 3, 4, относящихся к тому блоку 2 сравнения, в котором зафиксирован код защиты выполняемой операции.

Использование предлагаемого устройства в мультипрограммных вычислительных системах обеспечит большие, по сравнению с известными устройствами, функциональные возможности, а именно количество этих возможностей К. при увеличении числа операций с памятью т возрастает не прямрпропорционально, а в зависимости К, 2т, позволит уменьшить потребный объем памяти за счет организации общих информационных полей

для нескольких программ и повысит достоверность обрабатываемой информации.

Кроме того, применение предлагаемого устройства приведет к сокращению времени отладки программы за счет увеличения вероятиости обнаружения программных и аппаратных ошибок при обращении, например на запись в зоны памяти, разрешенные для обращения только на считывание и, наоборот, при обращении на считывание к зонам памяти,

разрешенным только для обращения в запись. Таким образом, использование предлагаемого устройства в мультипрограммных вычислительных системах позволит сократить общие расходы иа их проектирование.

Формула изобретения

Устройство для защиты памяти, содержащее последовательно соединенные дешифратор адресов зон и блок сравнения, входы которых подключены к первому и второму входам устройства, отличающееся тем, что, с целью повышения надежности устройства, в нем установлены дополнительные блоки сравнения, входы которых соединены с выходом дешифратора адресов зон и вторым входом устройства, подключенный к третьему входу устройства регистр признака обращения, соединенный с выходом данного регистра дешифратор признака обращения и элементы

И и ИЛИ, причем первые входы каждой пары элементов И связаны с выходами соответствующего блока сравнения, вторые входы - с выходами дешифратора признака обращения, а выходы-с соответствующими входами первого и второго элементов ИЛИ, подключенных своими выходами к выходам устройства. Источники информации, принятые во внимание при экспертизе

1.Патент Великобритании, кл. G 4А, № 1282628, 1971.

2.Дроздов Е. А. и др. Основы построения и функционирования вычислительных систем. М., «Энергия, 1973, с. 49-50 .(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Устройство для контроля программ | 1983 |

|

SU1136172A1 |

| Устройство сопряжения с памятью | 1979 |

|

SU903849A1 |

| Устройство для защиты памяти | 1988 |

|

SU1509910A1 |

| Устройство для связи процессоров | 1986 |

|

SU1481785A1 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

Авторы

Даты

1977-03-30—Публикация

1975-12-29—Подача