1

Изобретение относится к автоматике и вычислительной технике, может быть использовано в качестве распределителя, регистра сдвига счетчика и т. п., ъ измерительной и вычислительной аппаратуре.

Известно пересчетное устройство, содержащее потенциальные логические элементы.

Недостатки известного устройства - ограниченная емкость и низкое быстродействие.

Наиболее близко -к предлагаемому пересчетное устройство, каждый каскад которого содержит два элемента И, элемент ИЛИ и инвертор, причем выходы элементов И соединены со входами элемента ИЛИ, выход которого соединен с инвертором.

Недостатком известного устройства является сравнительно низкое быстродействие, что связано с необходимостью использования трехфазной синхронизации.

Цель изобретения - повышение быстродействия - достигается тем, что в пересчетпое устройство, каждый каскад которого содержит два элемента И, элемент ИЛИ и инвертор, причем выходы элементов И соединены со входами элемента ИЛИ, выход которого соединен с инвертором, в каждый каскад введен третий элемент И, выход которого соединен со входом элемента ИЛИ, a входы соединены с первыми входами первого и второго элементов И, которые соединены соответственно с выходом инвертора предшествующего каскада и с тактовой шиной, причем в один из каскадов введен четвертый элемент И, выход которого соединен со входом элемента ИЛИ этого разряда, входы-с выходами инверторов двух других каскадов, a выход элементов ИЛИ соединен со вторыми входами первого и второго элементов И данного разряда. Ири четном числе каскадов во всех каскадах кроме одного выход элемента ИЛИ предшествующего каскада непосредственно соединен с объединенными входами первого и третьего элементов И последующего каскада, вторые входы третьих элементов И соединены соответственно с парафазными тактовыми шинами.

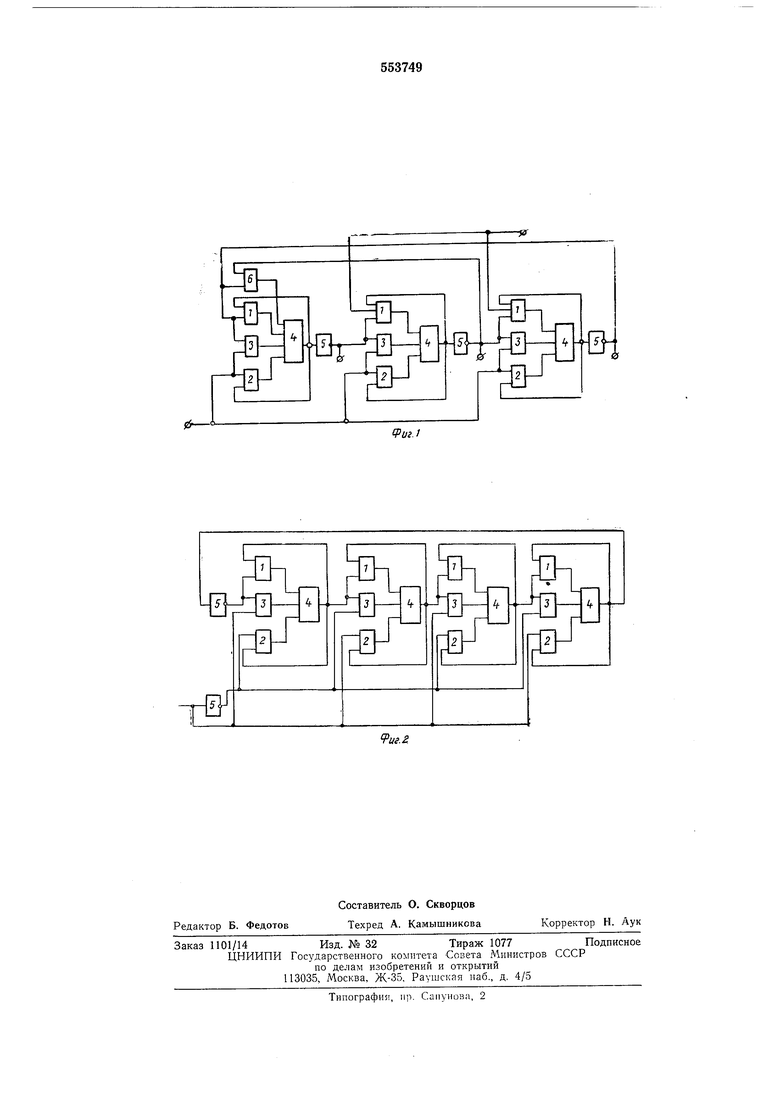

На фиг. 1 показана структурная схема пересчетного устройства при нечетном числе каскадов, на фиг. 2--при четном числе каскадов.

Устройство содержит элементы И 1-3, элементы ИЛИ 4, инверторы 5 и дополнительный элемент И 6, причем выходы элементов И 1-3 каждого каскада соединены со входами элемента ИЛИ того же каскада, выход элемента ИЛИ каждого разряда соединен со вторыми входами элементов И 1 и 2 того же разряда, первые входы элементов И 1 и 3 соединены с выходом инвертора предыдущего разряда, второй вход элемента И 3 и

первый вход элемента И 2 соединены с тактовой шиной. При нечетном числе каскадов в один из каскадов введен дополнительный элемент И 6, выход которого соединен со входом элемента ИЛИ этого каскада, а входы- с выходами инверторов двух других каскадов. При четном числе каскадов во всех каскадах кроме одного выход элемента ИЛИ предшествующего каскада непосредственно соединен с объединенными входами первого и третьего элементов И последующего каскада, а вторые входы вторых и третьих элементов И соединены соответственно с парафазными тактовыми шинами.

Рассмотрим работу устройства, показанного на фиг. 1.

В исходном состоянии элементы И 1 второго и третьего каскадов выключены, и на выходе инвертора первого каскада логический нуль, а на выходах инверторов второго и третьего каскадов - логическая единица. Пусть на вход подается последовательность счетных импульсов. При поступлении первого импульса срабатывает элемент И 3 третьего каскада. В результате этого на выходе элемента ИЛИ 4 этого разряда устанавливается единица, и с помощью элемента И 1 замыкается цепь положительной обратной связи, обеспечивая запоминание состояния «единица элемента ИЛИ 4 этого разряда. На выходе инвертора устанавливается состояние «нуль. Состояние выходов 7 и 8 не изменяется, поскольку входной единичный сигнал подтверждает состояние «единица элемента ИЛИ 4 первого каскада, и изменение состояния второго каскада блокируется ло входам элементов И 1 и 3 с выхода инвертора первого разряда и по входу элемента И 2 с выхода элемента ИЛИ 4 сигналом «нуль. После окончания сигнала «единица на входе выключаются элементы И 2, 3 лервого каскада. Это приводит к установке нуля на выходе элемента ИЛИ 4 данного каскада и к появлению единицы на выходе инвертора 5 первого каскада. Таким образом, к началу второго сигнала на входе изменяются состояния первого и третьего каскадов. Важной особенностью устройства является возможность надежного

запоминания состояния каскада в зависимости от комбинации сигналов с выхода предшествующего каскада и со входа. Элемент И 6 исключает блокировку работы устройства,

поскольку при появлении запрещенного кодового состояния 111, например из-за помех, оно автоматически переводится в 011-исходное состояние устройства. После действия второго и третьего сигналов устройство возвращается в исходное состояние.

Таким образом, при трех каскадах устройство выполняет лересчет на три, т. е. на единицу больше, чем прототип. В случае четного числа каскадов принцип работы устройства

остается прежним. Быстродействие устройства при этом не уменьшается.

Формула изобретения

1. Пересчетное устройство, каждый каскад которого содержит два элемента И, элемент ИЛИ и инвертор, причем выходы элементов И соединены со входами элемента ИЛИ, выход которого соединен с инвертором, отличающееся тем, что, с целью повышения быстродействия, в каждый каскад введен третий элемент И, выход которого соединен со входом элемента ИЛИ, а входы соединены с первыми входами первого и второго элементов И, которые соединены соответственно с выходом инвертора предшествующего каскада и с тактовой шиной, причем в один из каскадов введен четвертый элемент И, выход которого соединен со входом элемента ИЛИ

этого разряда, входы-с выходами инверторов двух других каскадов, а выход элементов ИЛР1 соединен со вторыми входами первого и второго элементов И данного разряда.

2. Пересчетное устройство по л. 1, отличающееся тем, что при четном числе каскадов во всех каскадах кроме одного выход элемента ИЛИ предшествующего каскада непосредственно соединен с объединенными

входами первого и третьего элементов И последующего каскада, вторые входы вторых и третьих элементов И соединены соответственно с парафазиыми тактовыми шинами.

IfUi.l

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Преобразователь N-разрядного параллельного кода в последовательный и обратно | 1979 |

|

SU922724A1 |

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2515225C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1965 |

|

SU170752A1 |

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

Авторы

Даты

1977-04-05—Публикация

1976-03-19—Подача