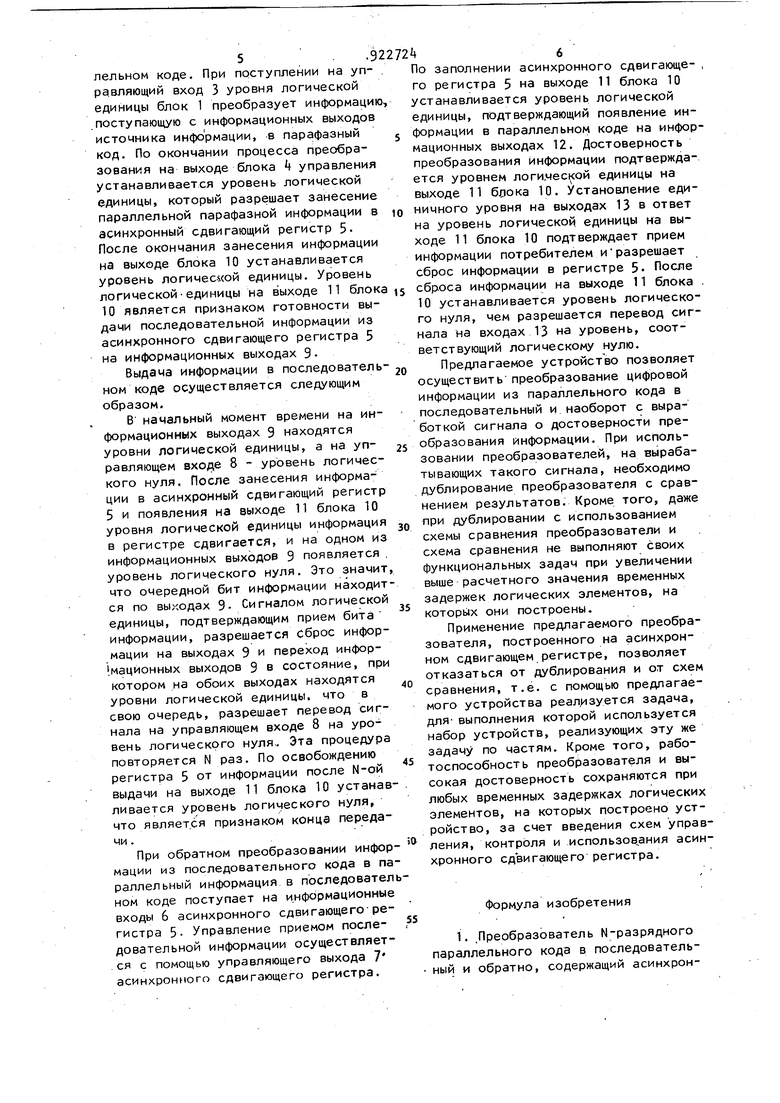

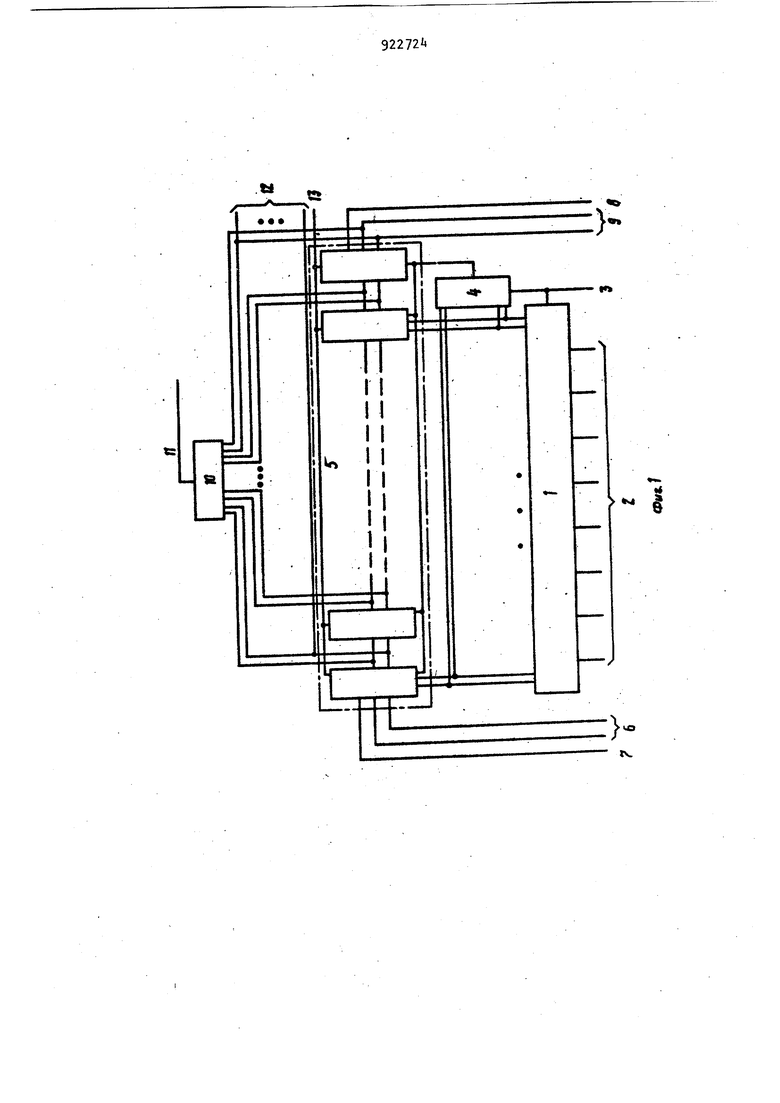

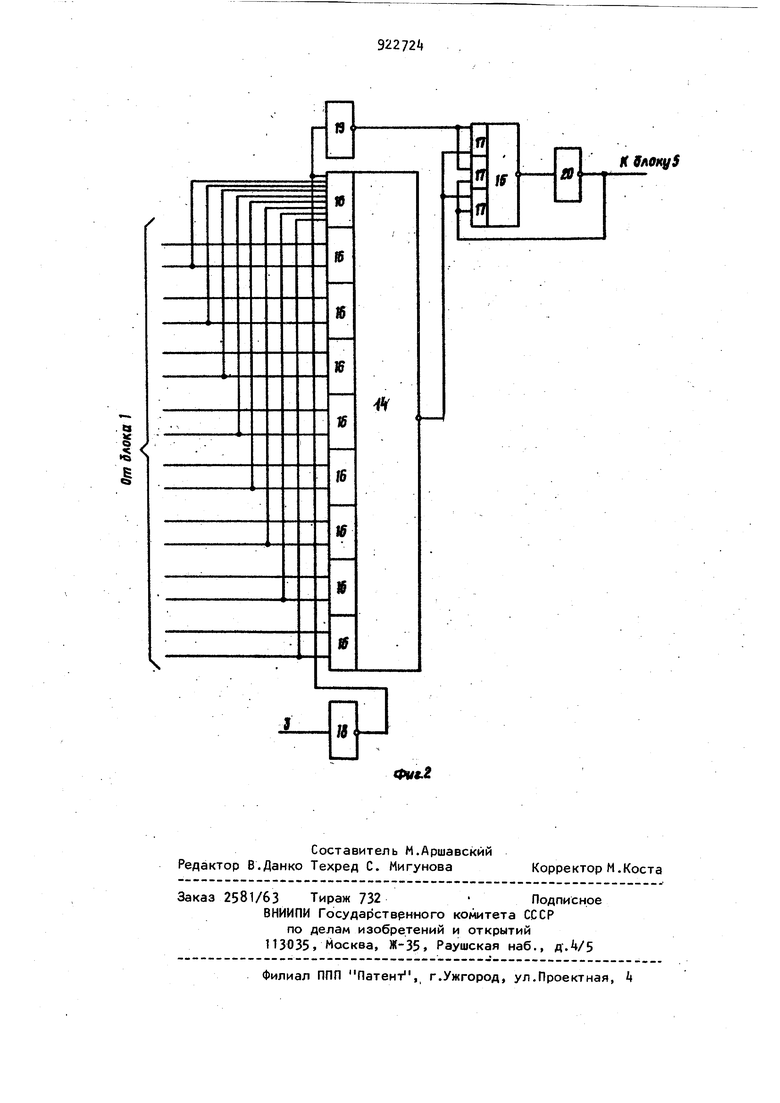

( 5 ) ПРЕОБРАЗОВАТЕЛЬ N-РАЗРЯДНОГО ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано в устройствах обмена, хранения и преобразования информации. Известен пpeoбpaзoвateль параллель ного кода в последовательный и обратно, содержащий сдвигающий регистр , разделенный на тетрады, блоки коррекции, выходы которых подключены к входам сдвигающего регистра, блоки анализа, первые входы которых подключены к выходам сдвигающего регистра, и блок, управления сдвигающим регистром, выход которого подключен к вторым входам блоков анализа 11. Недостаток известного преобразователя состоит в низкой достоверности преобразования, в отсутствии контроля преобразования, а также в низком быстродействии, являющимся следствием использования генератора тактовых импульсов. И ОБРАТНО Наиболее близким к изобретению по технической сущности является преобразователь параллельного кода в последовательный и обратно, содержащий асинхронный сдвигающий регистр с 2N разрядами, где N-миело разрядов преобразуемого кода, парафазные информационные входы и выходы последовательного кода которого являются соответственно информационными входами и выходами последовательного кода преобразователя, а управляющие вход и выход асинхронного сдвигающего регистра являются соответственно управляющими входом и выходом преобразователя, вход сброса которого соединен с входом сброса асинхронного сдвигающего регистра Г2. Недостатком данного преобразователя также является относительно низкое быстродействие и невысокая достоверность, связанная с отсутствием контроля. 3922 Цель изобретения - увеличение быстродействия и повышение достоверности преобразователя. Поставленная цель достигается тем, что в преобразователь N-разрядного параллельного кода в последовательный и обратно, содержащий асинхронный сдвигающий регистр с 2N разрядами, где N - число разрядов преобразуемого кода, парафазные информационные вход и выходы Последовательного кода кото рого являются соответственно информа ционными входами и выходами последовательного кода преобразователя, а управляющие вход и выход асинхронного сдвигающего регистра являются соответственно управляющими входом и выходом преобразователя, вход сброса которого соединен с входом сброса -асинхронного сдвигающего регистра, введены блок элементов И-НЕ, блок управления и блок контроля, вхбды ко торого соединены с парафазными информационными выходами асинхронного сдвигающего регистра, являющимися информационными параллельными выходами преобразователя, парафазные информационные входы четных разрядов асинхронного сдвигающего регистра соединены с парафазными выходами бло ка элементов И-НЕ и с информационными входами блока управления, выход которого соединен с сигнальным входо асинхронного сдвигающегося регистра, выход блока контроля является управляющим выходом готовности преобразователя, управляющий вход запуска преобразователя соединен с управляющими входами блока элементов-И-НЕ и блока управления. Кроме того, блок управления додер жит первый и второй .элементы ИЛИ-НЕ первую группу (N+1)-го .элемента И, выходы которых соединены с входами первого элемента ИЛИ-НЕ, вторую груп пу из трех элементов И, выходы которых соединены с входами второго элемента ИЛИ-НЕ, и три инвертора, входы N элементов И первой группы являются парафазными информационными входами блока управления, информационные вхо ды прямого кода блока управления сое динены соответственно с N входами (N+1 )-го элемента И первой группы, вход первого инвертора является упра ляющим входом блока управления, а вы ход первого инвертора соединен с (М+1)-ым входом (NH-l)-ro элемента И первой группы и входом второго инвер 4 тора, выход которого соединен с первыми входами первого и второго элементов И второй группы, выход второго элемента ИЛИ-НЕ через третий инвертор соединен с вторым входом второго и первым входом третьего элемента И второй группы, вторые входы первого и третьего элементов И второй группы соединены с выходом первого элемента ,ИЛИ-НЕ, выход третьего инвертора является выходом блока управления. На фиг.1 представлена блок-схема управления предлагаемого преобразователя; на фиг.2 - блок-схема блока управления. Преобразователь содержит блок 1 элементов И-НЕ с N информационными входами 2 и управляющим входом-3 блок i управления с управляющим входом, подключенным к управляемому входу блока 1, асинхронный сдвигающий регистр 5 с парафазными информационным входом 6 в последовательном коде, управляющим входом 7 асинхрон ного сдвигающего регистра 1, управляющим входом 8, парафазным информационным выходом 9 в последовательном коде, выходы блока 1 поразрядно подключены к входам блока 4 управления И установочными входами четных разрядов асинхронного сдвигающего регистра 5 сигнальные входы которых подключены к выходу блока k управления, блок 10 контроля, входы которого поразрядно подключены к информационным выходам параллельного кода регистра 5 а выход И блока 10 является выходом готовности преобразователя, информационные выходы асинхронного сдвигающего регистра 5 подключены к информационным параллельным выходам преобразователя, входы сброса асинхронного сдвигающего регистра 5 подключены к входу 13 сброса преобразователя. Блок k управления содержит первый и второй элементы ИЛИ-НЕ 14-15 первую группу 16 из (N+1)-го элемента И, вторую группу 17 из-трех элементов И и три инвертора 18-20. Блок контроля может быть выполнен из 6N/8 элементов И-НЕ и И-ИЛИ-НЕ. Преобразователь работает следующим образом. Блок 1 элементов И-НЕ закрыт уровнем логического нуля на управляющем входе 3 поступающим от управляющего выхода источника информации в параллельном коде. При поступлении на управляющий вход 3 уровня логической единицы блок 1 преобразует информаци .поступающую с информационных выходов источника информации, в парафазный код. По окончании процесса преобразования на выходе блока управления устанавливается уровень логической единицы, который разрешает занесение параллельной парафазной информации в асинхронный сдвигающий регистр 5После окончания занесения информации на выходе блока 10 устанавливается уровень логичес«ой единицы. Уровень логическойединицы на выходе 11 блок 10 является признаком готовности выдачи последовательной информации из асинхронного сдвигающего регистра 5 на информационных выходах 9 Выдача информации в последователь ном коде осуществляется следующим образом, В начальный момент времени на информационных выходах 9 находятся уровни логической единицы, а на управляющем входе 8 - уровень логического нуля. После занесения информации в асинхронный сдвигающий регистр 5 и появления на выходе 11 блока 10 уровня логической единицы информация в регистре сдвигается, и на одном из информационных выходов 9 появляется , уровень логического нуля. Это значит что очередной бит информации находит ся по выходах 9- Сигналом логической единицы, подтверждающим прием бита информации, разрешается Сброс информации на выходах 9 и переход информационных выходов 9 в состояние, при котором на обоих выходах находятся уровни логической единицы, что в свою очередь, разрешает перевод сигнала на управляющем входе 8 на уровень логического нуля. Эта процедура повторяется N раз. По освобождению регистра 5 от информации после N-ой выдачи на выходе 11 блока 10 устанавливается уровень логического нуля, что является признаком конца передачи. При обратном преобразовании инфор мации из последовательного кода в параллельный информация в последовател ном коде поступает на и.нформационные входы 6 асинхронного сдвигающего-регистра 5- Управление приемом последовательной информации осуществляется с помощью управляющего выхода 7 асинхронного сдвигающего регистра.

По заполнении асинхронного сдвигающе- , го регистра 5 на выходе 11 блока 10 устанавливается уровень логической единицы, подтверждающий появление информации в параллельном коде на информационных выходах 12. Достоверность преобразования информации подтверждается уровнем логияеской единицы на выходе 11 блока 10. Установление единичного уровня на выходах 13 в ответ на уровень логической, единицы на выходе 11 блока 10 подтверждает прием информации потребителем иразрешает сброс информации в регистре 5- После сброса информации на выходе 11 блока 10 устанавливается уровень логического нуля, чем разрешается перевод сигнала на входах 13 на уровень, соответствующий логическому нулю. Предлагаемое устройство позволяет осуществитьпреобразование цифровой информации из параллельного кода в последовательный и наоборот с выработкой сигнала о достоверности преобразования информации. При использовании преобразователей, на вырабатывающих такого сигнала, необходимо дублирование преобразователя с сравнением результатов. Кроме того, даже при дублировании с использованием схемы сравнения преобразователи и схема сравнения не выполняют своих функциональных задач при увеличении выше расчетного значения временных задержек логических элементов, на KOToptJX они построены. Применение предлагаемого преобразователя, построенного на асинхронном сдвигающем регистре, позволяет отказаться от дублирования и от схем сравнения, т.е. с помощью предлагаемого устройства реал зуется задача, для- выполнения которой используется набор устройств, реализующих эту же задачу по частям. Кроме того, работоспособность преобразователя и высокая достоверность сохраняются при любых временных задержках логических элементов, на которых построено устройство, за счет введения схем управления, контроля и использов,ания асинхронного сдвигающего регистра. Формула изобретения 1. ,Преобразователь N-разрядного параллельного кода в последовательный и обратно, содержащий асинхронный сдвигающий регистр с 2N разрядами, где N - число разрядов преобразуемого кода, парафазные информационные входы и выходы последовательного кода котоохр являются соответственно информа- s ционными входами и выходами последовательного кода преобразователя, а управляющие вход и выход асинхронного сдвигающего регистра являются соответственно управляющими входом и выходом О преобразователя, вход сброса которого соединен с входом сброса асинхронного сдвигающего регистра, отличающийся тем, что, с целью повышения быстродействия и увеличения его 15 достоверности, в него введены блок элементов И-НЕ, блок управления и блок контроля, входы которого соединены с парафазными информационными выходами асинхронного сдвигающего20

регистра, являющимися информационными параллельными выходами преобразователя, входы четных разрядов асинхронного сдвигающего регистра соединены с парафазными выходами блока 25 элементов И-НЕ и с информационными входами блока управления, выход которого соединен с сигнальным входом асинхронного сдвигающего регистра, выход блока контроля является управ- зо ляющим выходом готовности преобразовateля, вход запуска преобразователя соединен с управляющими входами блока элементов И-НЕ и блока управления.

2, Преобразователь по п.1,о т л чающийся тем, что в нем блок управления содержит первый и второй

элементы ИЛИ-НЕ, первую группу из (N+1)-ro элемента И, выходы которых соединены с входами первого элемента ИЛИ-НЕ, вторую группу из трех элементов И, выходы которых соединены с входами второго элемента ИЛИ-НЕ, и три инвертора, входы N элементов И первой группы являются парафазными информационными входами блока управления, информационные входы прямого кода блока управления соединены соответственно с входами (N+l)-ro элемента И первой группы, вход первого инвертора является управляющим входом блока управления, а выход первого инвертора соединен с (М+1)-ым входом (N+1)-ro элемента И первой группы и входом второго инвертора, выход которого соединен с первыми входами первого и второго элементов И второй группы, выход второго элемента ИЛИ-НЕ третий инвертор соединен с втсг рым входом второго и первым входом третьего элемента И второй группы, вторые входы первого и третьего элементов И второй группы соединены с выходом первого элемента ИЛИ-НЕ, выход третьего инвертора является выходом блока управления.

Источники информации, принятые .во внимание при экспертизе

1.Авторское свидетельство СССР № 62if226, кл. G Об F 5/02, 19752.Апериодические автоматы. .Под ред..В.И.Варшавского. М., Наука, 1975, с.309 (прототип).

VO

tv

19

К 9АОку5

to

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Преобразователь кодов | 1988 |

|

SU1552380A1 |

| Преобразователь кода во временной интервал | 1990 |

|

SU1753512A1 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| ПАРАФАЗНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2030107C1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 1997 |

|

RU2121754C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

16

t

1

Авторы

Даты

1982-04-23—Публикация

1979-09-10—Подача