I

Изобретение относится к аналоговой вычислительной технике.

. Известно множительно-делительное устройство, содержащее интеграторы, компаратор и заполшнающий блок (1J.

Недостатком его является невысокая точность измерения.

Наиболее близким к предлагаемому является устройство, содержащее первый интегратор, информащсонный вход которого является входом делителя устройства, а управляющий вход соединен со входом триггера, компаратор, первый вход которого соединен с выходом первого интегратора, а второй вход является входом первого сомножителя устройства, второй интегратор, выход которого соединен со входом запоминающего блока и одновибратор 2.

Недостатком этого устройства является невысокая точность измерения, обусловленная тем, что между двумя тактами деления присутствует временной интервал, необходимый для сбрасьтания на нуль напряжения первого интегратора. Так как зтот временной интервал входит в результат умножения-деления, то выходкое напряжение на выходе устройства получается больше истинного на величину, пропорщюнальную этому временному интервалу. Точнее, напряжение, запоминающееся в запоминающем блоке, равно U ,( +т)

где Т - временной интервал, необходимый для сбрасывания на нуль напряжения первого интегратора, т.е. результат вычисления имеет ошибку Ди KjZ-T. Это особенно сказывается при увеличении быстродействия устройства.

Цель изобретения - повыщение точности при увеличении быстродействия.

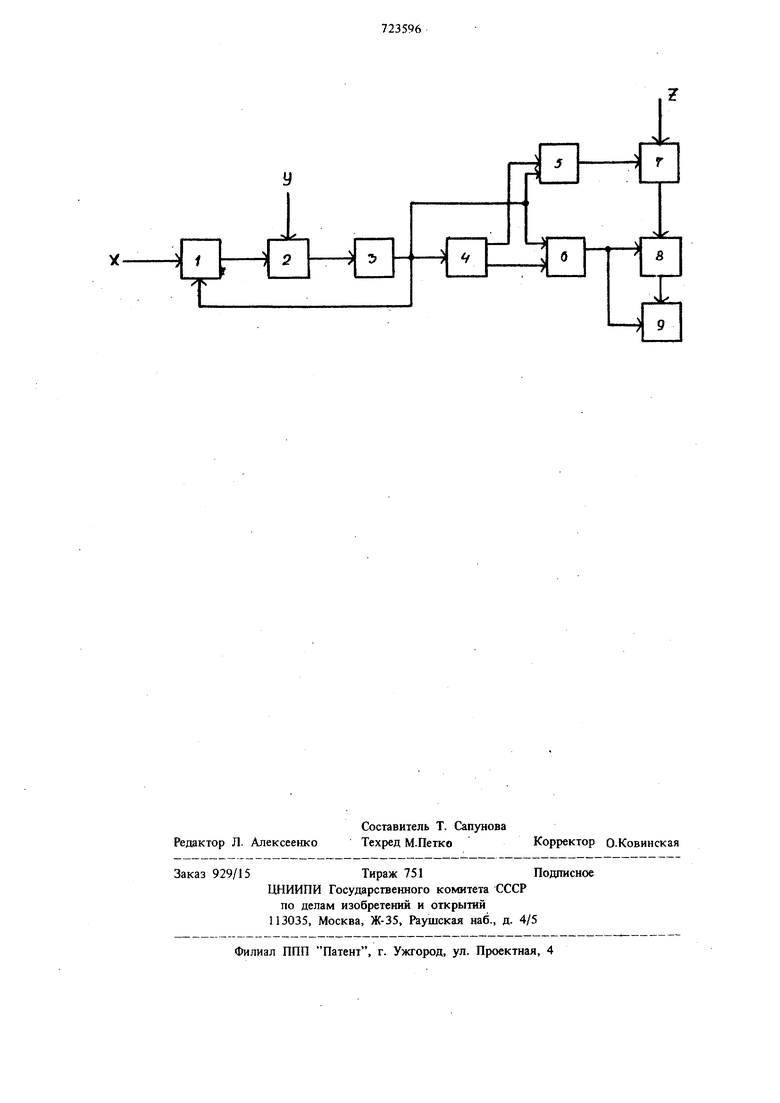

Эта цель достигается тем, что в устройство содержащее первый интегратор, компаратер, второй интегратор, триггер, одновибратор и запоминающий блок, причем информационный вход первого интегратора является входом делителя устройства, а управляющий вход соединен со входом триггера, выход первого интегратора подключен к одному из входов компаратора, второй вход которого является входом первого помножителя, выход второго интегратора подключен ко входу запоминающего блока, дополнитель.ю введены два элемеи та И и ключ, информадаонный вход которого является входом второго сомножителя, выход соединен со входом второго интегратора, а .управляющий вход подключен к выходу первого элемента И. Выход второго элемента И Подключен к управляющим входам второго интегратора и запоминающего блока. Выход компаратора соединен со входом одновибратора, выход которого подключен к первым входам обоих элементов И, вторые входы которых подключены к выходам триггера. На чертеже. приведена функциональная схема устройства. Устройство содержит первый интегратор 1, компаратор 2, одновибратор 3, триггер 4, первый элемент И 5, второй элемент И 6, ключ 7 второй интегратор 8, запоминающий блок 9. Устройство работает следующим образом. Пусть в исходном состоянии на прямом вы ходе триггера 4 нулевой потенциал. Первый ин тегратор 1 пропорционально входному напряже нию X вырабатывает линейно-изменяющееся напряжение, поступающее на вход компаратора 2 на другой вход которого подается напряжение При достижении линейно-изменяющимся напряжением уровня напряжения У компаратор 2 срабатывает и запускает одновибратор 3, импульс с выхода которого сбрасывает на нуль первый интегратор 1. При этом Y К,-Х-Т, где KI - коэффициент преобразования первого интегратора 1. Т - период равенства напряжения У и линейно-изменяющегося напряжения первого интегратора 1. Импульсы с выхода одновибратора 3 задним своим фронтом перебрасывают триггер 4, кото рый управляет элементами И 5 и 6. Импульсы с выхода одновибратора 3 через элемент И 5 блокируют ключ 7, а через элемент И 6 вызывают срабатывание запоминающегося блока 9, запоминающего мгновенное значение напряжения навыходе второго интегратора 8,и .сбрасывание на нуль второго интегратора 8. Так как импульсы с выхода элемента И 6 возникают на каждый второй импульс с выход одновибратора 3, а промежуточные импульсы блокируют ключ 7, то величина напряжения на выходе второго интегратора 8 , .22Т, где Kj - коэффициент преобразования второго интегратора 8. Напряжение, запоминающееся в запоминающ блоке 9 2K7-ZiY К,-Х В предлагаемом устройстве, для компенсации ощибки, обусловленной наличием временного интервала, необходимого Ш1я сбрасывания на нуль напряжения первого интегратора, введен ключ 7 и устройство коммутации, построенное на базе элементов И 5 и 6, управляемое триггером 4. Ключ 7 служит для блокировки информационного входа второго интегратора на время, необходимое для сбрасьшания на нуль первого интегратора в промежутке между двумя тактами деления, т.е. во время сбрасывания первого интегратора на нуль напряжение на выходе второго интегратора остается постоянным и равно К,-Х Применение предлагаемого устройства позволяет повысить точность обработки до 0,1% и выще при значительном увеличении быстродействия. Формула изобретения Множительно-делительное устройство, содержащее первый интегратор, компаратор, триггер, второй интегратор, одновибратор и запоминающий блок, причем информационный вход первого интегратора является входом делителя устройства, а управляющий вход соединен со входом триггера, выход первого интегратора подключен к одному из входов компаратора, второй вход которого является входом первого сомножителя, выход второго интегратора подключен ко входу запоминающего блока, отличающееся тем, что, с целью повышения точности при увеличении быстродействия, оно дополнительно содержит два элемента И и ключ, информационный вход которого является входом второго сомножителя, выход соединен со входом второго интегратора, а управляющий вход подключен к выходу первого элемента И, выход второго элемента И подключен к управляющим входам второго интегратора и запоминающего блока, выход компаратора соединен со входом одновибратора, выход которого подключен к пбрвым входам обоих элементов И, вторые входы которых подключены к выходам триггера. Источники информации, принятые во внимание при экспертизе 1.Патент США N 3564230, кл. 235-197, 1971. 2.Авторское свидетельство СССР № 568056, кл. G 06 G 7/161, 1977 (прототип).

и:

I

8

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1975 |

|

SU568056A1 |

| Множительно-делительное устройство | 1978 |

|

SU1095195A1 |

| Множительно-делительное устройство | 1974 |

|

SU554540A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1124346A1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Измеритель нелинейности амплитудной характеристики радиоэлементов | 1986 |

|

SU1370615A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1993 |

|

RU2082996C1 |

| Время-импульсное множительное устройство | 1982 |

|

SU1048489A1 |

| Коррелятор | 1975 |

|

SU526917A1 |

| Множительно-делительное устройство | 1978 |

|

SU1005081A1 |

Авторы

Даты

1980-03-25—Публикация

1978-01-23—Подача