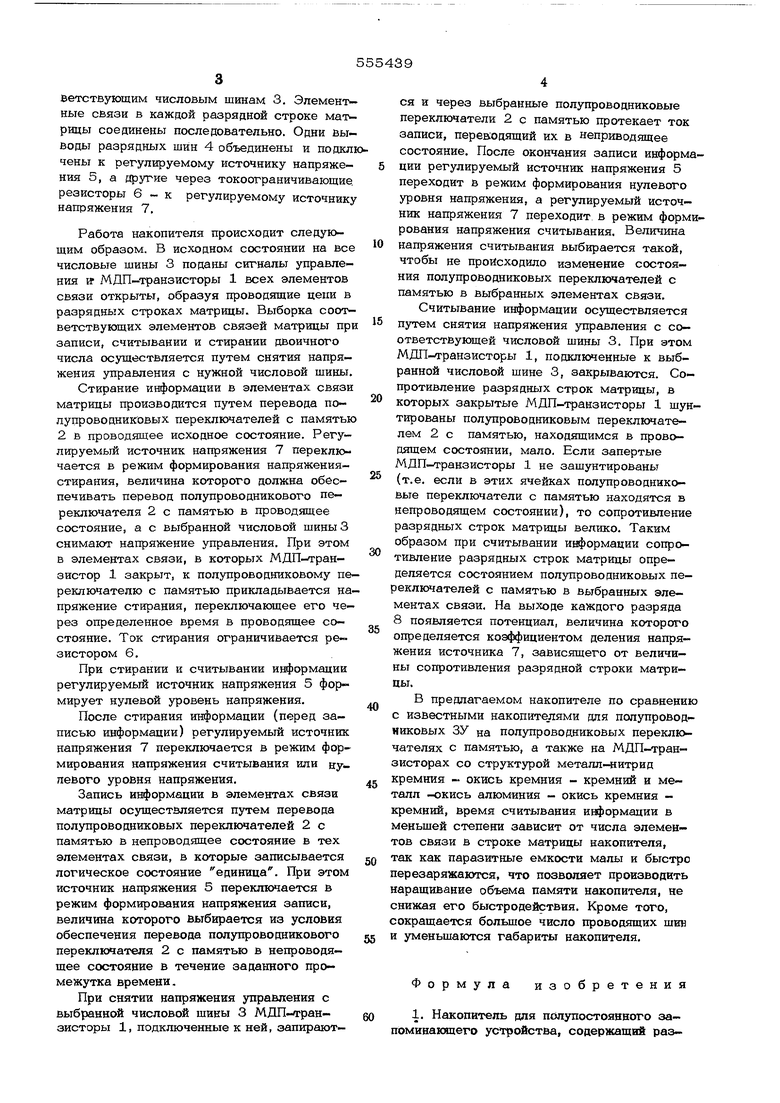

ветствующим числовым шинам 3. Элементные связи в каждой разрядной строке матрицы соединены последовательно. Одни выводы разрядных шин 4 объединены и подкл чены к регулируемому источнику напряжения 5, а другие через токоограничивающие резисторы 6 - к регулируемому источнику напряжения 7, Работа накопителя происходит следующим образом. В исходном состоянии на все числовые шины 3 поданы сигналы управления w МДП-транзисторы 1 всех элементов связи открыты, образуя проводяпдие цепи в разрядных строках матрицы. Выборка соответствующих элементов связей матрицы пр записи, считывании и стирании двоичного числа осуществляется путем снятия напряжения управления с нужной числовой шины. Стирание информации в элементах связи матрицы производится путем перевода полупроводниковых переключателей с памятью 2 в проводящее исходное состояние. Регулируемый источник напряжения 7 перекшочается в режим формирования напряжениястирания, величина которого должна обеспечивать перевод полупроводникового переключателя 2 с памятью в проводящее состояние, а с выбранной числовой шины 3 снимают напряжение управления. При этом в элементах связи, в которых МДП-транзистор 1 закрыт, к полупроводниковому пе реключателю с памятью прикладывается на пряжение стирания, переключающее его через определенное время в проводящее состояние. Ток стирания ограничивается резистором 6. При стирании и считывании информации регулируемый источник напряжения 5 формирует нулевой уровень напряжения. После стирания информации (перед записью информации) регулируемый источник напряжения 7 переключается в режим формирования напряжения считывания или иу левого уровня напряжения. Запись информации в элементах связи матрицы осуществляется путем перевода полупроводниковых переключателей 2 с памятью в непроводящее состояние в тех элементах связи, в которые записывается логическое состояние единица. При этом источник напряжения 5 переключается в режим формирования напряжения записи, величина которого выбирается из условия обеспечения перевода полупроводникового переключателя 2 с памятью в непроводящее состояние в течение заданного промежутка времени. При снятии напряжения управления с выбранной числовой шины 3 МДП-/гранзисторы 1, подключенные к ней, запирают- ся и через выбранные полупроводниковые переключатели 2 с памятью протекает ток записи, перев;одящий их в неприводящее состояние. После окончания записи информации регулируемый источник напряжения 5 переходит в режим формирования нулевого уровня напряжения, а регулируемый источник напряжения 7 переходит в режим формирования напряжения считывания. Величина напряжения считывания выбирается такой, чтобы не происходило изменение состояния полупроводниковых переключателей с памятью в выбранных элементах связи. Считывание информации осуществляется путем снятия напряжения управления с соответствующей числовой шины 3. При этом МДП- ранзисторы 1, подключенные к выбранной числовой шине 3, закрываются. Сопротивление разрядных строк матрицы, в которых закрытые МДП-транзисторы 1 шунтированы полупроводниковым переключателем 2 с памятью, наход5пцимся в проводящем состоянии, мало. Если запертые МДП-транзисторы 1 не зашунтированы (т.е. если в этих ячейках полупроводниковые переключатели с памятью находятся в непроводящем состоянии), то сопротивление разрядных строк матрицы велико. Таким образом при считывании информации сопротивление разрядных строк матрицы определяется состоянием полупроводниковых переключателей с памятью в выбранных элементах связи. На выходе каждого разряда 8 появляется потенциал, величина которого определяется коэффициентом деления напряжения источника 7, зависящего от величины сопротивления разрядной строки матрицы. В предлагаемом накопителе по сравнению с известными накопителями для полупроводниковых ЗУ на полупроводниковых перекл1Очателях с памятью, а также на МДП-т-ран- зисторах со структурой металл-нитрид кремния - окись кремния - кремний и металл -окись алюминия - окись кремния - кремний, время считывания информации в меньщей степени зависит от числа элементов связи в строке матрицы накопителя, так как паразитные емкости малы и быстро перезаряжаются, что позволяет производить наращивание объема памяти накопителя, не снижая его быстродействия. Кроме того, сокращается большое число проводящих шив и уменьшаются габариты накопителя. Формула изобретения 1. Накопитель для полупостоявного запоминающего устройства, содержащий разрядные шины, каждая из которых одним своим концом подключена через токоотраничивающий резистор к первому регулируемому источнику напряжения, и матрицу элементов свЭзи, подключенных к соответствующей числовой шине, отличающийся тем, что, с целью повышения надежности работы накопителя, он содержит второй регулируемый источник напряжения, подключенный к другим концам всех разрядных шин, а элементы связи в строках соединены последовательно.

2. Накопитель поп.1, отличающий с я тем, что элемент связи выпол6

нен из соединенных параллельно МДП-транзистора и полупроводникового переключателя с памятью.

Источники информации, принятые во внимание при экспертизе:

1.Крайзмер Л. П. Устройство хранения дискретной информации Энергия, Л,, 1969 г., стр. 248-249.

2.Заявка № 187О228/18-24 М.Кл. Q 11 С 17/00,УДК 681.327.6,02. 01. 73 г. (принято положительное решение).

3.Заявка № 1915689/18-24 ,М.Кп G 11 С 17/00, 681.327.6, 23. 04. 73 г. (принято положительное решение).

| название | год | авторы | номер документа |

|---|---|---|---|

| Матрица для накопителя полупостоянного запоминающего устройства | 1976 |

|

SU595793A1 |

| Формирователь записи-считывания для запоминающих устройств | 1982 |

|

SU1035639A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| Полупостоянное запоминающее устройство | 1975 |

|

SU611251A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО И СПОСОБ УПРАВЛЕНИЯ ИМ | 1979 |

|

RU1110315C |

| Матричный накопитель для постоянного запоминающего устройства | 1977 |

|

SU734807A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1983 |

|

SU1105055A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1982 |

|

SU1108915A1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| Матричный накопитель | 1980 |

|

SU974412A1 |

Авторы

Даты

1977-04-25—Публикация

1973-07-13—Подача