Изобретение относится к устройствам вычислительной техники. Оно может быть использовано в электрически перепрограммируемых постоянных запоминающих устройствах на n-канальных лавинно-инжекци- онных МДП-транзисторах с плавающими, управляющими, стирающими затворами, сохраняющими информацию при отключенных источниках питания, нашедших широкое применение в блоках памяти вычислительных машин, в устройствах автоматики.

Известна конструкция матричного накопителя для электрически перепрограммируемого постоянного запоминающего устройства, сохраняющего информацию при отключенных источниках питания.

Матричный накопитель содержит полупроводниковую подложку первого типа проводимости, на поверхности которой расположен первый диэлектрический слой с отверстиями. В этих отверстиях расположены диэлектрические слои меньшей толщины. На поверхности первого и вторых диэлектрических слоев расположены поликремниевые электроды.

На поверхности поликремниевых электродов, первого и вторых диэлектрических слоев расположены третьи диэлектрические слои. На поверхности этих диэлектрических слоев размещены адресные поликремниевые шины над поликремниевыми электродами.

На поверхности первого диэлектрического слоя, торцах поликремниевых электродов, третьих диэлектрических слоев, адресных поликремниевых шин расположен четвертый диэлектрический слой. На его поверхности между парами адресных поликремниевых шин над торцами поликремниевых электродов размещены поликремниевые шины стирания.

В приповерхностном слое полупроводниковой подложки под вторыми диэлектрическими слоями размещены диффузионные слои первого типа проводимости, первые и вторые разрядные диффузионные шины второго типа проводимости.

Основными недостатками матричного накопителя являются низкая надежность его работы из-за необходимости контрольного стирания информации из каждой ячейки памяти и невозможность побайтового стирания информации.

Наиболее близким техническим решением является матричный накопитель для электрически перепрограммируемого постоянного запоминающего устройства, сохраняющего информацию при отключенных источниках питания. В матричном накопителе использованы поликремниевые электроды, адресные шины и стирающие шины, диффузионные и металлические разрядные шины. Запоминающий элемент состоит из МОП-транзистора с переменным пороговым напряжением и МДП-транзистора (ключа) с постоянным пороговым напряжением. В конструкции матричного накопителя на две ячейки памяти используется один ключевой МДП-транзистор.

Матричный накопитель содержит полупроводниковую подложку первого типа проводимости, на поверхности которой расположен первый диэлектрический слой с отверстиями. В этих отверстиях расположены вторые диэлектрические слои меньшей толщины. На поверхности первого и вторых диэлектрических слоев расположены поликремниевые электроды. На поверхности поликремниевых электродов, первого и вторых диэлектрических слоев над поликремниевыми электродами расположены поликремниевые адресные шины. На поверхности первого диэлектрического слоя, торцах поликремниевых электродов, третьих диэлектрических слоев, адресных поликремниевых шин расположен четвертый диэлектрический слой.

На его поверхности между парами адресных поликремниевых шин над торцами поликремниевых электродов размещены поликремниевые шины стирания. На поверхности поликремниевых шин стирания и четвертого диэлектрического слоя расположен пятый диэлектрический слой.

В приповерхностном слое полупроводниковой подложки под первыми и вторыми диэлектрическими слоями размещены диффузионные слои первого типа проводимости и первые группы разрядных диффузионных шин второго типа проводимости. Первые группы разрядных диффузионных шин расположены с частичным перекрытием краев поликремниевых электродов, краев первого диэлектрического слоя. Первые группы разрядных диффузионных шин размещены перпендикулярно адресным поликремниевым шинам.

В приповерхностном слое полупроводниковой подложки под вторым диэлектрическим слоем расположены диффузионные слои второго типа проводимости с частичным перекрытием краев первого диэлектрического слоя.

Вторые группы разрядных шин выполнены металлическими и размещены на поверхности пятого диэлектрического слоя и на поверхности вторых диффузионных слоев в отверстиях во втором, четвертом, пятом диэлектрических слоях между каждыми четырьмя поликремниевыми электродами. Вторые группы разрядных металлических шин размещены перпендикулярно адресным поликремниевым шинам.

Адресные поликремниевые шины, расположенные между парами поликремниевых электродов, размещены над вторыми и третьими диэлектрическими слоями с частичным перекрытием краев диффузионных слоев с одной из сторон.

В местах пересечения адресных поликремниевых шин, первых и вторых групп разрядных шин образована ячейка памяти матричного накопителя в виде n-канальных лавинно-инжекционных МДП-транзисторов с плавающими, управляющими, стирающими поликремниевыми затворами с изменяющимися пороговыми напряжениями в процессе программирования или стирания информации и ключевых n-канальных МДП-транзисторов с постоянными положительными пороговыми напряжениями.

Первые группы разрядных диффузионных шин являются стоками лавинно-инжекционных МДП-транзисторов, поли- кремниевые электроды - их плавающими затворами, адресные поликремниевые шины - их управляющими затворами, стирающие поликремниевые шины - их стирающими затворами. Диффузионные слои являются истоками ключевых МДП-транзисторов, адресные поликремниевые шины - их затворами.

Недостатком матричного накопителя является низкое быстродействие.

Целью изобретения является увеличение быстродействия матричного накопителя.

Поставленная цель достигается тем, что матричный накопитель для постоянного запоминающего устройства, содержащий полупроводниковую подложку первого типа проводимости, на поверхности которой расположен первый диэлектрический слой с отверстиями, в которых размещен второй диэлектрический слой меньшей толщины, на поверхности первого и второго диэлектрических слоев размещены поликремниевые электроды, на поверхности которых и поверхностях первого и второго диэлектрических слоев расположен третий диэлектрический слой, на поверхности которого над поликремниевыми электродами размещены адресные поликремниевые шины, на поверхности которых и на торцах поликремниевых электродов расположен четвертый диэлектрический слой, на поверхности которого над одними торцами поликремниевых электродов размещены стирающие поликремниевые шины, на поверхности которых и поверхности четвертого диэлектрического слоя расположен пятый диэлектрический слой, в приповерхностном слое полупроводниковой подложки размещены диффузионные слои первого типа проводимости, первую группу разрядных диффузионных шин второго типа проводимости, расположенных под вторым диэлектрическим слоем с частичным перекрытием краев поликремниевых электродов и краев первого диэлектрического слоя, в приповерхностном слое полупроводниковой подложки под вторым диэлектрическим слоем расположены диффузионные слои второго типа проводимости, на поверхности пятого диэлектрического слоя перпендикулярно адресным поликремниевым шинам распо- ложена вторая группа разрядных металлических шин, содержит ключевые поликремниевые шины, расположенные на поверхности второго диэлектрического слоя параллельно разрядным диффузионным шинам с частичным перекрытием их, причем через N поликремниевых электродов (где N = 2n, n = 1, 2, 3. ..) ключевые поликремниевые шины расположены над первым и вторым диэлектрическими слоями, и третью группу разрядных диффузионных шин второго типа проводимости, расположенных в приповерхностном слое полупроводниковой подложки между ключевыми поликремниевыми шинами с частичным их перекрытием, кроме того, в матричном накопителе четвертый диэлектрический слой на поверхности поликремниевых адресных шин имеет толщину 1500-3000  , на торцах поликремниевых электродов 500-700

, на торцах поликремниевых электродов 500-700  .

.

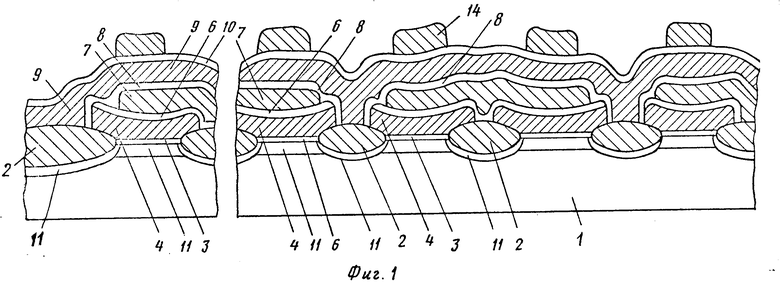

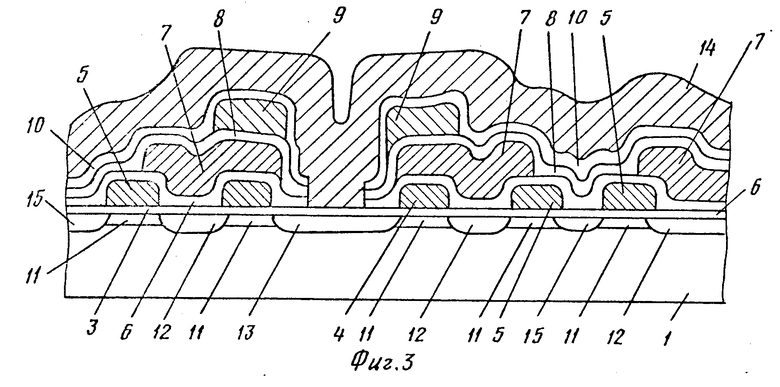

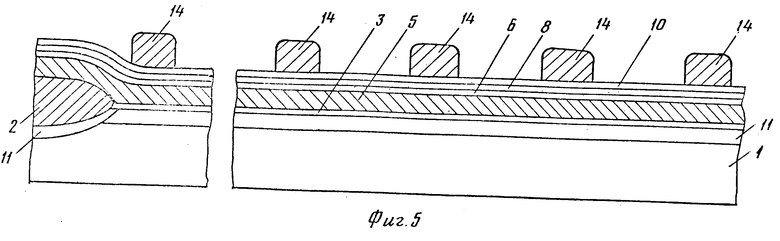

На фиг.1-5 изображена структура матричного накопителя; на фиг.6 показана организация одного байта информации матричного накопителя, состоящего из N ячеек (N = 2n, где n = 1, 2, 3...) памяти. В качестве примера на фиг.6 принято N = 8.

Матричный накопитель (см. фиг.1) содержит полупроводниковую подложку 1 первого типа проводимости, на поверхности которой расположен первый диэлектрический слой 2 с отверстиями. В этих отверстиях расположены вторые диэлектрические слои 3 меньшей толщины. На поверхности первого и вторых диэлектрических слоев расположены поликремниевые электроды 4. На поверхности второго диэлектрического слоя расположены ключевые поликремниевые шины 5 (см. фиг.5). Через N поликремниевых электродов поликремниевые ключевые шины расположены над поверхностью первого диэлектрического слоя. На поверхности поликремниевых электродов и на их первых торцах, ключевых поликремниевых шин, первого и вторых диэлектрических слоев расположены третьи диэлектрические слои 6. На поверхности третьих диэлектрических слоев над парами поликремниевых электродов и первыми их торцами, части ключевых поликремниевых шин расположены адресные поликремниевые шины 7 (см. фиг.1 и 2).

На вторых торцах поликремниевых электродов, поверхностях адресных поликремниевыхн шин, третьего диэлектрического слоя расположен четвертый диэлектрический слой 8 (см. фиг.1 и 2).

На его поверхности над поликремниевыми электродами расположены поликремниевые шины стирания 9 параллельно ключевым поликремниевым шинам (см. фиг. 1 и 3). На поверхности шин стирания и четвертого диэлектрического слоя размещен пятый диэлектрический слой 10 (см. фиг.1, 2, 3 и 4).

В приповерхностном слое полупроводниковой подложки под первым и вторым электрическими слоями размещены диффузионные слои 11 первого типа проводимости и первая группа разрядных диффузионных шин 12 второго типа проводимости. Первая группа разрядных диффузионных шин расположена с частичным перекрытием краев поликремниевых электродов и ключевых шин (фиг.2, 3, 4 и 5). Первая группа разрядных диффузионных шин размещена параллельно ключевым поликремниевым шинам.

В приповерхностном слое полупроводниковой подложки под вторыми диэлектрическими слоями расположены диффузионные слои 13 второго типа проводимости с частичным перекрытием краев поликремниевых электродов (см. фиг.3).

Вторая группа разрядных шин 14 выполнена металлическими и размещена на поверхности пятого диэлектрического слоя и на поверхности диффузионных слоев в отверстиях во втором, четвертом, пятом диэлектрических слоях перпендикулярно ключевым и стирающим поликремниевым шинам (см. фиг.3).

В приповерхностном слое полупроводниковой подложки между парами ключевых поликремниевых шин расположена третья группа разрядных диффузионных шин 15 второго типа проводимости с частичным их перекрытием (см. фиг.3 и 4).

Организация матричного накопителя обеспечивает потактовую запись и стирание электрической информации. Это достигается тем, что n лавинно-инжекционных транзисторов (разрядов) в столбце матричного накопителя имеют независимую вторую группу разрядных металлических шин, общую первую разрядную диффузионную шину, адресную поликремниевую шину, поликремниевую шину стирания.

Ключевой МПД-транзистор является общим для ячеек памяти, третья диффузионная область (исток) заземлена.

Сущность работы матричного накопителя заключается в следующем. Для стирания информации из n разрядов (в данном примере 8) на стирающую поликремниевую шину 9 подают высокое положительное напряжение, адресные, разрядные шины 14 и 7 заземляют. Под действием этого напряжения между торцами поликремниевых электродов 4 и стирающими поликремниевыми шинами 9 возникает высокая напряженность электрического поля, электроны инжектируются с торцов поликремниевых электродов, проходят сквозь четвертый диэлектрический слой, удаляются через стирающие поликремниевые шины. Это приводит к тому, что пороговые напряжения N ячеек памяти имеют высокие отрицательные пороговые напряжения, соответствующие единичному (проводящему) состоянию в режиме считывания информации. В режиме записи электрической информации проводится изменение состояний из единичного в нулевое только в заданные ячейки памяти.

Для программирования нулевых (непроводящих) состояний в заданные ячейки памяти на адресную поликремниевую шину 7 и вторую группу разрядных металлических шин 14 подают высокое положительное напряжение. В случае необходимости сохранения проводящего (единичного) состояния в одних из N ячеек памяти на вторую группу разрядных металлических шин, принадлежащих этим ячейкам памяти, подают нулевое напряжение. Это приводит к захвату поликремниевыми электродами инжектированных "горячих" электронов из канала, к переводу запоминающих элементов в нулевые состояния. Ячейки памяти, у которых на вторых группах разрядных металлических шин были показаны нулевые напряжения, остаются в прежнем единичном состоянии.

При считывании информации на вторые группы разрядных металлических шин N ячеек памяти 14 (см. фиг.6) и ключевую поликремниевую шину подают низкое положительное напряжение, адресную поликремниевую шину 7 и стирающую поликремниевую шину 9 заземляют. Через запоминающие элементы и вторые группы разрядных металлических шин ток не протекает, если они находятся в нулевом состоянии; ток протекает, если они находятся в единичном состоянии. Наличие или отсутствие тока в ячейках памяти регистрируют N усилителей, подключенных к N вторым группам разрядных металлических шин 14.

В предложенной конструкции матричного накопителя возможно обеспечение быстродействия при записи логической информации 10 мкс - 1 мс, аналоги и прототип имеют быстродействие записи 10-100 мс.

Увеличение быстродействия при записи возможно за счет превышения концентрации примеси диффузионной области под вторым диэлектрическим слоем в канале лавинно-инжекционного транзистора в 2-3 раза по сравнению с диффузионной областью в канале ключевого МДП-транзистора и улучшения инжекции электронов из канала в плавающий затвор.

Увеличение концентрации примеси этой области не приведет к повышению порогового напряжения лавинно-инжекционного МДП-транзистора, так как после стирания логической информации этот транзистор имеет высокое отрицательное напряжение, считывание информации осуществляется подачей положительного напряжения на затвор ключевого МДП-транзис- тора, пороговое напряжение которого не изменится.

Матричный накопитель может быть выполнен на полупроводниковой подложке из кремния p-типа проводимости с сопротивлением более 7 Ом˙см. Толщина первого диэлектрического слоя из двуокиси кремния составляет 0,5-2 мкм, второго-третьего, четвертого диэлектрических слоев из двуокиси кремния составляет 500-800  , 3000

, 3000  соответственно. Толщина пятого диэлектрического слоя из фосфорно-силикатного стекла составляет 0,6-1,5 мкм, диффузионные слои первого типа проводимости выполнены ионным легированием бором с концентрацией примеси 2˙1016 см-3. Первые группы разрядных диффузионных шин, диффузионные слои второго типа проводимости, третьи группы разрядных диффузионных шин второго типа проводимости выполнены ионным легированием мышьяком или фосфором. Длина канала лавинно-инжекционного и ключевого МДП-транзисторов 2-3 мкм, ширина поликремниевых электродов 4-5 мкм, ширина стирающей поликремниевой шины 8 мкм, алюминиевой разводки 5-8 мкм.

соответственно. Толщина пятого диэлектрического слоя из фосфорно-силикатного стекла составляет 0,6-1,5 мкм, диффузионные слои первого типа проводимости выполнены ионным легированием бором с концентрацией примеси 2˙1016 см-3. Первые группы разрядных диффузионных шин, диффузионные слои второго типа проводимости, третьи группы разрядных диффузионных шин второго типа проводимости выполнены ионным легированием мышьяком или фосфором. Длина канала лавинно-инжекционного и ключевого МДП-транзисторов 2-3 мкм, ширина поликремниевых электродов 4-5 мкм, ширина стирающей поликремниевой шины 8 мкм, алюминиевой разводки 5-8 мкм.

По отношению к прототипу основными преимуществами предложенной конструкции являются уменьшение времени перепрограммирования за счет организации побайтового стирания информации; снижение напряжения записи за счет использования одного ключевого МДП-транзистора на n лавинно-инжекционных МДП-транзисторов с большой шириной канала, в результате чего падение напряжения на нем уменьшается; увеличение времени хранения информации за счет того, что в режиме считывания управляющие поликремниевые шины заземлены; увеличение быстродействия при записи логической информации за счет возможности увеличения концентрации примеси диффузионной области под вторыми диэлектрическими слоями в канале лавинно-инжекционного МДП-транзистора.

, на торцах поликремниевых электродов 500 - 700 @ .

, на торцах поликремниевых электродов 500 - 700 @ .

| Авторское свидетельство СССР N 921347, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1995-01-27—Публикация

1983-01-28—Подача