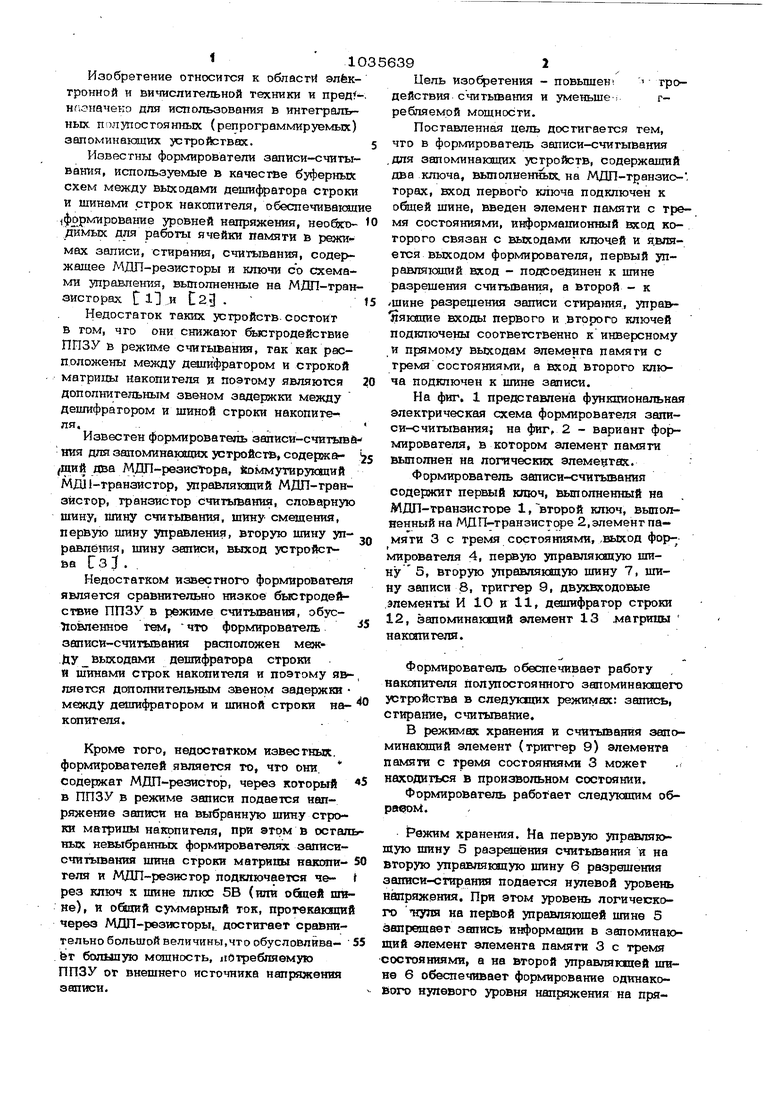

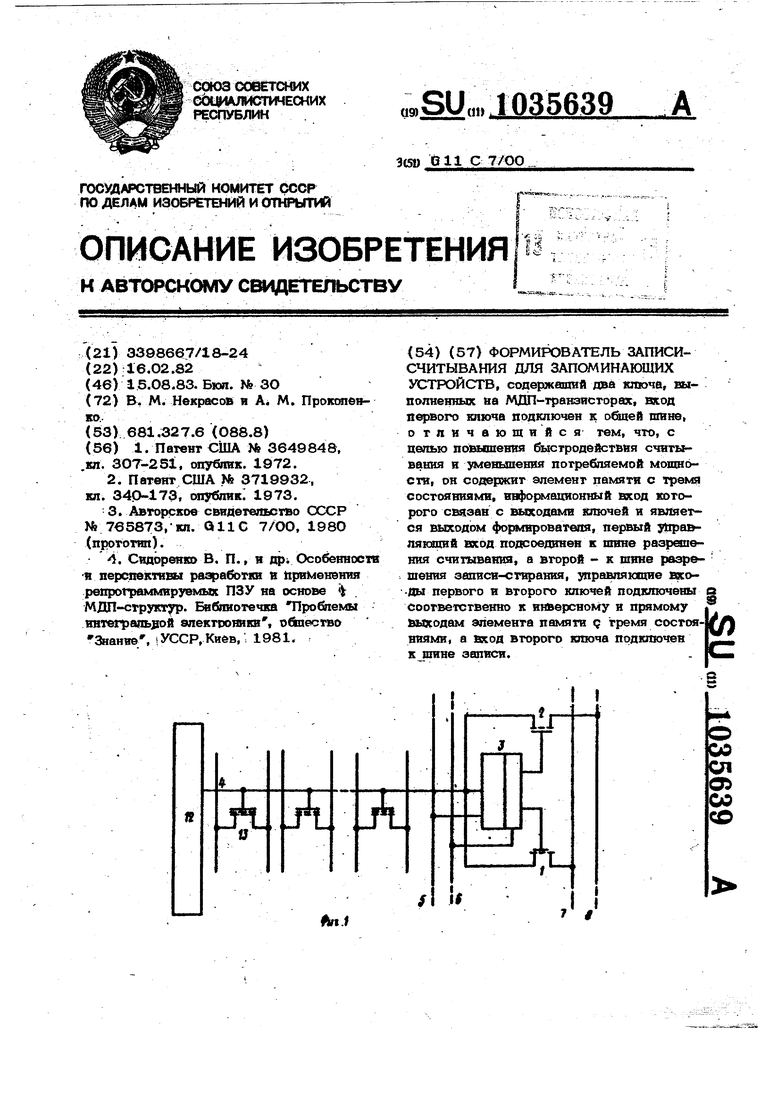

Изобретение относится к области электронной и и тельной техники и пред нг1значеко для использования в интегральных полупостоянных (репрограммирувмых) запоминающих устройствах. Известны формирователи записи-считыванпя, используемые в качестве буферных схем между выходами дешифратора строки и шинами строк накопителя, обеспечивакш (формирование уровней напряжения, необхгод ймых для работы ячейки памяти в режимах записи, стирания, считывания, содержащее МДП-резисторы и ключи со схемами управления, вьтолненные на МШ-тран зисторах С23 . Недостаток таких устройств состоит в том, что они снижают быстродействие ППЗУ в режиме считывании, так как расположены между дешифратором и строкой матрицы накопителя и поэтому являются дополнительным звеном задержки между деигафратором и шиной строки накопителя,. Известен формирователь записи-считывй ния для запоминающих устройств, содержа щий два MjQП-peзиc гopa, гоммутирукядий М/Ц1-транзистор, управляющий МДП-транзистор, транзистор считывания, словарную шину, шину считывания, шину смеддения, первую шину управления, вторую шину управлбкия, шину записи, выход устройсгва С 3 J . , Недостатком известного формирователя является сравнительно низкое быстродействие ППЗУ в режима считьгоания, обусТювленное тем, что формирователь зеписи-считъгоания расположен между выходами дешифратора строки и шиналта строк накопителя и поэтому является дсягсолни тельным звеном задержки между дешифратором и шиной строки накопителя. Кроме того, недостатком известных, формирователей является то, что они. содержат МДП-резистор, через который в ППЗУ в реясиме записи подается напряжение записи на выбранную шину строки матрицы накопителя, при этом в остал ных невыбранных формирователя записисчитьюания шина строки матрицы накопителя и МДП-резистор подключается через ключ S шине плюс 5В (гота обшей шв не), и общий суммарный ток, протекающи через МДП-резисторы, достигает сравнительно большой величины,что обусловлива- ёт большую мошность, потребляемую ППЗУ от внешнего источника напряжения записи. Цель изобретения - повьш1ен тродействия считьюания и уменьше ;гребляемрй мошности. Поставленная цель достигается тем, что в формирователь записи-считывания .для запоминаюших устройств, содержаший два ключа, вьшолнешак. на МДП-транзис-, торах, вход первого ключа подключен к общей шине, введен элемент памяти с тремя состояниями, информационный исод которого связан с выходами ключей и я.вляется выходом формирователя, первый управляющий вход - подсоединен к шине разрешения считъюания, а второй - к /шине разрешения записи стирания, управ яющие входы первого и .второго ключей подключены соответственно к инверсному и прямому выходам элемента памяти с тремя состояниями, а вход второго ключа подключен к шине записи. На фиг, 1 представлена функциональная электрическая схема формирователя записи-считывания; на фиг, 2 - вариант формирователя, в котором элемент памяти вьтолнен на логических элементах. Формирователь записи-считывания содержит первый кгаоч, выполненный на МДЛ-транзисторе 1,второй ключ, вьшолнанный на МДП-транзисгоре 2, элемент памяти 3 с тремя состояниями, ,выход фор-j мирователя 4, первую управлякииую шину 5, вторую управляюшую шину 7, шину записи 8, триггер 9, двухвходовые .элементы И 10 и 11, дешифратор строки 12, запоминакший элемент 13 матрицы накспителя. Формирователь обеспечивает работу накспителя полупостоянного запоминающего устройства в следующих режимах; запись, стирание, считывание, В режимах хранения и считывания запоминаюаоий элемент (триггер 9) элемента памяти с тремя состояниями 3 может находиться в произвольном состоянии. Формирователь работает следующим обра0оМ. Режим хранения. На первую управляющую шину 5 разрешения считьюания и на вторую управляющую шину б разрешения заяиси-стирания подается нулевой уровень напряжения. При этом уровень логического тгуля на первой управляюшей шине 5 запрещает запись информации в запоминающий элемент элемента памяти 3 с тремя состояниями, а на второй управлягаией шине 6 обеспечивает формирование одинакового нулевого уровня напряжения на пряMOM и инверсном выходах элемента памяти 3, которые запирают ключи 1 и 2.

Режим считьтвания. Ключи 1 и 2 поддеживаются в закрытом состоянии аналогично режиму хранения. Таким образом, формирователь запис -ечитьтання не оказывает влияния на работу своей строки матрицы накопителя. При считывании поступающий уровень логической единицы с выхода дешифратора 12 возбуждает запоминакщее элементы 13 строки матрицы накопителя, осуществляя при этом считывани информации подобно обь1чным полупостоятодм запоминакидим устройствам.

Режим записи. Выбор формирователя зезщ си-считывания осуществляется дешифратором 12. Уровень логической единицы или нуля с выхода деши чзатора 12 через гнину 4 формирователя поступает, как и в режиме считываний, на ии|)0рмационный вход элемента памяти 3 с тремя состояния1 1И. Одновременно (или с произвольной задержкой) с окончанием установления требуемого логического уровня на выходе дешифратора на первую управляюШую шину 5 подается сигнал с уровнем логической единипы и элемент памяти 3 устанавливается в состойние, соответствую ющее логическому уровню напряжения на выходе дешифратора.

Затем на управляющую шину 5 подается нулевой уровень напряжения и элемент памятИЗ формируетновое состояние. После этого дешифратор отктпочают или (при наличии дополнитбльной зашиты выходного каскада дешифратора от повышёйных напряжений) дешифратор оставляют включенным, а на вторую управляющую шину 6 подают напряжение уровня логической единицы. При этом на выходах f. элемента 3 -формируются напряжения, соотвётствуюшие состоянию запоминающего элемента (триггернрй схемы) элетлента йамяти, котфые подаются на управлятош:ие входы ключей 1 и 2.

При единичном состоянии элемента памяти 3, что соответствует выбранной шине строки матрицы накопителя, дешифратором 12 открьтаегся ключ 2 и через него выход 4 формирователя подключает- |СЯ к шине записи 8, а при нулевом соетоянии элемента памяти 3, что соответствует невыбранной шине строки матрицы накопителя, открывается ключ 1, через который выход формирователя подключается к обшей шине 7.

Таким образом, в режиме записи в

элемент памяти 3 предварительно записывается логическое состояние на выходе .дешифратора, затем отнлючается и не оказывает влияние на выход формиргжатеяя, а формирователь записисчитывания формирует на выходе 4 напряжение в соответствии с состоянием .элемента памяти.

Режим стирания осуществляется точно так же, как и режим записи, только, с помоиЕью дополнительного .коммутатора (внешнего) шина 8 подключается к обшей птне, а ш:ина 7 - fe внешнему источнику

записн.

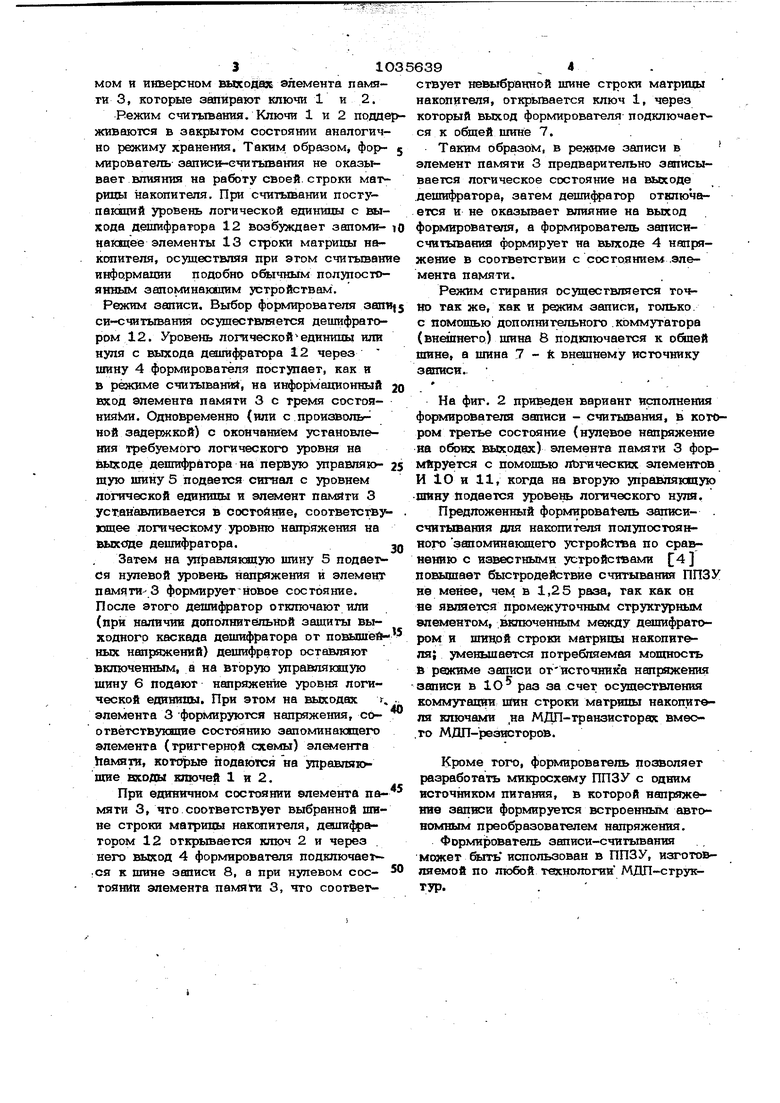

На фиг. 2 приведен вариант исполнения формирователя записи - считывания, в котром третье состояние (нулевое напряжение на о&их выходах) элемента памяти 3 формируется с помощью лЬгических элементов И 1О к 11, когда на вторую управляющую шину Подается уровень логического нуля.

Предтгоженный формирова1ель записисчитывания для накопителя полупостоянного запоминающего устройстпаа по сравнению с известными устройс1вами 4 повышает быстродействие считывания ППЗ не менее, чем в 1,25 раза, так как он не является промежуточным структурным элементом, включенным между дешифратором и шидой строки матрицы накопителя; уменьшается потребляемая мощность в режиме записи от источника напряжения записи в 1О раз за счет осуществления коммутации шин строки матрицы накопителя ключами на МДП-транзисторах вмео,то МДП-резисторов.

Кроме того, формирователь позволяет разработать микросхему ППЗУ с одним источником питания, в которой напряжение записи формируется встроенным автономным преобразователем напряжения.

Формирователь записи-считывания меже т быть использован в ППЗУ, изготовляемой по любой технологии МДП-структур.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь записи-считывания для запоминающих устройств | 1978 |

|

SU765873A1 |

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| Ячейка памяти для ОЗУ с энергонезависимым хранением информации (ее варианты) | 1982 |

|

SU1161989A1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Запоминающее устройство | 1977 |

|

SU720509A1 |

| Запоминающее устройство | 1983 |

|

SU1107176A1 |

| Полупостоянное запоминающее устройство | 1975 |

|

SU611251A1 |

ФОРМИРОВАТЕЛЬ ЗАПИСИСЧИТЫВАНИЯ ПЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ, содержащий два ключа, выполненных на Mfln-ipaHSHCTopax, вход первого ключа подключен к обшей шине, отличающийся тем, что, с целью повышения быстродействия считывания и уменьшения потребляемой МОЕШОсти, он содержит элемент памяти с тремя состояниями, информационный вкод которого связан с выходами ключей и яв юется выходом формирователя, первый уьравлякяций вход подсоединен к шине разрешения считывания, а второй - к шине разрешения записи-стирания, равляющие вкоды первого и второго ключей подключены соответственно к инверсному и прямому ВЫ}содам элемента памяти Q тремя состояниями, а вход второго ключа подключен к шине записи. 00 ел О) со со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ЭЛЕКТРОННО-ОПТИЧЕСКАЯ СИСТЕМА | 0 |

|

SU364984A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| П., н др1 Особенности я перспективы разработки и Ири ленентш репрограммируемых ПЗУ на основе «|: МДП-структзф | |||

| Библиотечка Пробдемы интеграпь й электроники , обшество ЗнаниеЛ УССР,Киев,; 1981 | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1983-08-15—Публикация

1982-02-16—Подача