(54) МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Делительное устройство | 1972 |

|

SU477425A1 |

| Устройство для умножения | 1976 |

|

SU615476A1 |

| Вероятностный спектрокоррелометр | 1979 |

|

SU942033A1 |

| Вероятностное множительное устройство | 1979 |

|

SU773628A1 |

| Адаптивный вероятностный спектрокоррелятор | 1979 |

|

SU955087A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1967 |

|

SU222740A1 |

| Арифметическое устройство | 1976 |

|

SU656059A1 |

| АНАЛОГО-ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2123720C1 |

| ОДНОТАКТНОЕ ЦИФРОВОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU330450A1 |

Изобретение относится к вычислительной технике и предназначено для пере.миожения величин стохастическим способом.

Известно множительное устройство, содержащее генератор случайных чисел, регистры сомножителей и результата, схему совпадения и схемы сравнения.

Но это устройство имеет низкое быстродействие.I Наиболее близким по технической сущности к предлагаемому является множительное yciройство, содержащее регистр результата, регистры операндов, выходы разрядов которых соединены с первой группой входов первого блока элементов И, вторая группа входов которого соединена с генератором тактовых импульсов и первой группой входов второго блока элементов И, вторая группа входов которого подключена к датчику случайных чисел, а выходы блоков элементов И соединены с соответствующими входа.ми схем сравнения.

Низкое быстродействие этого устройства обусловлено необходимостью проведения большого числа статистических испытаний в процессе вычисления произведения.

Цель изобретения - повышение быстродействия множительного устройства.

Это достигается тем, что в предлагаемое устройство введен логический блок умножения, соединенный с регистром результата.

причем входы логического блока умножения подключены к выходам схем сравнения и выходам первого блока элементов И, соединенного со старшими разрядами регистров операпдов. В предлагаемо.м устройстве используется многосимвольное вероятностно-импульсное представление сомножителей и произведения.

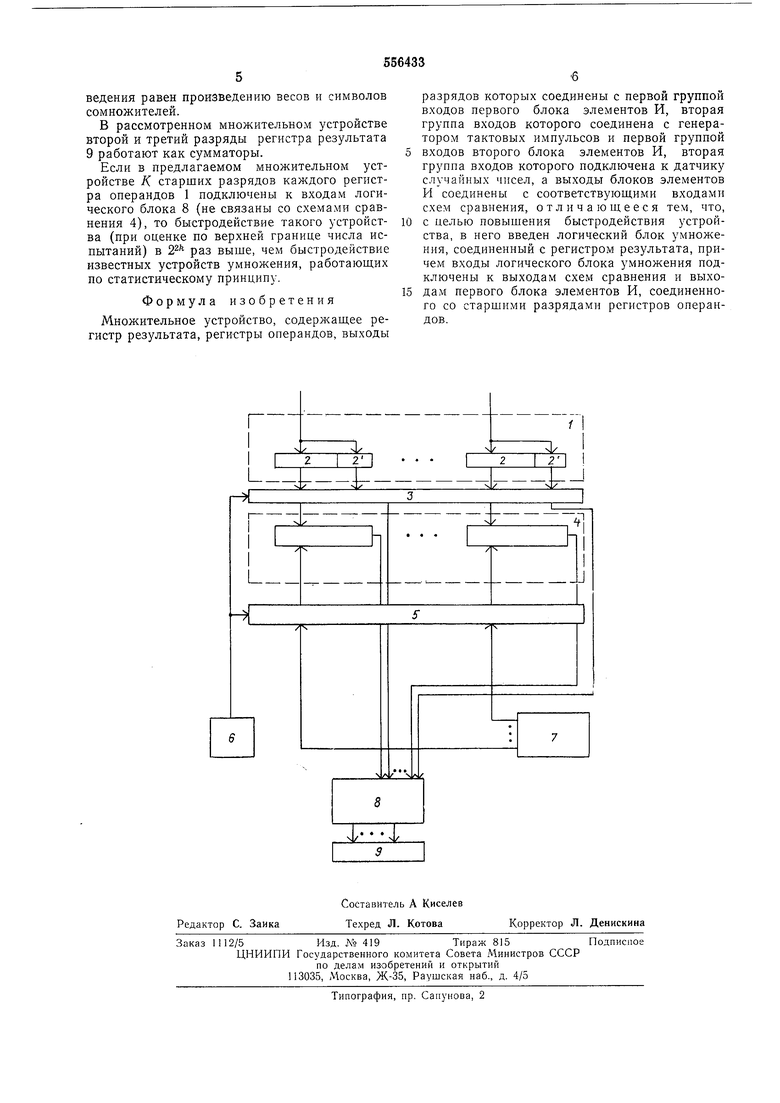

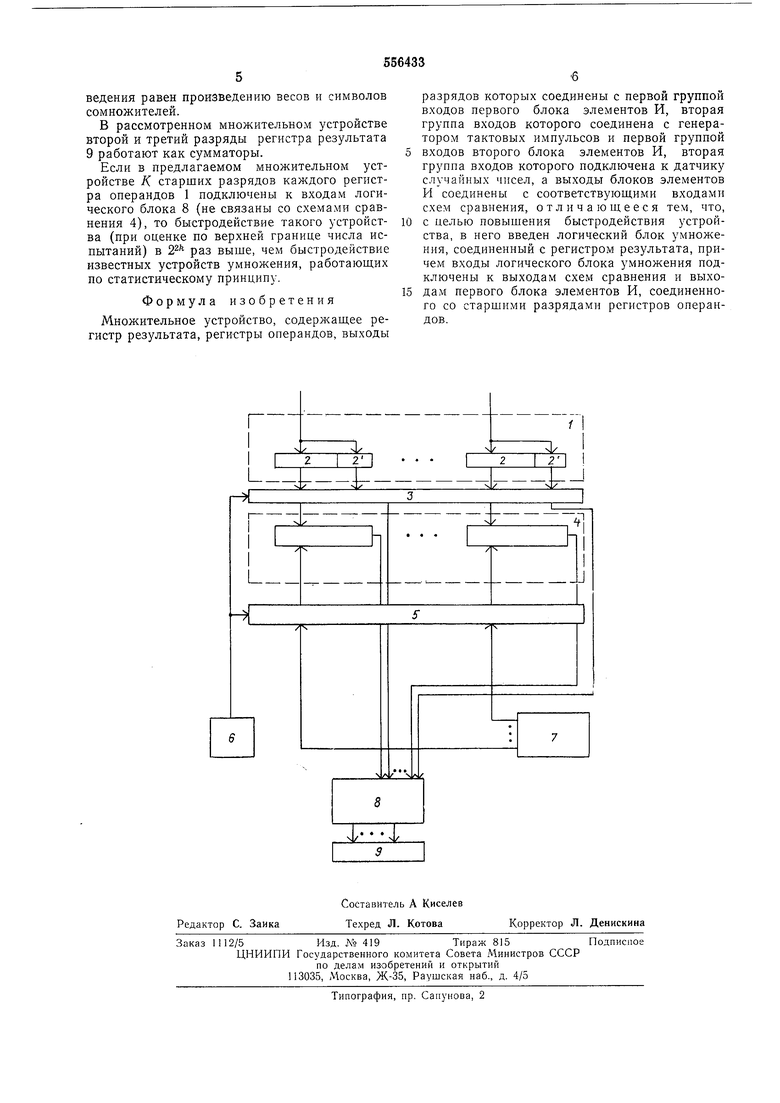

На чертеже представлена блок-схема предлагаемого множительного устройства.

Оно состоит из регистров операндов 1, старшие разряды 2 которых и выходы младших разрядов 2 соединены с первым блоком элементов И 3. Устройство содержит также схемы сравнения 4, второй блок элементов И 5, генератор тактовых импульсов 6, датчик случайных чисел 7, логический блок умножения 8 и регистр результата 9.

Устройство работает по статистическому

принципу. Двоичные коды сомножителей Хг, заданных на интервале (0,1), записываются в соответствующие регистры операндов 1. При подаче тактового импульса с генератора 6 на блок элементов И 3 на первые входы

схем сравнения 4 списываются значения xi, соответствующие младшим разрядам кодов сомножителей. На вторые входы схе.м сравнения 4 списываются случайные числа Ri с разных выходов датчика случайных чисел 7. Если

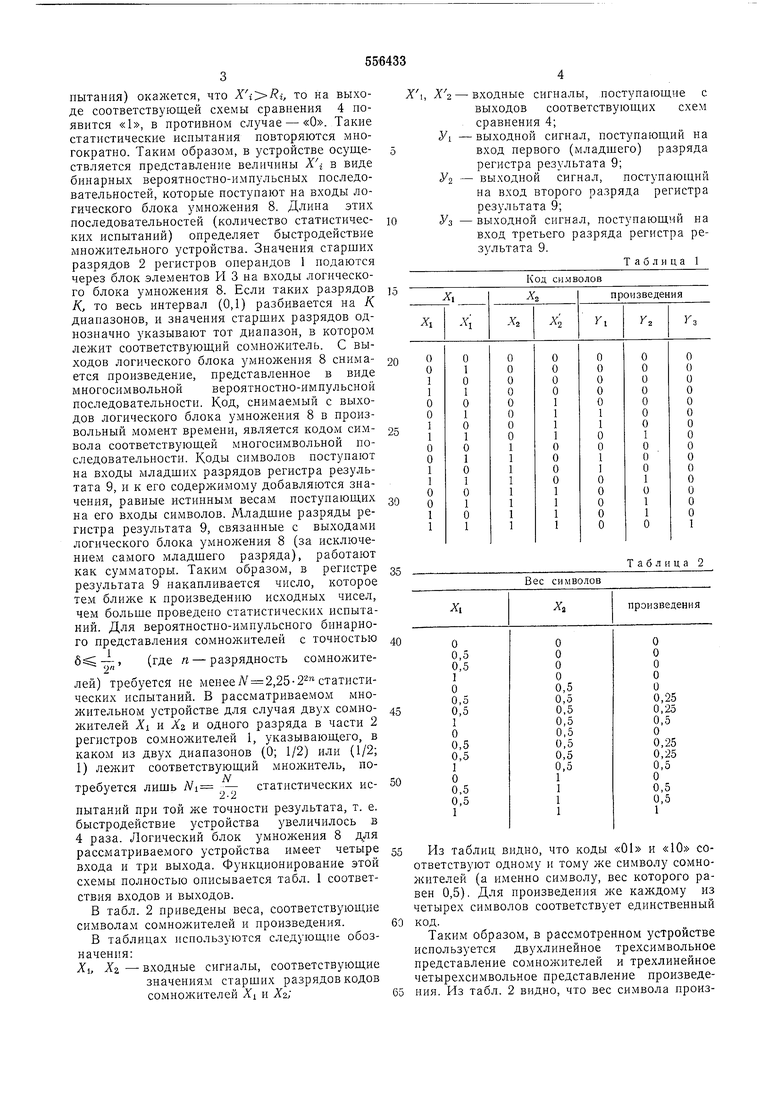

в результате сравнения (статистического испытания) , что , то на выходе соответствующей схемы сравнения 4 появится «1, в противном случае - «О. Такие статистические испытания повторяются многократно. Таким образом, в устройстве осуществляется представление величины X.i в виде бинарных вероятностно-импульсных иоследовательностей, которые поступают на входы логического блока умножения 8. Длина этих последовательностей (количество статистических испытаний) определяет быстродействие мнолсительного устройства. Значения старших разрядов 2 регистров операндов 1 подаются через блок элементов И 3 на входы логического блока умножения 8. Если таких разрядов К, то весь интервал (0,1) разбивается на К диапазонов, и значения старших разрядов однозначно указывают тот диапазон, в котором лежит соответствующий сомножитель. С выходов логического блока умножения 8 снимается произведение, представленное в виде многосимвольной вероятностно-импульсной последовательности. Код, снимаемый с выходов логического блока умножения 8 в произвольный момент времени, является кодом символа соответствующей многосимвольной последовательности. Коды символов поступают на входы младших разрядов регистра результата 9, и к его содержимому добавляются значения, равные истинны.м весам поступающих на его входы символов. Младидне разряды регистра результата 9, связаииые с выходами логического блока умнол ения 8 (за исключением самого младщего разряда), работают как сумматоры. Таким образом, в регистре результата 9 накапливается число, которое тем ближе к произведению исходных чисел, чем больше проведено статистических испытаний. Для вероятностно-импульсного бинарного представления сомножителей с точностью , (где л - разрядность сомнол ителей) требуется не менее Л 2,25-22 статистических испытаний. В рассматриваемом множительном устройстве для случая двух сомножителей 1 и и одного разряда в части 2 регистров сомножителей 1, указывающего, в каком из двух диапазонов (0; 1/2) или (1/2; 1) лежит соответствующий мнолштель, по,, N треоуется лишь Ni /- статистических испытаний при той же точности результата, т. е. быстродействие устройства увеличилось в 4 раза. Логический блок умножения 8 для рассматриваемого устройства имеет четыре входа и три выхода. Функционирование этой схемы полностью описывается табл. 1 соответствия входов и выходов. В табл. 2 приведены веса, соответствующие символам сомножителей и произведения. В таблицах используются следующие обозначения:Xi, Xz - входные сигналы, соответствующие значениям старщих разрядов кодов сомнол ;ителей Х и Xz; входные сигналы, поступающие с выходов соответствующих схем сравнения 4; выходной сигиал, поступающий на вход первого (младшего) разряда регистра результата 9; выходной сигнал, поступающий на вход второго разряда регистра результата 9; выходной сигнал, поступающий на вход третьего разряда регистра результата 9. Таблица 1 Код символов Таблица 2 Вес символов иц видно, что коды «01 и «10 сот одному и тому же символу сомноа именно символу, вес которого раля произведения из мволов соответствует единственный бразом, в рассмотренном устройстве ся двухлинейное трехсимвольное ние сомнол ;ителей и трехлинейное вольное представление произведебл. 2 видно, что вес символа ироизведения равен произведению весов и символов сомножителей.

В рассмотренном множительном устройстве второй и третий разряды регистра результата 9 работают как сумматоры.

Если в предлагаемом множительном устройстве К старших разрядов каждого регистра операндов 1 подключены к входам логического блока 8 (не связаны со схемами сравнения 4), то быстродействие такого устройства (при оценке по верхней границе числа испытаний) в раз выше, чем быстродействие известных устройств умножения, работаюших по статистическому принципу.

Формула изобретения

Множительное устройство, содержашее регистр результата, регистры операндов, выходы

разрядов которых соединены с первой группой входов первого блока элементов И, вторая группа входов которого соединена с генератором тактовых импульсов и первой группой

входов второго блока элементов И, вторая группа входов которого подключена к датчику случайных чисел, а выходы блоков элементов И соединены с соответствующими входами схем сравнения, отличающееся тем, что,

с целью повышения быстродействия устройства, в него введен логический блок умножения, соединенный с регистром результата, причем входы логического блока умножения подключены к выходам схем сравнения и выходам первого блока элементов И, соединенного со старшими разрядами регистров операндов.

Авторы

Даты

1977-04-30—Публикация

1972-09-26—Подача