(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1972 |

|

SU556433A1 |

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ КОРРЕЛОМЕТР | 1972 |

|

SU419895A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1101836A1 |

| Делительное устройство | 1972 |

|

SU477425A1 |

| Конвейерное множительное устройство | 1980 |

|

SU903866A1 |

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| Последовательное множительное устройство | 1981 |

|

SU987620A1 |

| Последовательное множительное устройство | 1984 |

|

SU1233138A1 |

Изобретение относится к области вычи лителыюй техники, в частности к цифровым множительным устройствам.

Известны устройства для умложёния с промежуточным преобразованием кодов

сомножителей в последовательности импульсов. Например, множительное устройство iJcoaepsKKT регистры,операндов младшие разряды которых через блоки сх И соединены с первымв входами схемы сравнения, вторые входы которой соеди- нены с датчиком случайных чисел. Выходы схемы с авнения соединены с логическим устройством умножения, выходы которого соединены с регистром результата.

Недостатками указанного устройства являются наличие в нем сложного функционального узла - датчика случай- ных чисел и низкое быстродействие.

Наиболее близким Jrexничecким решением к изобретению является устройство для умножения, содержащее первый н второй h разрядные регистры, блок

сравнения бпок умножения элементы И, блок элементов ИЛИ, первый и второй счетчики, пбфвый( сумматор. BXOJ ная шина устройства соединена с входом первого счетчика, первая группа ||выходов которого соединена с первыми входами элементов И. входы эламевтов И соединены с выходами tl - Kljn 1 nawu«x. разрядов первотю peretcrpa, а выходы алементов.И - с входама блока элементов ИЛИ. Вторая группа {выходов первого счетчика соединена с первыми входами блока сравнения, вторые входы которого подключены к выходамН-кмладшнйГраз- рядов второго; регистра. 13ыход блока умножения соединен с входом первого сумк матора, выход которого соед1 нен с входом второго счетчика, выходы первого сум- матера и второго счетчика соединены с выходными шинами устройства 2j.

Недостаток устройства - низкое быотродействие.

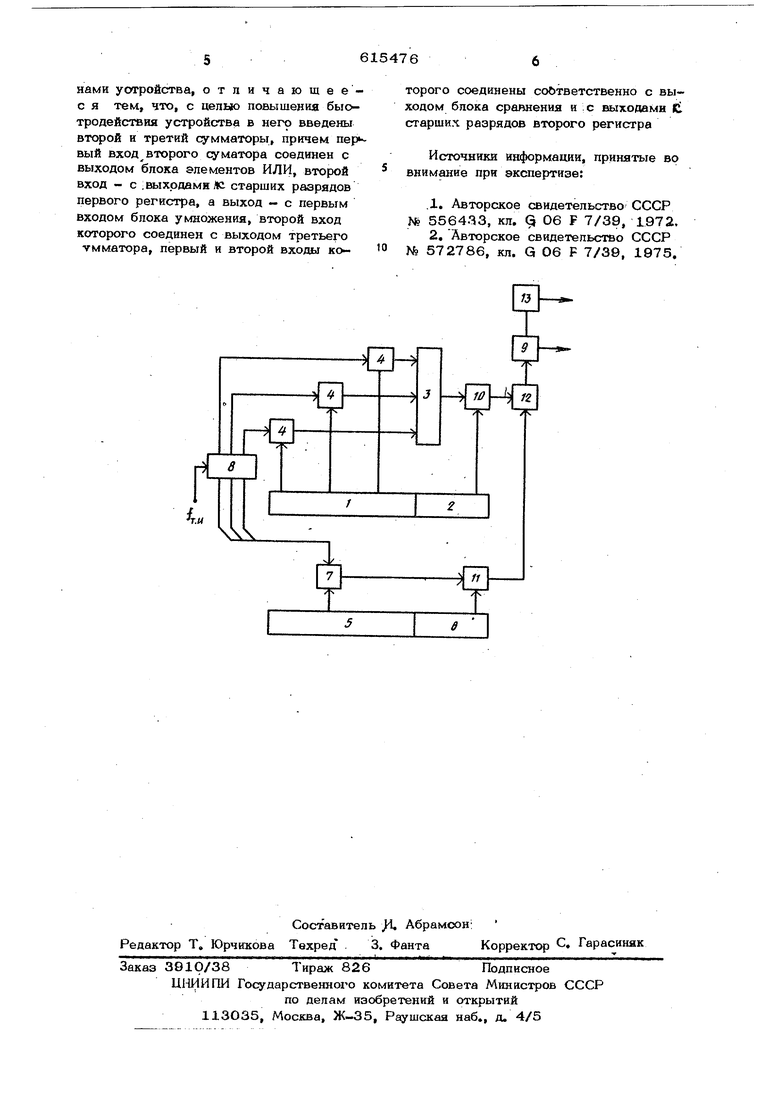

Целью изобретения является повыtyeHHe. быстродействия. Зто достигается тем, что в устройство введены второй и третий суммаах ры. Причем первый вход второго сумматора соединен с выxoдo f. блока элементов ИЛИ, второй вход - с выходами |С старших разрядов первого регистра, а выход - с первым входом блока умножения. Второй вход последнего соединен с выходом третьего сумматора, первый и второй входы которого соединены соответственно с выходом блока сравнения и с вы ходами к старших ; разрядов второго регистра, Блок-схема устройства представлена на чертеже. Устройство содержит регистр с группой П- К младших разрядов 1 и группой К старших разрядов 2, блок 3 эле ментов ИЛИ, элементы И 4, регистр с группой (п- к) младших разрядов 5 и группой--К старших разрядов 6, блок сравнения 7, счетчик 8, сумматоры 9, 10 и 11, логический блок у множен ш 12, счетчик результатов 13. Устройство работает следующим образом. Время вычислений определяется циклом ,работы счетчика 8 и равно 2 После одного цикла работы счетчик 8 ос навливается и в сумматоре 9 и счетчике 13 фиксируется результат умножения. Младшие,П-К разряды сомножителей j ,и М преобразуются в число имлульсов и временной интервал, соответствую щие преобразуемым младшим разрядам сомножителей N и Мд, При поступлении нулевого сигнала с выхода блока 3 элементов ИЛИ с выхода сумматора 1О снимается код N„-+0 старших К разрядов 2 первого регистра. При поступлени нулевогх сигнала с выхода блока 3 с выхода сумматора 10 снимается код . Таким образом, за 2 такта работы устройства число N,j поступает на первый вход блока 12 умножения , а число Н -Ыраз, С выхода сумматора 11 во время на личия на его первом входе временного щ тепвала да тапьности ,/, что соответствует И тактам входной частоты - , снимается код М, „и М коды старших разрядов первого и второго сомножителей, хранящихся в частях 2 и 6 регистров. Во время отсутствия на входе сумматора 11 этого временного интервала, что соответствует тактам частоты f-.v, с его выхода снимается кодАЛ +О. Таким образом, за рой ВХОД блока 12 умножения число 1 поступает 2 -М раз, а число ( - М раз. После перемножения в блоке 12 с его выхода снимается коаМ /2 число раз, paBHoe()( код CM2t4) число раз, рав-. Hoe(,)M ; код М2(. il число раз, равное N , код - число равное N ЛЛ , Эти коды суммируются накапливающим сумматором 9 и счетчиком 13, Их сумма 5- 2()(,НМ,4.1)ЦГ,. (,)М2()АГ,(,) ММ2Н){М2+1)()-1-. После упрощен1ш 2)(M.,) s то является результатом перемножения сомножителей ,Л, N Время выполнения операции умноже- 2 tt -, kия равно Предложенное устройDTBO целесообразно использовать при К « п , так как при этом получают существенное повышение производитель ности практически без увеличения аппаратурных затрат. Формула изобретения Устройство для умножения, содержащее первый и второй h-разрядные регистры, блок сравнения, блок умножения, элементы И, блок элементов ИЛИ, первый и второй счетчики, первый сумматор, причем входная шина устройства соединена с входом первого счетчика, первая группа выходов, которого соединена с первыми входами элементов И, вторые входы которых подключены к выходам, п-к ( rv ) младших разрядов первого регистра, а выходы элементов И соединены с входами блокаЭлементов ИЛИ, вторая группа выходов первого.счетчика соединена с первыми входами блока сравнения, вторые входы которого подключены к выходам П-к младших разрядов второго регистра, выход блока умножения соединен с входом первого сумматора, выход которого соединен с входом второго счетчика, выходу пеового суммлтооа и BTODO-

нами устройства, отдичаюшеес я тем, что, с целые повышения быстродействия устройства в негр введены второй и третий сумматоры, причем пер вый вход второго суматора соединен с выходом блока элементов ИЛИ, второй вход - с ;ш 1Хрдамн 1 старших разрядов первого регистра, а выход - с первым входом блока умножения, второй вход которого соединен с выходом третьего умматора, первый и второй входы которого соединены соЬтветственно с выходом блока сравнения и с выходами it старших разрядов второго регистра

Источники информации, принятые вр внимание при экспертизе:

,1. Авторское свидетельство СССР № 556433, кл. 9 06 F 7/39, 1972.

Авторы

Даты

1978-07-15—Публикация

1976-01-22—Подача