соединен с выходом узла унравления пуском распределителя.

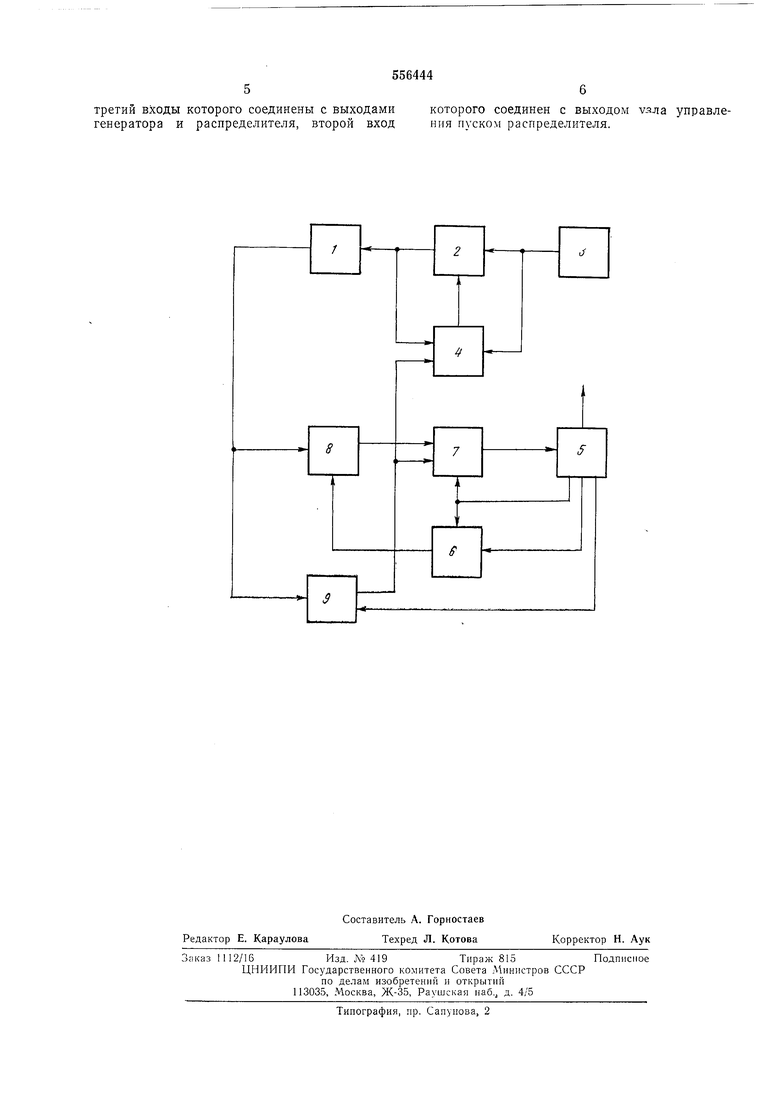

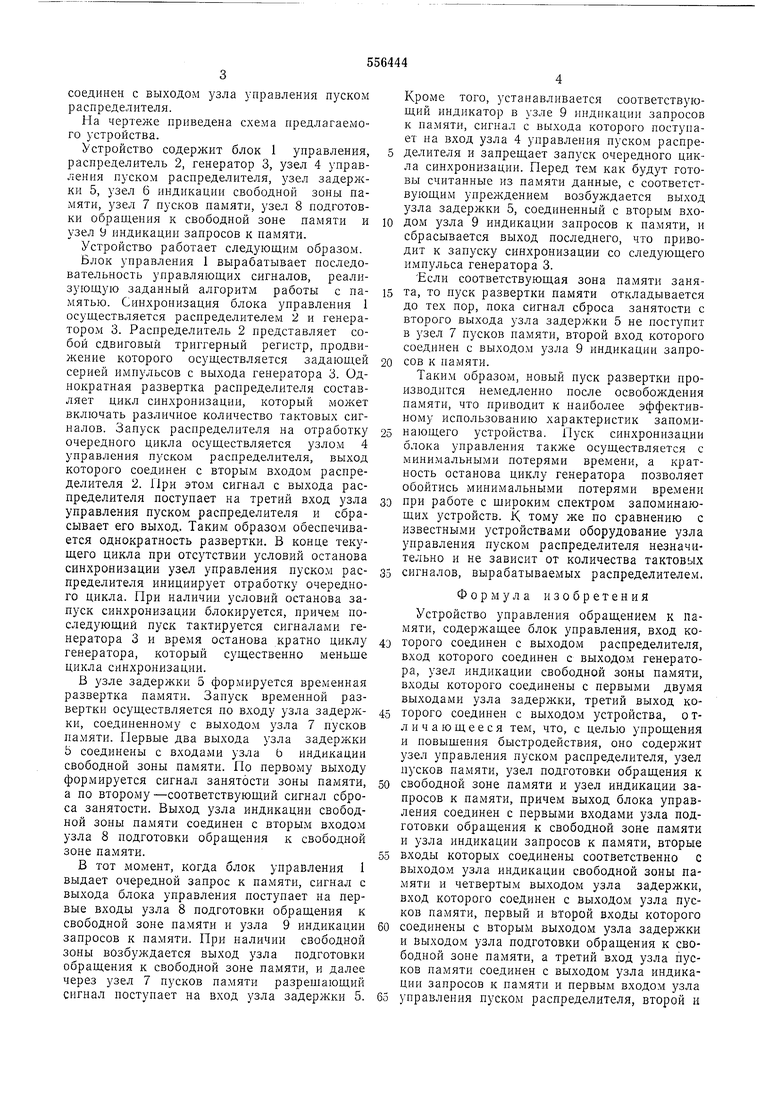

На чертеже приведена схема предлагаемого устройства.

Устройство содержит блок 1 управления, распределитель 2, генератор 3, узел 4 управления пуском распределителя, узел задержки 5, узел 6 индикации свободной зоны памяти, узел 7 пусков памяти, узел 8 подготовки обраш,ения к свободной зоне памяти и узел 9 индикации запросов к памяти.

Устройство работает следующим образом.

Блок управления 1 вырабатывает последовательность управляющих сигналов, реализующую заданный алгоритм работы с памятью. Синхронизация блока управлеиия 1 осуществляется распределителем 2, и генератором 3. Распределитель 2 представляет собой сдвиговый триггерный регистр, продвижение которого осуществляется задающей серией импульсов с выхода генератора 3. Однократная развертка распределителя составляет цикл синхронизации, который может включать различное количество тактовых сигналов. Запуск распределителя на отработку очередного цикла осуществляется узлом 4 управления пуском распределителя, выход которого соединен с вторым входом распределителя 2. При это.м сигнал с выхода распределителя поступает на третий вход узла управления пуском распределителя и сбрасывает его выход. Таким образом обеспечивается однократность развертки. В конце текущего цикла при отсутствии условий останова синхронизации узел управления пуском распределителя инициирует отработку очередного цикла. При наличии условий останова запуск синхронизации блокируется, причем последующий пуск тактируется сигналами генератора 3 и время останова кратно циклу генератора, который существенно меньще цикла синхронизации.

В узле задержки 5 формируется временная развертка памяти. Запуск временной развертки осуществляется по входу узла задержки, соединенному с выходом узла 7 пусков памяти. Первые два выхода узла задержки 5 соединены с входами узла b индикации свободной зоны памяти. По первому выходу формируется сигнал занятости зоны памяти, а по второму-соответствующий сигнал сброса занятости. Выход узла индикации свободной зоны памяти соединен с вторым входом узла 8 подготовки обращения к свободной зоне памяти.

В тот момент, когда блок управления 1 выдает очередной запрос к памяти, сигнал с выхода блока управления поступает на первые входы узла 8 подготовки обращения к свободной зоне памяти и узла 9 индикации запросов к памяти. При наличии свободной зоны возбуждается выход узла подготовки обращения к свободной зоне памяти, и далее через узел 7 пусков памяти разрещающий сигнал поступает на вход узла задержки 5.

Кроме того, устанавливается соответствующий индикатор в узле 9 индикации запросов к памяти, сигнал с выхода которого поступает на вход узла 4 управления пуском распределителя и запрещает запуск очередного цикла синхронизации. Перед тем как будут готовы считанные из памяти данные, с соответствующим упреждением возбуждается выход узла задержки 5, соединенный с вторым входом узла 9 индикации запросов к памяти, и сбрасывается выход последнего, что приводит к запуску синхронизации со следующего импульса генератора 3. Если соответствующая зона памяти занята, то пуск развертки памяти откладывается до тех пор, пока сигнал сброса занятости с второго выхода узла задержки 5 не поступит в узел 7 пусков памяти, второй вход которого соединен с выходом узла 9 индикации запросов к памяти.

Таким образом, новый пуск развертки производится немедленно после освобождения памяти, что приводит к наиболее эффективному использованию характеристик запоминающего устройства. Пуск синхронизации блока управления также осуществляется с минимальныА1и потерями времени, а кратность останова циклу генератора позволяет обойтись минимальными потерями времени

при работе с щироким спектром запоминающих устройств. К тому же по сравнению с известными устройствами оборудование узла управления пуском распределителя незначительно и не зависит от количества тактовых

сигналов, вырабатываемых распределителем.

Формула изобретения

Устройство управления обращением к памяти, содержащее блок управления, вход которого соединен с выходом распределителя, вход которого соединен с выходом генератора, узел индикации свободной зоны памяти, входы которого соединены с первыми двумя выходами узла задержки, третий выход которого соединен с выходо.м устройства, отличающееся тем, что, с целью упрощения и повышения быстродействия, оно содержит узел управления пуском распределителя, узел пусков памяти, узел подготовки обращения к

свободной зоне памяти и узел индикации запросов к памяти, причем выход блока управления соединен с первыми входами узла подготовки обращения к свободной зоне памяти и узла индикации запросов к памяти, вторые

входы которых соединены соответственно с выходом узла индикации свободной зоны памяти и четвертым выходом узла задержки, вход которого соединен с выходом узла пусков памяти, первый и второй входы которого

соединены с вторым выходом узла задержки и выходом узла подготовки обращения к свободной зоне памяти, а третий вход узла пусков памяти соединен с выходом узла индикации запросов к памяти и первым входом узла

управления пуском распределителя, второй и

третий входы которого соединены с выходами генератора и распределителя, второй вход

которого соединен с выходом узла управления пуском распределителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления памятью | 1983 |

|

SU1119020A1 |

| Устройство для сопряжения процессора с памятью | 1980 |

|

SU898437A1 |

| Процессор | 1976 |

|

SU670935A1 |

| Устройство для сопряжения памяти с процессором | 1983 |

|

SU1142838A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Устройство для управления обменом информацией процессора с памятью | 1988 |

|

SU1587525A1 |

| Устройство связи для вычислительной системы | 1980 |

|

SU924694A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

Авторы

Даты

1977-04-30—Публикация

1975-04-04—Подача