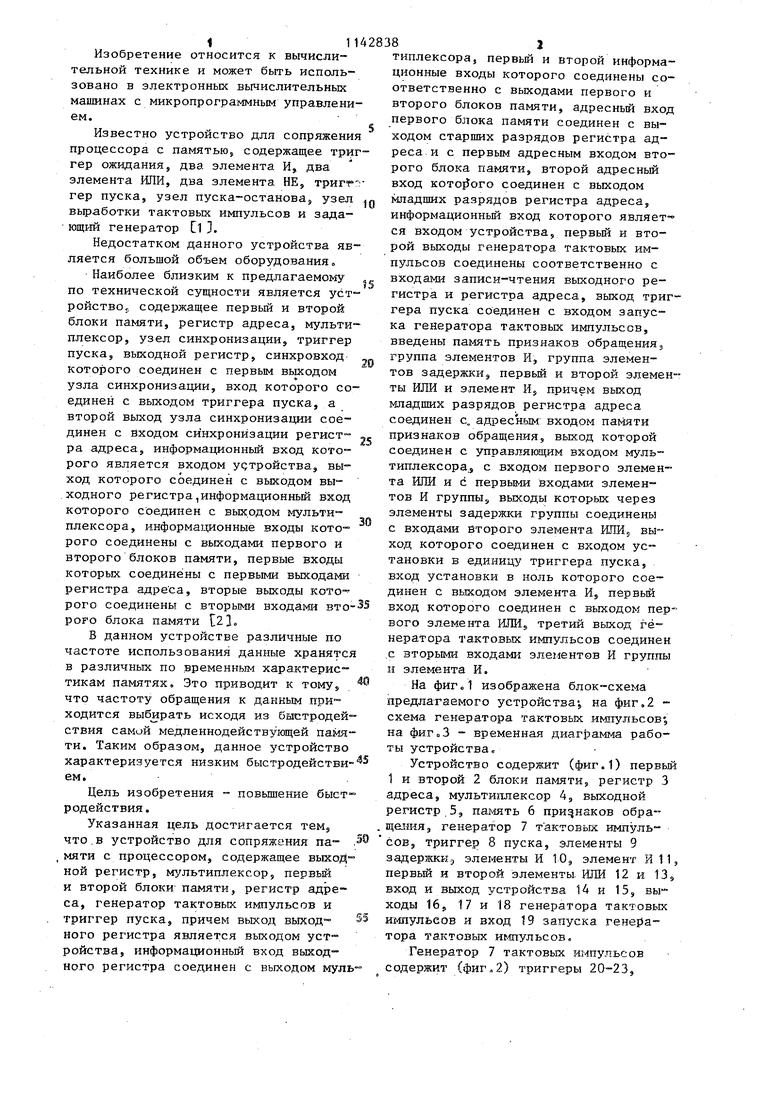

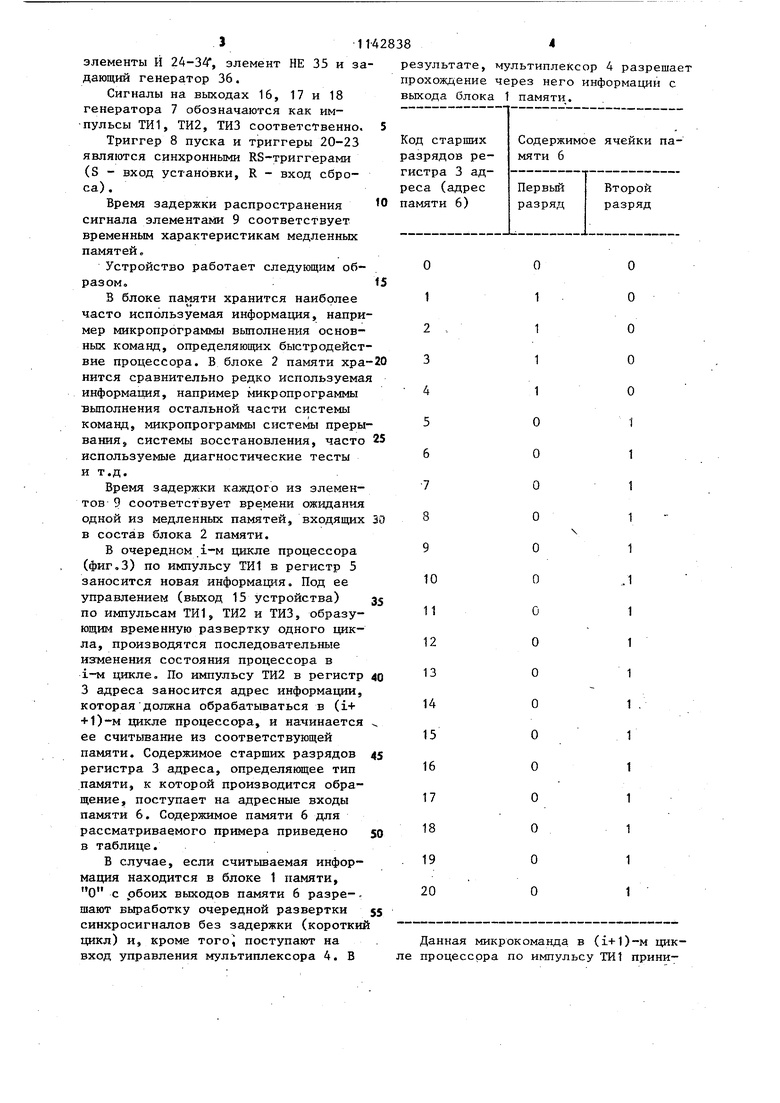

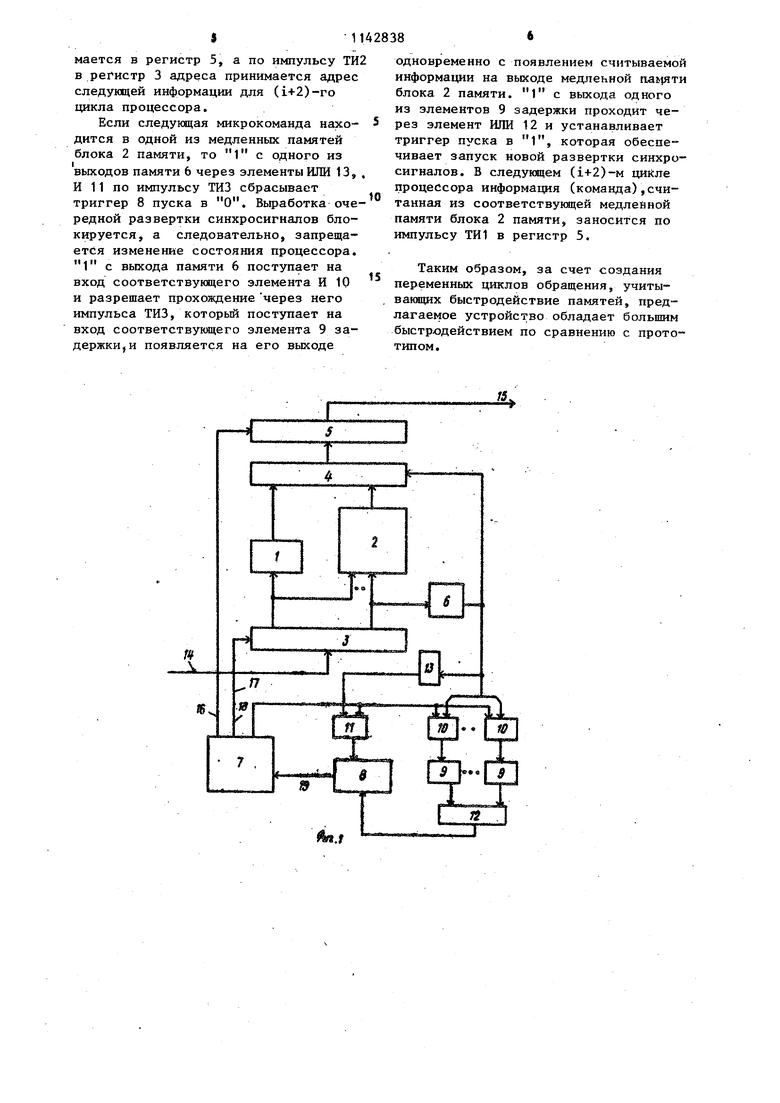

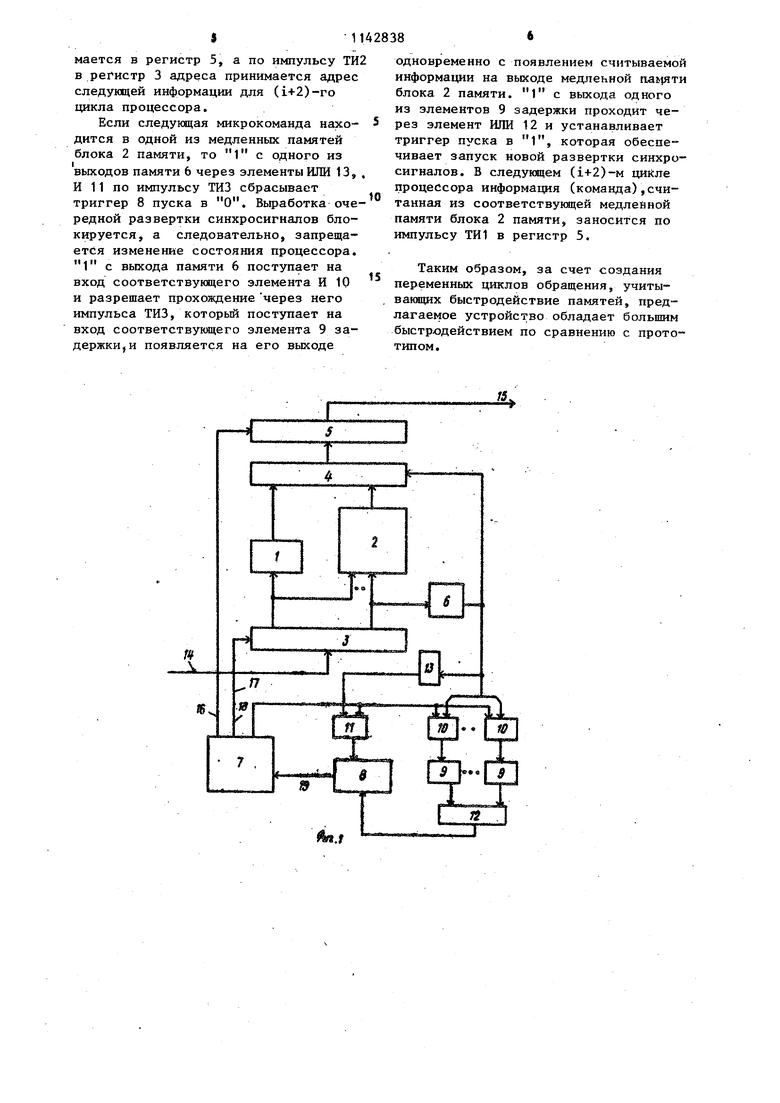

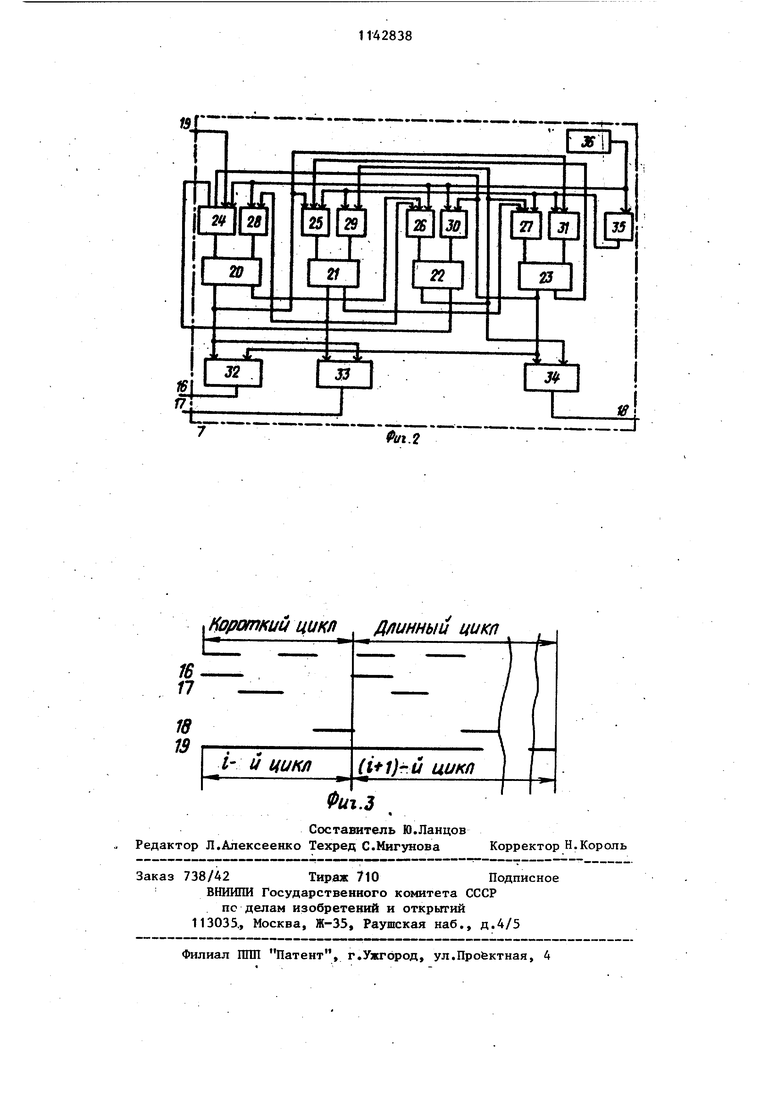

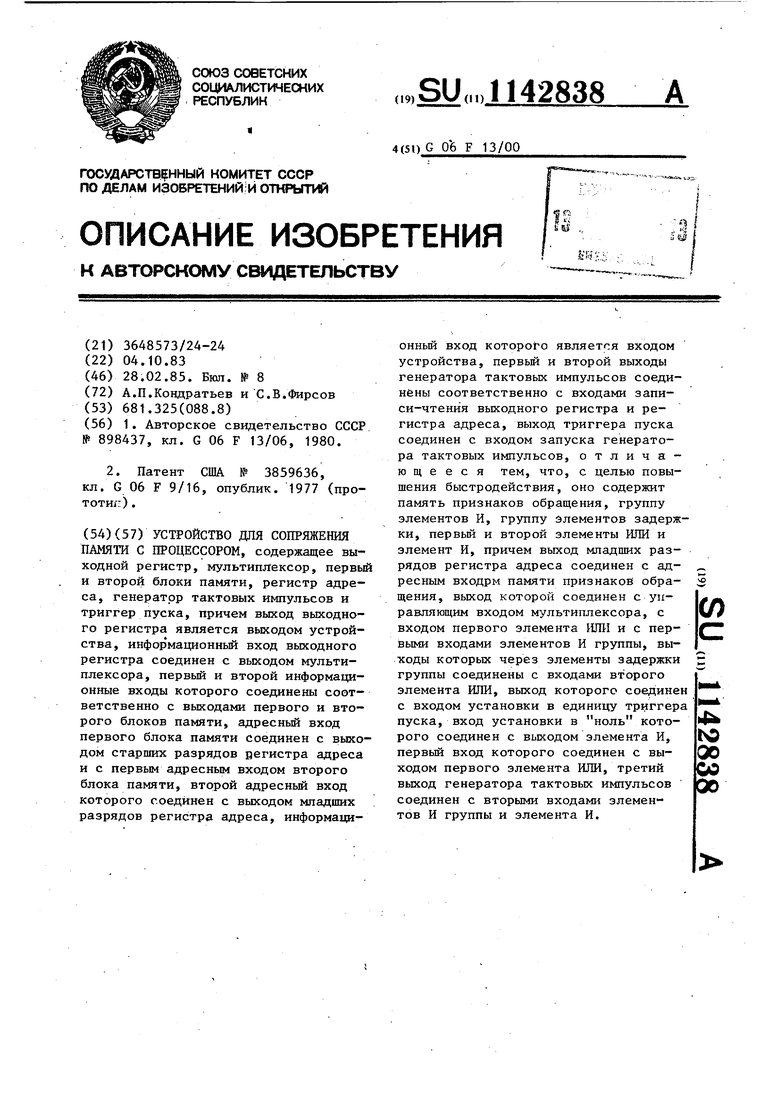

Изобретение относится к вычислительной технике и может быть использовано в электронных вычислительных машинах с микропрограммным управлени ем. Известно устройство для сопряжени процессора с памятью, содержащее три гер ожидания, два элемента И, два элемента ИЛИ, два элемента НЕ, тригг гер пуска, узел пуска-останова} узел выработки тактовых импульсов и задающий генератор Cl . Недостатком данного устройства яв ляется большой объем оборудования Наиболее близким к предлагаемому по технической сущности является уст ройство,., содержащее первый и второй блоки памяти, регистр адреса, мульти плексор, узел синхронизации, триггер пуска, выходной регистр, синхровход которого соединен с первым выходом узла синхронизации, вход которого со единен с выходом триггера пуска, а второй выход узла синхронизации соединен с входом синхронизации регистра адреса, информационный вход которого является входом устройства, выход которого соединен с выходом выходного регистра,информационный вход которого соединен с выходом мультиплексора, информационные входы которого соединены с выходами первого и второго блоков памяти, первые входы которых соединены с первыми выходами регистра адреса, вторые выходы которого соединены с вторыми входа1УН вто POFO блока памяти .2l В данном устройстве различные п:о частоте использования данные хранятс в различных по временным характеристикам памятях. Это приводит к тому,, что частоту обращения к данным приходится выб ирать исходя из быстродей ствия самой медленнодействующей памя ти. Таким образом, данное устройство характеризуется низким быстродействи ем. Цель изобретения - повышение быст родействия. Указанная цель достигается тем, что.в устройство для сопряжения па мяти с процессором, содержащее выход ной регистр, мультиплексор, первьй и второй блоки памяти, регистр адреса, генератор тактовых импульсов и триггер пуска, причем выход выходного регистра является выходом устройства, информационньш вход выход™ ного регистра соединен с выходом мул типлексора, первый и второй информационные входы которого соединены соответственно с выходами первого и второго блоков памяти, адресный вход первого блока памяти соединен с выходом старших разрядов регистра адреса и с первым адресным входом второго блока памяти, второй адресньй вход KOTOiJoro соединен с выходом младших разрядов регистра адреса, информационньй вход которого являет- ся входом устройства, первьй и второй выходы генератора тактовых импульсов соединены соответственно с входами записи-чтения выходного регистра и регистра адреса, выход триггера пуска соединен с входом запуска генератора тактовых импульсов, введены память признаков обращенияэ группа элементов И, группа элементов задержки, первый и второй элементы ИЛИ и элемент И, причем выход младших разрядов регистра адреса соединен с. адресньм: входом памяти признаков обращения, выход которой соединен с управляющим входом мультиплексора., с входом первого элемента ИЛИ и с первыми входами элементов И rpynnHj выходы которых через элементы задерлски группы соединены с входами второго элемента ИЛИ;, выход которого соединен с входом установки в единицу триггера пуска, вход установки в ноль которого соединен с выходом элемента И, первьй вход которого соединен с выходом первого элемента ИЛИ, третий выход генератора тактовых импульсов соединен с вторыми входами элементов И группы и элемента И. На фиг„1 изображена блок-схема предлагаемого устройства- на фиг.2 схема генератора тактовых импульсов-, на фиГеЗ - временная диаграшта работы устройства. Устройство содержит (фиг.1) первьй 1 и второй 2 блоки памяти, регистр 3 адреса, мультиплексор 4, выходной регистр 5, б признаков обраща жя, генератор 7 тактовых импульсов, триггер 8 пуска, элементы 9 задержки, элементы И 10, элемент И 11, первьй и второй элементы. ИЛИ 12 и 13, вход и выход устройства 14 и 15, выходы 16,, 17 и 18 генератора тактовых ш-шульсов и вход 19 запуска генератора тактовых иг.шульсов. Генератор 7 тактовых импульсов содержит (фиг„2) триггеры 20-23, 311-428 элементы И 24-34, элемент НЕ 35 и задающий генератор 36. Сигналы на выходах 16, 17 и 18 генератора 7 обозначаются как импульсы ТИ1, ТИ2, ТИЗ соответственно. 5 Триггер 8 пуска и триггеры 20-23 являются синхронными RS-триггерами (S - вход установки, R - вход сброса) . Время задержки распространения сигнала элементами 9 соответствует временным характеристикам медленных памятей« Устройство работает следующим образом, В блоке памяти хранится наиболее часто используемая информация, например микропрограммы выполнения основных команд, определяющих быстродействие процессора. В блоке 2 памяти хра-20 нится сравнительно редко используемая информация, например шкропрограммы выполнения остальной части системы команд, микропрограммы системы прерывания, системы восстановления, часто 25 используемые диагностические тесты и т.д. Время задержки каждого из элементов 9 соответствует времени ожидания одной из медленных памятей, входящих 30 в состав блока 2 памяти. В очередном i-M цикле процессора (фиг.З) по импульсу ТИ1 в регистр 5 заносится новая информация. Под ее управлением (выход 15 устройства) 35 по импульсам ТИ1, ТИ2 и ТИЗ, образующим временную развертку одного цикла, производятся последовательные изменения состояния процессора в i-M цикле. По импульсу ТИ2 в регистр 40 3 адреса заносится адрес информации, котораядолжна обрабатьюаться в (i+ +1)-м цикле процессора, и начинается ее считьтание из соответствующей памяти. Содержимое старших разрядов 45 регистра 3 адреса, определяющее тип памяти, к которой производится обращение, поступает на адресные входы памяти 6. Содержимое памяти 6 для рассматриваемого примера приведено 50 в таблице. В случае, если считьшаемая информация находится в блоке 1 памяти, О с обоих выходов памяти 6 разре-, шают выработку очередной развертки 55 синхросигналов без задержки (короткий цикл) и, кроме Toroi поступают на вход управления мультиплексора 4. В мается в регистр 5, а по импульсу ТИ в регистр 3 адреса принимается адрес следующей информации для (i+2)-ro цикла процессора. Если следующая микрокоманда находится в одной из медленных памятей блока 2 памяти, то 1 с одного из выходов памяти 6 через элементы ИЛИ 13, И 11 по импульсу ТИЗ сбрасывает триггер 8 пуска в О. Вьфаботка оче редной развертки синхросигналов блокируется, а следовательно, запрещается изменение состояния процессора. 1 с выхода памяти 6 поступает на вход соответствующего элемента И 10 и разрешает прохождение через него импульса ТИЗ, который поступает на вход соответствующего элемента 9 задержки, и появляется на его выходе одновременно с появлением считываемой информации на выходе медленной блока 2 памяти. 1 с выхода одного из элементов 9 задержки проходит через элемент ИЛИ 12 и устанавливает триггер пуска в 1, которая обеспечивает запуск новой развертки синхросигналов. В следующем (1+2)-м цикле процессора информация (команда),считанная из соответствукяцей медленной памяти блока 2 памяти, заносится по импульсу ТИ1 в регистр 5. Таким образом, за счет создания переменных циклов обращения, учитывакицих быстродействие памятей, предлагаемое устройство обладает большим быстродействием по сравнению с прототипом .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения памяти с процессором | 1986 |

|

SU1377866A1 |

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для формирования широкополосного случайного процесса | 1986 |

|

SU1432514A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для сортировки информации | 1984 |

|

SU1196849A1 |

| Система для программного управления | 1985 |

|

SU1251033A1 |

| Устройство для ввода информации от датчиков | 1990 |

|

SU1691828A1 |

| Устройство для ввода информации | 1985 |

|

SU1282107A1 |

| Устройство для индикации | 1989 |

|

SU1649602A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПАМЯТИ С ПРОЦЕССОРОМ, содержащее выходной регистр, мультиплексор, первый и второй блоки памяти, регистр адреса, генератор тактовых импульсов и триггер пуска, причем выход выходного регистра является выходом устройства, информационный вход выходного регистра соединен с выходом мультиплексора, первый и второй информационные входы которого соединены соответственно с выходами первого и второго блоков памяти, адресный вход первого блока памяти соединен с выходом старших разрядов вегистра адреса и с первым адресным входом второго блока памяти, второй адресньй вход которого соединен с выходом младших разрядов регистра адреса, информационньй вход KOTopoto является входом устройства, первьй и второй выходы генератора тактовых импульсов соединены соответственно с входами записи-чтения выходного регистра и регистра адреса, выход триггера пуска соединен с входом запуска генератора тактовых импульсов, отличающееся тем, что, с целью повышения быстродействия, оно содержит память признаков обращения, группу элементов И, группу элементов задержки, первьй и второй элементы ИЛИ и элемент И, причем выход младших разрядов регистра адреса соединен с адресным входрм памяти признаков обращения, выход которой соединен с уп(Л равляющим входом мультиплексора, с входом первого элемента ИЛИ и с первыми входами элементов И группы, выходы которых через элементы задержки группы соединены с входами второго элемента ИЛИ, выход которого соединен с входом установки в единицу триггера i4iib пуска, вход установки в ноль котоN9 рого соединен с выходом элемента И, ЭО СО первый вход которого соединен с выходом первого элемента ШШ, третий эо выход генератора тактовых импульсов соединен с вторыми входами элементов И группы и элемента И.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сопряжения процессора с памятью | 1980 |

|

SU898437A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3859636, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1985-02-28—Публикация

1983-10-04—Подача