Изобретение относится к вычислительной технике, в частности к устройствам для сопряжения с памятью, и может быть использовано для построения- систем с быстродействующей памятью большой информационной емкости.

Цель изобретения - повьш1ение информационной, емкости устройства.

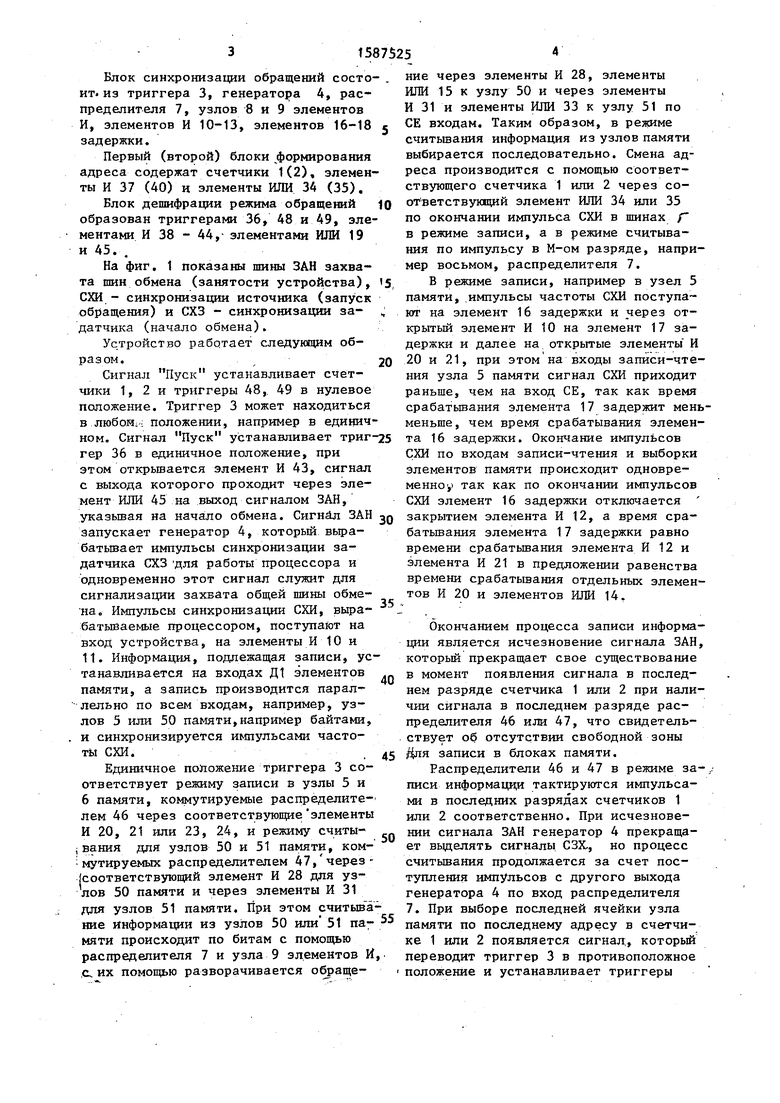

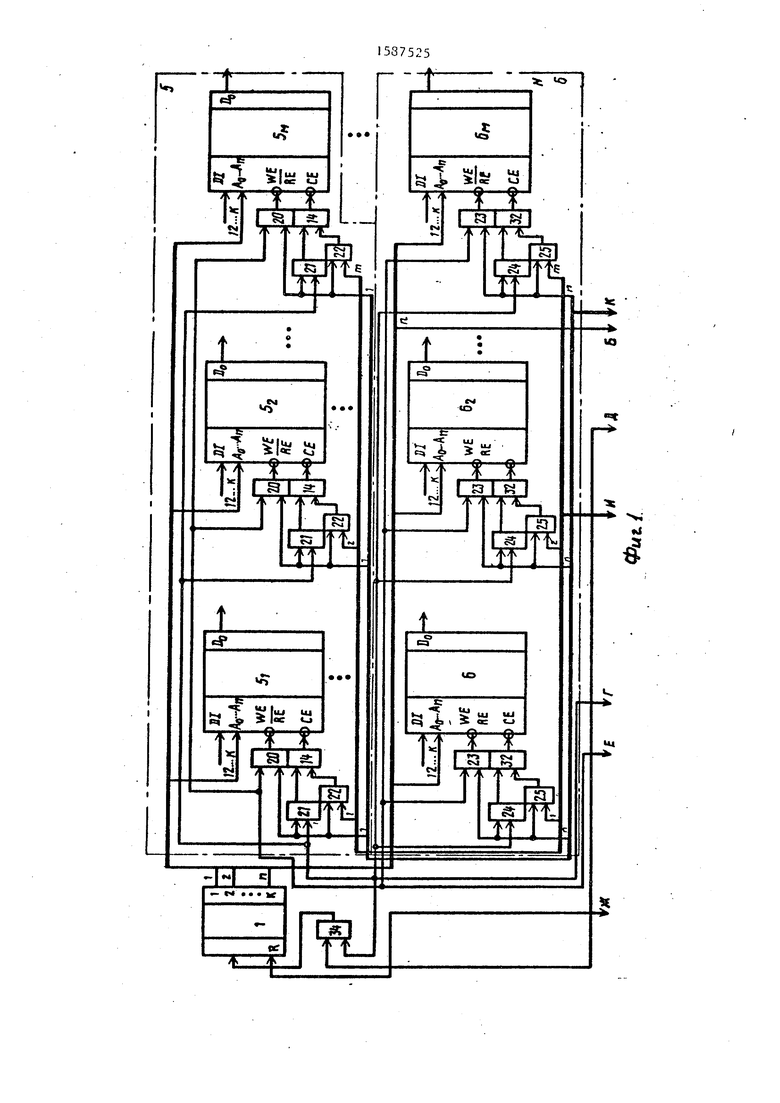

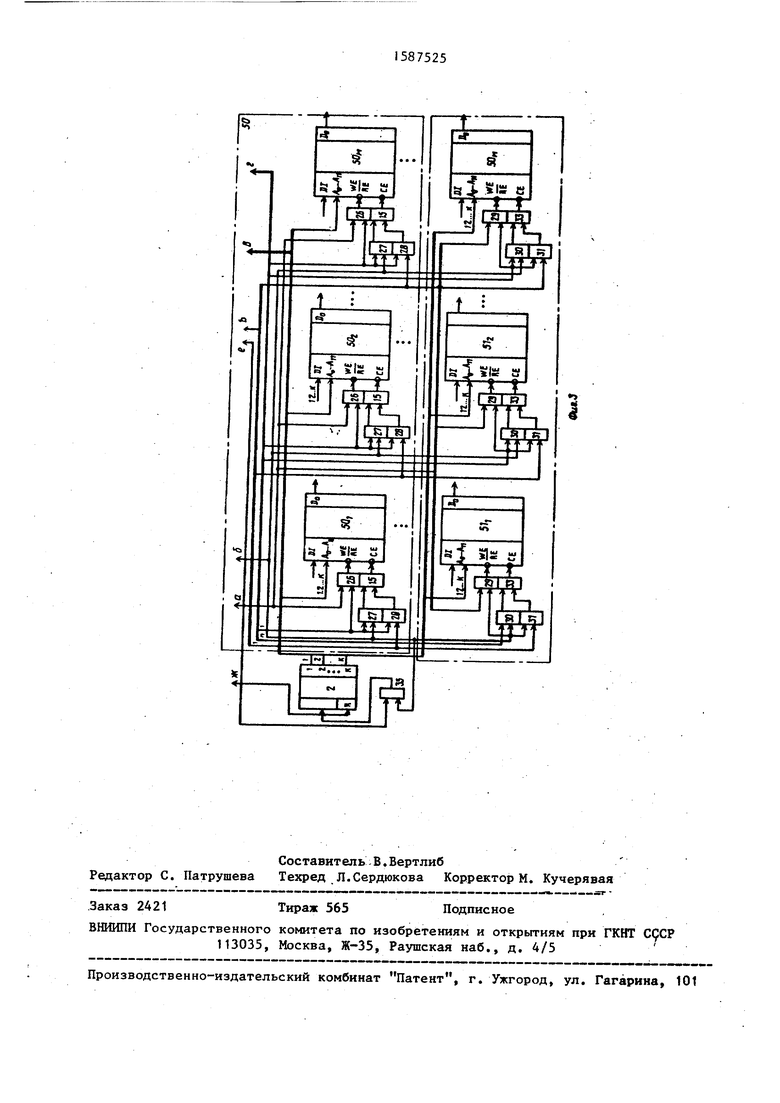

На фиг. 1 - 3 представлена функциональная схема устройства.

Устройство содержит счетчики 1 и 2 адреса, триггер 3 режима, генератор 4 импульсов,первый и N-й узлы 5 и 6 памяти первого блока памяти, первый распределитель 7 импульсов, уалы 8 и 9 элементов И, элементы И 10-13, группы элементов ИЛИ 14 и 15, элементы 16-18 задержки, элемент ИЛИ 19, группы элементов И 20-31, группы элементов

ИЛИ 32 и 33, элементы ИЛИ 34 и 33, триггер 36, элементы И 37-44, элемент. ИШ 45, второй и третий распределители импульсов 46 и 47, триггеры 48 и |49, первый и N-й узлы 50 и 51 памяти второго блока памяти.

Первый узел 5 (50) памяти первого (второго) блока памяти содержит М элементов 5,-5 (50,-50д) памяти, М коммутаторов, образованных элементами И 21 и 22 (27 и 28) и элементами ИЛИ 14 (15), и М элементов И 20 (26).

N-й узел 6 (51) памяти первого (второго) блока памяти содержит М элементов 6,-6 (51,-51м) памяти, М коммутаторов, образованных элементами И 24 и 25 (30 и 31) и элементами ИЛИ 32 (33), и М элементов И 23 (29),

Блок синхронизации обращений состо- ит. из триггера 3, генератора 4, распределителя 7, узлов 8 и 9 элементов И, элементов И 10-13, элементов 16-18 задержки.

Первый (второй) блоки формирования адреса содержат счетчики 1(2), элементы И 37 (40) и элементы ИЛИ 34 (35).

Блок дешифрации режима обращений образован триггерам 36, 48 и 49, элементами И 38 - 44,- элементами ИЛИ 19 и 45. .

На фиг. 1 показаны шины ЗАН захвата шин обмена (занятости устройства), СХИ - синхронизации источника (запуск обращения) и СХЗ - синхронизации за- датчика (начало обмена).

Устройство работает следующим образом.

Сигнал Пуск устанавливает счетчики 1, 2 и триггеры 48, 49 в нулевое положение. Триггер 3 может находиться в любом-; положении, например в единич

. j

5, ,

7525

ние через элементы И 28, элементы ИЛИ 15 к узлу 50 и через элементы И 31 и элементы ИЛИ 33 к узлу 51 по СЕ входам. Таким образом, в режиме считьшания информация из узлов памяти выбирается последовательно. Смена адреса производится с помощью соответствующего счетчика 1 или 2 через со- от ветствукщий элемент ИЛИ 34 или 35 по окончании импульса СХИ в щинах Г в режиме записи, а в режиме считывания по импульсу в М-ом разряде, например восьмом, распределителя 7.

В режиме записи, например в узел 5 памяти, импульсы частоты СХИ поступают на элемент 16 задержки и через открытый элемент И 10 на элемент 17 задержки и далее на открытые элементы И 20 и 21, при этом на входы записи-чтения узла 5 памяти сигнал СХИ приходит раньше, чем на вход СЕ, так как время срабатьюания элемента 17 задержит мень0

меньше, чем время срабатывания элемен

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1989 |

|

SU1742823A1 |

| Устройство для управления обменом процессора с памятью | 1988 |

|

SU1667087A1 |

| Устройство для сопряжения процессора с памятью | 1990 |

|

SU1798788A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Устройство для формирования сигнала идентификации начала команды ЭВМ | 1985 |

|

SU1352493A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения систем с быстродействующей памятью большой емкости. Цель изобретения - повышение информационной емкости устройства. Цель достигается введением в устройство, содержащее два блока формирования адреса, память и блок синхронизации обращений, включающий генератор импульсов, распределитель импульсов, триггер режима, два узла элементов И, четыре элемента И и три элемента задержки, блока дешифрации режима обращения. Использование изобретения позволяет увеличить информативность и емкость процесса обмена за счет коммутации блоков памяти в режиме записи и считывания, причем запись информации осуществляется байтами, а считывание - битами, т.е. в режиме считывания параллельный код преобразуется в последовательный. 2 з.п. ф-лы, 3 ил.

ном. Сигнал Пуск устанавливает триг-25 та 16 задержки. Окончание импульсов

гер 36 в единичное положение, при этом открьшавтся элемент И 43, сигнал с выхода которого проходит через элемент ИЛИ 45 на выход сигналом ЗАН,

указьшая на начало обмена. Сигнал ЗАН JQ закрытием элемента И 12, а время срабатьтания элемента 17 задержки равно времени срабатывания элемента И 12 и элемента И 21 в предложении равенства времени срабатывания отдельных элементов И 20 и элементов ИЛИ 14.

запускает генератор 4, который вырабатывает импульсы синхронизации за- датчика СХЗ для работы процессора и одновременно этот сигнал служит для сигнализации захвата общей шины обме- на. Импульсы синхронизации СХИ, вырабатываемые процессором, поступают на вход устройства, на элементы И 10 и 11. Информация, подлежащая записи, устанавливается на входах Д1 элементов памяти, а запись производится парал35

40

Окончанием процесса записи информации является исчезновение сигнала ЗАН, который прекращает свое существование в момент появления сигнала в последнем разряде счетчика 1 или 2 при наличии сигнала в последнем разряде распределителя 46 или 47, что свидетельствует об отсутствии свободной зоны Для записи в блоках памяти.

лельно по вce входам, например, узлов 5 или 50 памяти,например байтами, и синхронизируется импульсами частоты СХИ.

Единичное положение триггера 3 соответствует режиму записи в узлы 5 и 6 памяти, коммутируемые распределителем 46 через соответствующие элементы И 20, 21 или 23, 24, и режиму считы- iвания для узлов 50 и 51 памяти, ком- мутируемых распределителем 47, через- (соответствующий элемент И 28 для узлов 50 памяти и через элементы И 31 для узлов 51 памяти. При этом считывание информации из узлов 50 или 51 па- Мяти происходит по битам с помощью распределителя 7 и узла 9 элементов И .х их помощью разворачивается обраще-

СХИ по входам записи-чтения и выборки элементов памяти происходит одновременно) так как по окончании импульсов СХИ элемент 16 задержки отключается

0

5

5

0

Окончанием процесса записи информации является исчезновение сигнала ЗАН, который прекращает свое существование в момент появления сигнала в последнем разряде счетчика 1 или 2 при наличии сигнала в последнем разряде распределителя 46 или 47, что свидетельствует об отсутствии свободной зоны Для записи в блоках памяти.

Распределители 46 и 47 в режиме за-,.- писи информации тактируются импульсами в последних разрядах счетчиков 1 или 2 соответственно. При исчезновении сигнала ЗАН генератор 4 прекращает вьщелять сигналы СЗХ., но процесс считывания продолжается за счет поступления импульсов с другого выхода генератора 4 по вход распределителя 7. При выборе последней ячейки узла памяти по последнему адресу в счетчике 1 или 2 появляется сигнад, который переводит триггер 3 в противоположное положение и устанавливает триггеры

5Г587525

8 и 49 в исходное положение, при этом станавливается сигнал ЗАН запроса бщей айны, а считьгоание произвоится из другого блока памяти.

к вы т н ю кл 10 д с и и г ра к 1ж г си от вы со во ад ци жи ма от ус 30 к го ро пе с эл ще си си

Ф

ормула изобретения

15

20

25

ка синхронизации обращений, группы выходов второго и третьего )аспредеЛи- телей импульсов являются соответственно первой и второй группами стробиру- ющих память выходов устройства и подключены к первому и. второму разрещаю- щим входам блока дешифрации режима обращений, первый и второй тактовые вхо- 10 ды которого соединены соответственно с вторыми тактовыми входами, первого- и второго блока формирования адреса и нулевым и единичным выходами триггера режима блока синхронизации обращений, счетным входом подключенного к второму вьпсоду блока дешифрации ре- 1жима обращений, группы выходов первого и второго узлов элементов И блока синхронизации обращений являются соответственно первой и второй группами выходов выборки памяти устройства и-. соединены с разрешающими входами первого и второго блоков формирования адреса и третьим и четвертым информационными входами блока дешифраций режима обращений, пятый и шестой информационные входы которого являются соответственно входом пуска и сброса. устройства, а второй выход подключен 30 к установочным входам первогб и второго блоков формирования адреса, второй выход генератора импульсов и вход первого элемента задержки, соединенный с вторыми входами первого и второго элементов И блока синхронизации обращений, являются соответственно выходом сигнала занятости устройства и входом сигнала запуска обращения устройства.

первого элемента ИЛИ, третий вход ко- торого соединен с пятым информационным входом блока и установочным входом первого триггера, вход сброса ко- 0 торого является шестым информационным входом блока, первые и вторые входы первого и третего элементов И соединены соответственно с первым и третьим информащюнными входами блока, первые 5 и вторые входы второго и четвертого элементов И соединены соответственно с вторым и четвертым информационными входами блока, третьи входы первого и второго элементов И являюtcя

0

ветственно первым и вторым разрешаю щими входами блока, четвертые входы первого и второго элементов И являются соответственно первым и вторым так товыми входами блока и соединены с первыми входами шестого и пятого элементов И вторые входы которых соеди- |нены с выходом первого триггера, а выходы - соответственно с первым и вторым входами второго элемента ИЛИ, выход которого является первым выходом блока, третьи входы пятого и шестого элементов И соединены роответст- венно с выходами второго и третьего триггеров, счетные входы которых соединены соответственно с выходами третьего и четвертого элементов И, а установочные входы - с выходом первого элемента ИЛИ и вторым выходом блока.

Составитель В.Вертлиб Редактор С. Патрушева Техред Л.Сердюкова Корректор М. Кучерявая

Заказ 2421

Тираж 565

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СрСР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Устройство буферной памяти | 1987 |

|

SU1418723A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1488816, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-23—Публикация

1988-10-04—Подача