(54) УСТРОЙСТВО ДЛЯ ПОТЕНЦИРОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для логарифмирования двоичных чисел | 1972 |

|

SU448459A1 |

| Устройство для вычисления функции @ = @ | 1982 |

|

SU1034033A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Устройство для потенцирования | 1990 |

|

SU1815635A1 |

| Конвейерное устройство для вычисления гиперболических функций | 1981 |

|

SU1026141A1 |

| Конвейерное устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1003080A1 |

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

| Устройство для вычисления математического ожидания | 1986 |

|

SU1322315A1 |

| Устройство для потенцирования массивов двоичных чисел | 1982 |

|

SU1043646A1 |

: . .

-Иаобретение относится к области вычислительной техники и может быть использовано для вычисления антилогарифмических зависимостей (проведение операции потен/дирОВвн Гя) в цвоичной системе счислении.

Известио устройство для потенцирования, содержащее регистр сдвига, .счетчик, элемент ИЛИ, три элемента И, два триг гера, элемент задержки и генератор тактоы Гз1 импульсов jlj..

Недостатком устройства является низкая точность вычисления.

Наиболее близким техническим решением к нзобретеншоявляется устройство для . потенцирования, содержащее два регистра блок сравнения и триггер 2.

Недостатком устройства является низкая точность вычислений с погрешностью ПО 8,5%, что не всегда приемлемо при решении ряда задач.

Целью изобретения является повышение точности работы устройства.

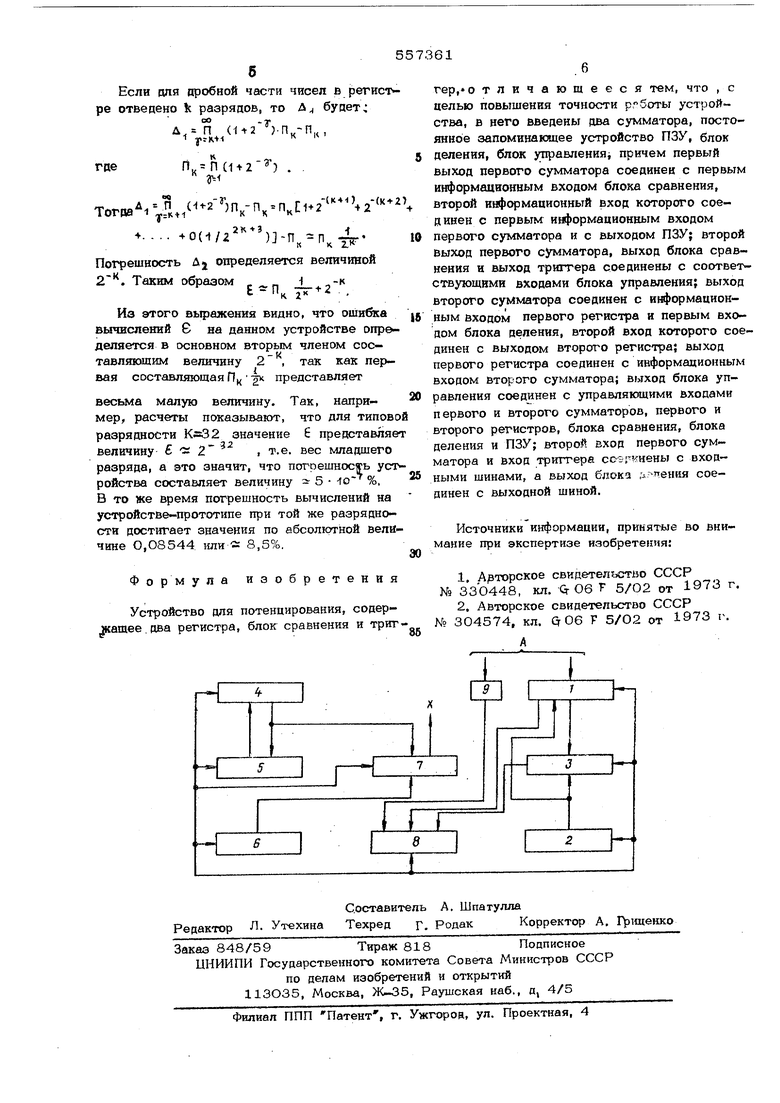

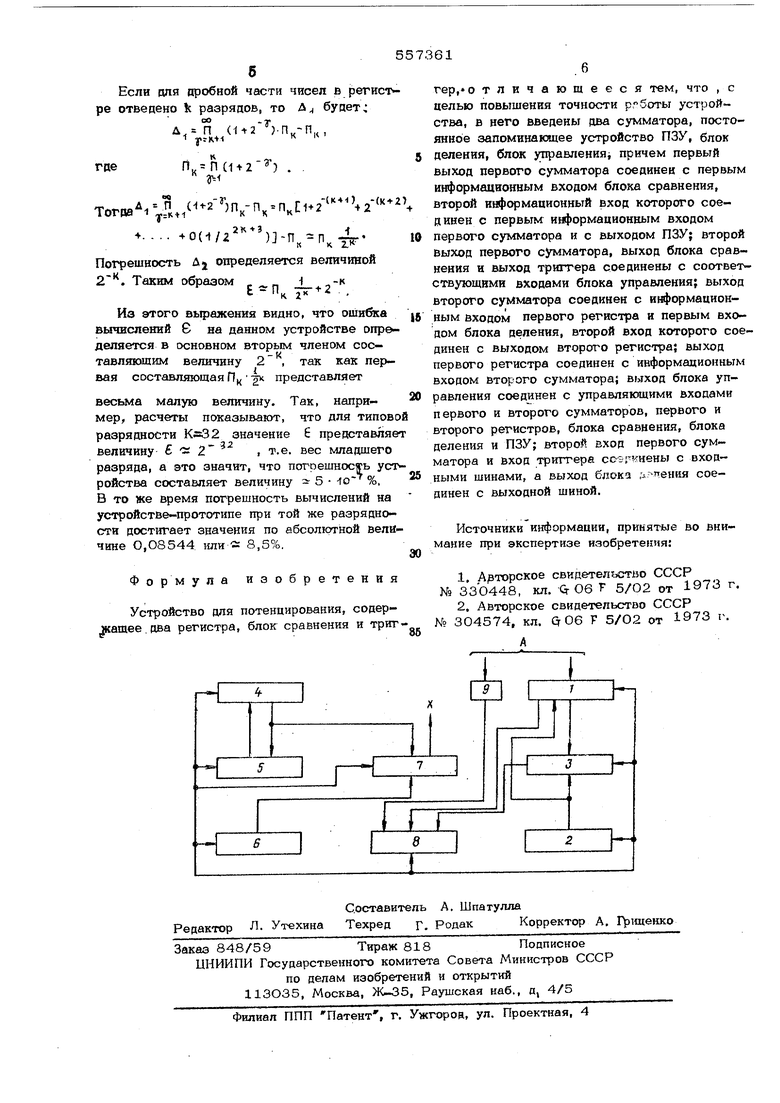

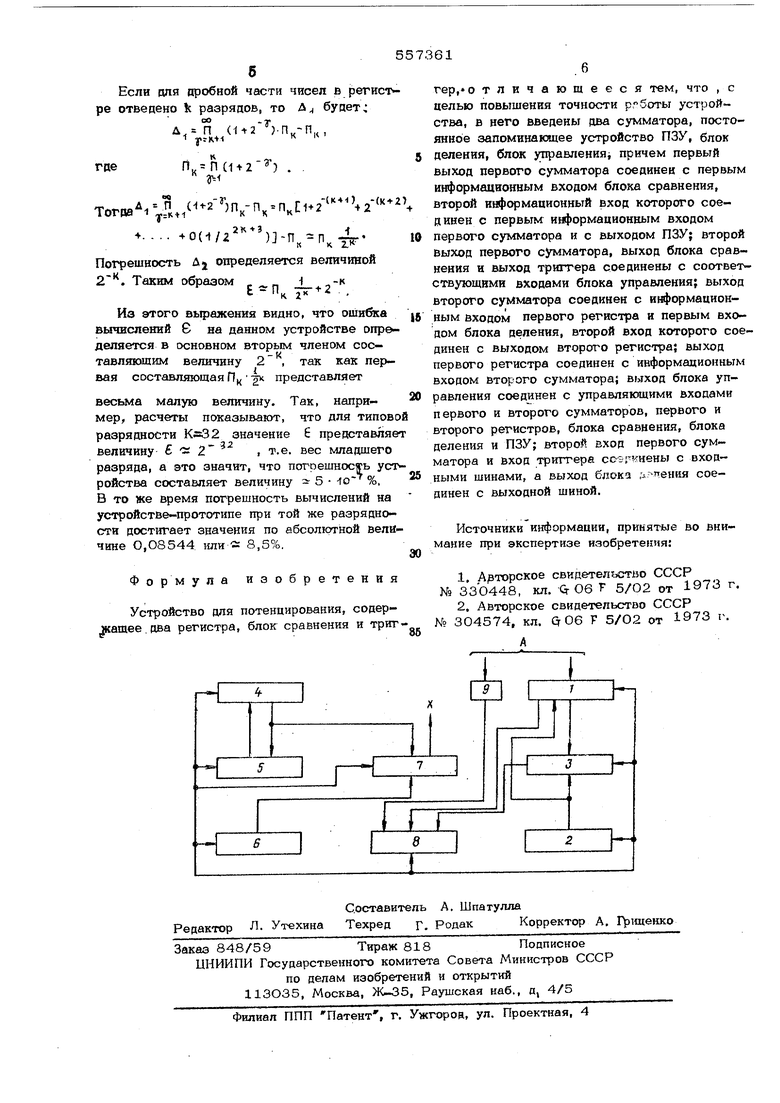

Эта цель достигается за счет того, что в предложенное устройство введены допол1|1Ительно два сумматора, постоянное запоминающее устройство (ПЗУ), блок деления и блок управления. Первый выход первого сумматора соединен с первым информацион ным входом блока сравнения, второй информационный вход которого соединен с первым информационным входом первого сумматора и с выходом ПЗУ. Второй выход первого сумматора, выход блока сравнения и выход триггера соединены с соответствук шими входами блока управления. Вход второго сумматора соединен с информационным входом первого регистра и первым входом блока деления, второй вход которого соединен с выходом второго регистра. Выход

первого регистра соединен с информационным входом второго сумматора. Выход блока управления соединен с управляющими входами первого и второго сумматоров, первого и второго регистров, блока сравнения,

блока деления и ПЗУ. Второй вход первого сумматора и вход триггера соединены с входными шинами, а выход блока деления с выходной шиной.

На чертеже представлена блок-схема

устройства для потенцирования. Устройство содержит первый сумматор f ПЗУ 2, блок сравнения 3, второй сумматор 4, первый 5 и второй 6 регистры, блок целения 7, блок управления 8 и триггер 9, Устройство работает следующим образом. В Исходном СОСТОЯНИЙ все разряды всех регистров, сумматоров н триггера находят- ей в нулевом состоянии. Значение .исход ного числа А, которое в общем случае представляет величину Cogr, и которое необходимо преобразовать по антилогарвф- мической зависимости, заносится в сумматор 1, а его знак - в триггер знака 9. В сумматор 4 вводится величина 1,1(2) {1ц-2-j), где f 1, а в 6 заносится едишэда. Затем из разрядов сумматора 1, отведенных рля целой части значе«; нкя А, если значение целой части не равно нулю, аычитается единица на каждом такте до получения нулевого значения в этой части сумматора 1, Одновременно с этой операцией сннхротю в регистре 6 производится сдвиг единицы влево. Причем при выполнении этих операций должно вы полняться следующее условие: при положительном исходном числе в регистре 6 кроме указанных сдвигов производится еще один дополннг-ельный в ту же сторону, а соцержкмое цробной части сумматора 1 нреобразуется в вополнителышй код, при отрицательном заданном числе дополнитель ный сдвиг в регистре 6 не производится, а содержимое сумматора 1 остается в прямом коде. Во время перечисленных операций состояние сумматора 4 и тригг.ера 9 не изменяется. Затем содержимое сумматора 1 сравнивается со значением константы d. , которая выб1фается из ПЗУ с помощью блока управления 8 и подается на вход блока сравнения 3. Обьем ПЗУ определяется числом к хранящихся в нем констант -, где k - дисло разрядов разрядной сетки уст ройства, предназначенных для представлеНИН дробной части чисел. Если константа больше значения содержимого сумматор 1, т.е. О, то производится сдвиг еди4 ниды дробной части сумматора 4 вправо Hd один разряд, а состояние регистров 5 и 6 йе изменяется. Затем сравнивается содержимое сумматора 1 с очередным значением константы и если Oi то как и на предыдущем шаге единицы сумматора 4 сдвигаете на один разряд вправо без изменения сост ния регистров 5 и 6. Операции сравнения содержимого сумма тора 1 с очередными значениями о(.|-с соот етствующими последующими опе{ адиями роводятся до тех пор, пока результат сравения каждый раз дает нулевое значение ператора . В том случае, когда результат операции равнения равен единице ( ), что оответствует тому, что значение ot том шаге меньше содержимого сумматора 3. двиг на сумматоре 4 не производится; а го значение дополнительно записывается в регистр 5. Затем из содержимого сумматора 1 вычитается значение d-n по которому в этом проводилось сравнение, путем подачи с выхода ПЗУ 2 на вход сум- . матора. Далее полученное значение в сумматоре 1 сравнивается с очередным значением конс танты с.™,.Если результат сравнения равен нулю, то содержимое всех регистров и сумматоров не изменяется. Если же на каком-то шаге результат сравнения равен единице (1)., то из содержимого сумматора 1 вычитается сравниваемое значение константы сА, причем содержимое сумматора 4 и регистра 6 не меняется, а содержимое регистра 5 сдвигается вправо в сторону младших разрядов, по числу проведенных операций сравнения, которое фиксирует блок 8 управления. Эти процедуры повторяются до тех пор, пока не будет проведено k сравнений, где k - разрядность дробной части чисел, с которыми оперирует устройство. Если в сумматоре 1 на каком-либо шаге появится значение, равное нулю, то проведение операций сравнения прекращается. В результате проведенных процедур в сумматоре 4 находится делитель, а в регистре 6 - делимое. Делимое и делитель подаются на блок 7 деления, с выхода которого получаем исходный результат (частное) х т.е. результат операции .потенцирования. Среднее время вычисления антилогариф ма наибольшего исходного числа, которое можно записать в сумматор 1, составляет порядка сотни тактов. В то же время решение аналогичной задачи на универсальной ЦВМ с использованием библиотеки стандарт ных программ необходимо около 2000 тактов. Таким образом, быстродействие предлагаемого устройства повышено по сравнению с известными. Погрешность при потенцировании состоит из основных Погрешностей: погрешности вычисления бесконечного произведения Д и погрешности, связанной с ограничением разрядной сетки регистров при выполнении вычислений - Д - Д.

Авторы

Даты

1977-05-05—Публикация

1974-08-27—Подача