(54) НАКАПЛИВАЮЩИЙ СУММАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| Накапливающий сумматор | 1991 |

|

SU1800454A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР | 1972 |

|

SU342186A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО | 1973 |

|

SU362295A1 |

| Параллельный накапливающий сумматор | 1978 |

|

SU744568A2 |

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| Накапливающий сумматор с запоминанием переноса | 1978 |

|

SU943710A1 |

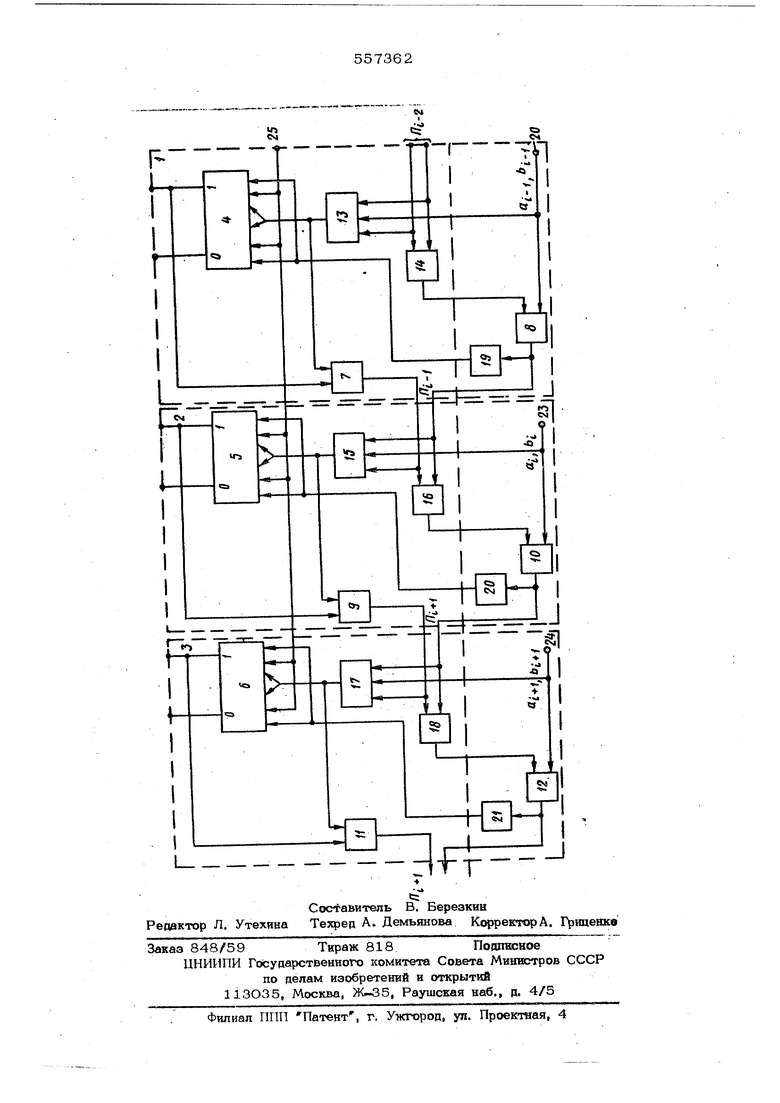

Изобретение относится к области цифровой вычислительной техники. Известны накапливающие сумматоры па раллельного действия, содержащие в каждом разряде элементы И и ИЛИ и счетный триггер, и, рассчитанные на параллельный ввод разрядов слагаемых. Слагаемые при этом вводятся в сумматор последовательно во времени. В этих случаях при образовании переноса на счетный вход триггера ( разряда сумматора) одновременно могут придти перенос и второе слагаемое. Для исключения этого сигнал переноса, воЗ никающий в этом случае при суммировании в существующих схемах искусственна, задерживается и лишь потом поступает йа счетный вход триггера l. Известны также сумматоры, в которых для управления переносом использованы шины гашения .переноса, распространение прямого и обратйого значения сигнала переноса. При этом для формирования переноса использованы вентили, инверторы, схемы сборки и совпадения, установленньге на входе схемы формирования сигнала переноса 2J. Накостатком таких устройств является услойсненке входной логики схем формирования переноса, что вносит дополнительную задержку в aeira переноса и как следствие, ухудшает временные характеристики сумматора. Наиболее близким техническим решением к изобретению является накапливающий сумматор; содержащий в каждом разряде счетный триггер, элементы И и ИЛИ. вход счетного трвгггера соединен с выходом первого элемента ИЛИ, первый вход которого соединен со входом соответствующего разряда слагаемого и первым входом первого элемента И. Второй вход первого элемента ИЛИ подключен к выходу переноса из предыдущего разряда сумматс а. Единичный выход счетного триггера, соединен с первым входом второго элемента И, выход которого соединен с выходом переноса из данного разряда сумматора з. Такой сумматор содержит в каждом разряде элемент задержки, что усложняет кснструхкию сумматора и ухудшает его надежность.. Цель изобретения - повышенке надежности и утфощение сумматоров. Для достижения этой цели каждый разряд сумматора дополнительно содержит элемент НЕ и второй элемент ИЛИ, входы которого подключены к выходам переноса из предыдущего разряда сумматора, а вы- ход ко второму входу первого элемента И, выход которого подключен к другому выходу переноса из данного разряда сумматора и через ©лемент НЕ к первому разрешаюraeijiy входу счетного триггера, втфой раз р иашший вход которого соединен с шиной разрешении сложения. Третий вход первого элемевта ИЛИ соединен с другим выходом переноса игз прэдн.уЩетаз разряда су1- 1мато ра. Зыуод аервот о елемси-.га ИЛИ подключен ко второму вхгэду второго элемента И, На sepTevite приаецепз функциональная схзма трех рязрядоа накапливающего сумтуш тора, № обозначены 1.-3 - разряды накаштйваюшего сумматора, 4.6 - счетные триггеры, 7-12 « элементы И, 13-18 елементы ИЛИ, влементы НЕ, 22, 23,24 - входы соответст&ующих разрядов слагаемого и 25 шина разрешения, слонсе- кия. Рассмотри.- i paapsa cjrivnviaTOpa (2 Он ссядержггт с-н мч1;ьг|{ трцгч-ер 5, единичный выход которого соедг.неп со В5еодом элемен та И 8, вход Ko-ropoixs; иодключен к выходу элемента ИЛИ 15, шэагагюченный к - ютлому TpHi-s epa 5, Первый и второй Еходь; злемектов ИЛИ 3.5 и 16 поцклю чекы ко входам переноса из предыдущего ( -i - 1) то разряда, Трет-нй вход элемента Или 15 подключен ко ахозду 23 соо в&гствующаго i гЪ разряр а слагаемого, который :а.одкпючен ко входу элемента И 10 Др;|;Той BXOR последнего соз да-иен с выходом элемента ИЛИ 16, Выхои элемента И 10 через элемент НЕ 20 Нодключен к разрешающему входу триггера 5, щзугой разрешающий вход которого соецинен с шиной разрешения сложенг1я 2.5, Выходы элементов И 9 li 10 являются выходами переноса в последуйщий: ( i -fl) й разряд сум . матора В качестве счетного триггера монет бы {5спопьзована универсальная триггерная схе ма, имеющая один счетный вход и два разрешающих входа (например, J К.триг5 ер), Слагаемые а и в поступают по входам. 22-24 последовательно, одно за другим. При этом слокение первого и второго слагаемых ос: пцествляется при подаче сигнала на шику 2.5 . Промежуточный т й разряд сумматора работает спе.гхуюшкм образом. Допустим, что на вход разряда 2 постуают слагаемые, имеющие следующие значеия:первое слагаемое О,- 1, второе слагамое Ъ- -1, Ввод слагаемых осуществляется через лемент ИЛИ 15, Слагаемые поступают а счетный вход триггера 5 и на однн из ходов элемента И. При этом с единичного ыхода триггера 5 на элемент И 9 постуает сигнал разрешение переноса. Вслед а первым второе слагаемое также постуает на счетный вход триггера 5 и на элеент И 9. В результате совпадения двух сигналов на выходе элемента И 9 образуется сигнал нереноса, распространяюшийся по цепя сквозного переноса в сторону старших разрядов. После прихода импульса по шине 25 значение суммы появляется яа выходе ного разряда. При этом запирающий сигнал с его счетного выхода поступает на один из входов элемента И 9. Если со стороны предыдущего ( i - 1) -го разряда 1 сигнал переноса (по одной из шин переноса или по двум шинам одновременно не поступал, то на выходе элемента И 9 будет запрещающий потенциал, который передается по одной из шин переноса { .Л, ) в старший ( +1) й разряд 3 и на элемент НЕ 20. Запрещающий потенциал на выходе элемента НЕ 20 инвертируется, и в виде разрешающего потенциала подается на разрешающий вход триггера 5 данного т -гр разряда. За вторым слагаемым следует импульс по шине 25, Но окончании импульса по шине 25 информация на выходе данного счетного разряда 3, Если со стороны предыду1дего ( i -1)Го разряда 1 поступил сигнал переноса (по одной из шин или по двум шинам одновременно), то этот сигнал, пройдя элементы ИЛИ 16 и И 10, формирует на выходе элемента И 1О разрешающий потенциал, который является сигналом переноса для следующего ( i +1)-го разряда 3, Кроме того, разрешающий потенциал с выхода элемента И 10 поступает на элемент НЕ 2О и инвертируется, В резуль-тате сформированный запрещающий потенциал с выхода элемента НЕ 2О поступает на разрешающий вход триггера 5 данного 1 -го разряда 2, Следующий за вторым слагаемым импульс по шине 25 не меняет состояния триггера 5 данного т -го разряда 2, Это состояние триггера 5 остается неизменным, как для случая С|:, О, так и для случая O(.j 1. В обоих случаях на выходе триггера о получают значение суммы.

Все другие разряды сумматора работают аналогично,

Исключение из всех разрядов накапливающего сумматора элементов задержки позволяет повысить надежность сумматора в целом, так как надежность этих элементов значительно ниже, чем надежность всех остальных элементов сумматора (например, выполненных в интегральном исполнении), и упростить его структуру.

Формула изобретения

Накапливающий сумматор, содержащий в каждом разряде счетный триггер, элементы И и ИЛИ, причем, счетный вход счетного триггера соединен с выходом первого элемента ИЛИ, первый вход которого соединен со входом соответствующего разряда слагаемого и первым входом первого элемента И, второй вход первого элемента ИЛИ подключен к выходу переноса из предыдущего разряда сумматора, единичный выход счетного триггера соединен с первым входом второго элемента. И, выход которого соединен с выходом переноса из данного разряда сумматора, отличающийся тем, что.

с целью повышения надежности и ущюшени сумматора, каждый разряд его дополнител но содержит элемент НЕ и второй элсмс 1т ИЛИ, входы которого подключены к выходам переноса из предыдущего разряда сумматора, а выход - ко второму входу первого элемента И, выход которого подключен к другому выходу переноса из данного разряда сумматора и через элемент НЕ к первому разрешающему входу счетного триггера, второй разрешающий вход которого соединен с шиной разрешения сложения; третий вход первого элемента ИЛИ соединен с другим выходом переноса иапредыдущего разряда сумматора; выход первого элемента ИЛИ подключен ко второму входу второго элемента И.

Источники информадии. принятые во внимание прИ экспертизе:

1,Папернов А. А, Логические основы ЦВТ. М.,Сов.радио„ 1972 п, с. 150,

2,Гаврилова Ю, В, и др, Арифметические устройства быстродействующих ЭЦВМ , М./Сов,радио , 1970 г., с. 5461.

3,Авторское свидетел:;С-тво СССР № 256367, кл, аОб Т 7/5Г 1968 г, (прототип).

Авторы

Даты

1977-05-05—Публикация

1976-01-04—Подача