1

Изобретение относится к цифровой вычислительной технике, может быть использовано для построения арифметических устройств и является усовершенствованием изобретения по авт. св. № 581470.

В основном изобретении по авт. св. № 581470 описан параллельный накапливающий сумматор, содержащий в каждом разряде триггер, элемент И и элемент ИЛИ, причем первые входы элементов И всех разрядов сумматора подключены к входам разрядов числа, выходы элементов И каждого разряда - к первому входу элементов ИЛИ соответствующего разряда сумматора, выходы которых подсоединены к счетным входам триггеров того же разряда, вторые входы элементов И четных разрядов сумматора подключены к шине управления, а единичный .выход триггера каждого разряда сумматора - к второму входу элемента ИЛИ последующего разряда сумматора, кроме того, сумматор содержит элемент задержки, вход которого подключен к щине управления, а выход - к вторым входамэлементов И нечетных разрядов сумматора 1.

Недостатком такого сумматора является невозможность выполнения операции сдвига.

Цель изобретения - расширение функциональных возможностей сумматора, заключающееся в возможности выполнения операции сдвига.

5 Для достижения поставленной цели в каждый разряд сумматора введен дополнительный элемент И, а в каждый нечетный разряд сумматора - элемент задержки, причем входы дополнительного элемента И

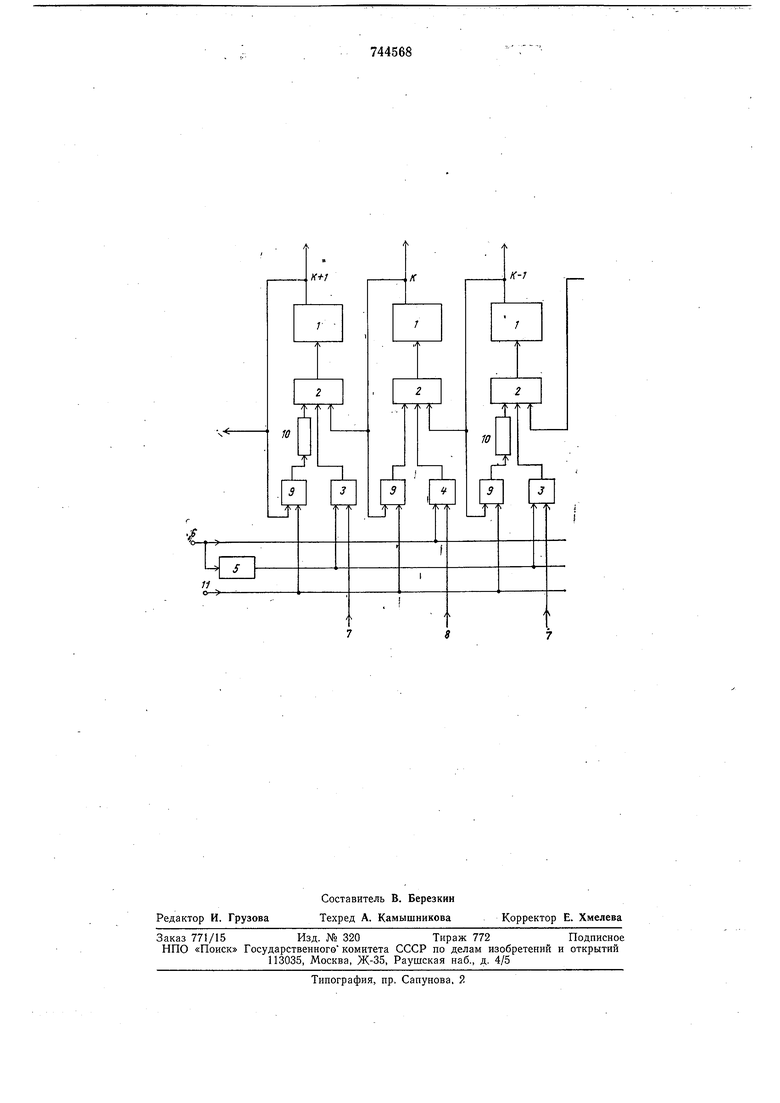

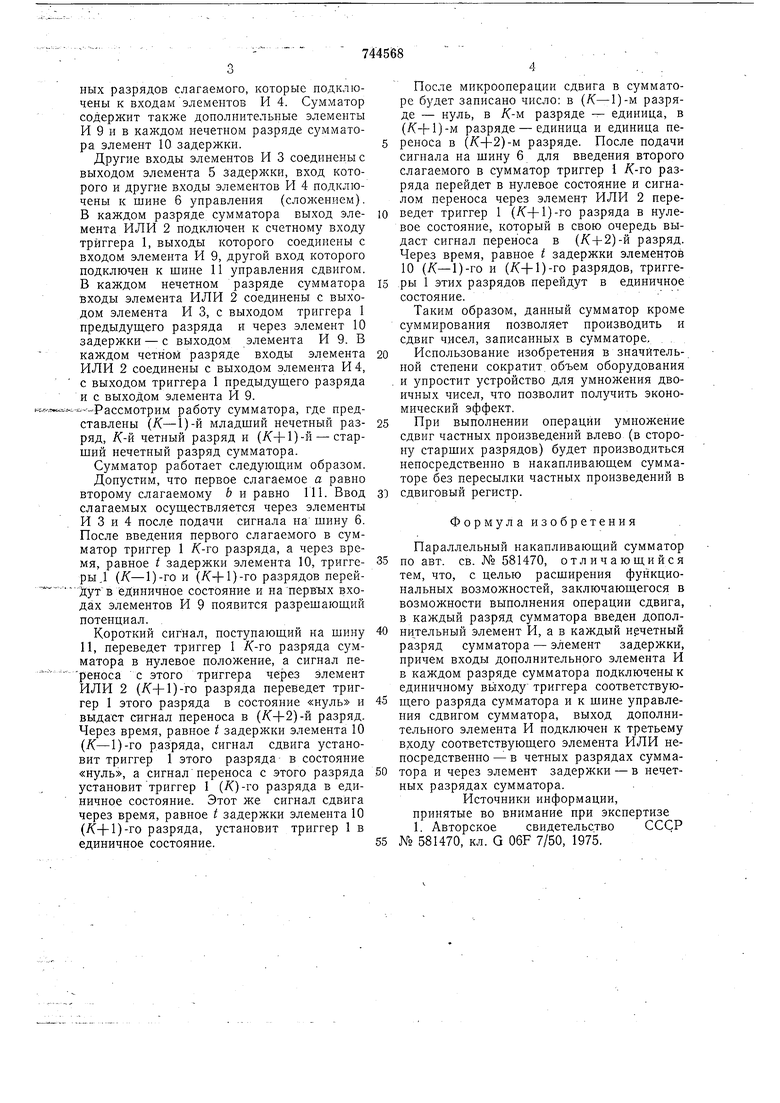

10 в каждом разряде сумматора подключены к единичному выходу триггера соответствуйщего разряда сумматора и к шипе управления сдвигом сумматора, выход дополнитёльного элемента И - к третьему входу соот15 ветствующего элемента ИЛИ непосредственно- в четных разрядах сумматора и через элемент задержки - в нечетных разрядах сумматора. На чертеже представлена функциональ20 ная- схема трех разрядов ((К-1)-го /С-го, (/С+1)-го) сумматора.

Сумматор содержит триггеры 1, элементы ИЛИ 2, элементы И нечетных 3 и чет ных 4 разрядов сумматора, элемент 5 задержки, шину 6 управления (сложением), входы 7 разрядов числа, служащие для ввода нечетных разрядов слагаемого, которые подключены к входам элементов И 3, входы 8 разрядов числа, служащие для ввода четных разрядов слагаемого, которые подключены к входам элементов И 4. Сумматор содержит также дополнительные элементы И 9 и в каждом нечетном разряде сумматора элемент 10 задержки.5

Другие входы элементов И 3 соединены с выходом элемента 5 задержки, вход которого и другие входы элементов И 4 подключены к шине 6 управления (слол ением). В каждом разряде сумматора выход эле- ю мента ИЛИ 2 подключен к счетному входу триггера 1, выходы которого соединены с входом элемента И 9, другой вход которого подключен к шине 11 управления сдвигом. В каждом нечетном разряде сумматора 15 входы элемента ИЛИ 2 соединены с выходом элемента И 3, с выходом триггера 1 предыдущего разряда и через элемент 10 задержки - с выходом элемента И 9. В каждом четном разряде входы элемента 20 ИЛИ 2 соединены с выходом элемента И 4, с выходом триггера 1 предыдуш,его разряда и с выходом элемента И 9. -Рассмотрим работу сумматора, где представлены (К-1)-й младший нечетный раз- 25 ряд, К-й четный разряд и (/СН-1)-й - старший нечетный разряд сумматора.

Сумматор работает следующим образом.

Допустим, что первое слагаемое а равно второму слагаемому b и равно 111. Ввод 31 слагаемых осуществляется через элементы И 3 и 4 после подачи сигнала на шину 6. После введения первого слагаемого в сумматор триггер 1 К-го разряда, а через время, равное / задержки элемента 10, тригге- 35 ры.1 (К-1)-го и (/С+1)-го разрядов перейЙутв единичное состояние и напервых входах элементов И 9 появится разрешающий потенциал. .

Короткий сигнал, поступающий на щину 40 11, переведет триггер 1 К-го разряда сумматора в нулевое положение, а сигнал переноса с этого триггера через элемент ИЛИ 2 (/С+1)-го разряда переведет трнггер 1 этого разряда в состояние «нуль и 45 выдаст сигнал переноса в (/С+2)-й разряд. ерез время, равное t задержки элемента 10 (К-1)-го разряда, сигнал сдвига устаноит триггер 1 этого разряда в состояние нуль, а сигнал переноса с этого разряда .50 становит триггер 1 (.)-го разряда в едиичное состояние. Этот же сигнал сдвига ерез время, равное t задержки элемента 10 (/С+1)-го разряда, установит триггер 1 в диничное состояние.55

После микрооперации сдвига в сумматоре будет записано число: в (К-1)-м разряде - нуль, в /С-м разряде - единица, в (К+1)-и разряде - единица и единица переноса в (/С+2)-м разряде. После подачи сигнала на шину 6 для введения второго слагаемого в сумматор триггер 1 К-то разряда перейдет в нулевое состояние и сигналом переноса через элемент ИЛИ 2 переведет триггер 1 (/С+1)-го разряда в нулевое состояние, который в свою очередь выдаст сигнал переноса в (/С+2)-й разряд. Через время, равное t задержки элементов 10 (К-1)-го и (/С+1)-го разрядов, тригге,ры 1 этих разрядов перейдут в единичное состояние.- Таким образом, данный сумматор кроме суммирования позволяет производить и сдвиг чисел, записанных в сумматоре, . .

Использование изобретения в значительной степени сократит объем оборудования и упростит устройство для умножения двоичных чисел, что позволит получить экономический эффект.

При выполнении онерации умножение сдвиг частных произведений влево (в сторону старших разрядов) будет производиться непосредственно в накапливающем сумматоре без пересылки частных произведений в сдвиговый регистр.

Формула изобретения

Параллельный накапливающий сумматор по авт. св. № 581470, отличающийся тем, что, с целью расширения функциональных возможностей, заключающегося в возможности выполнения операции сдвига, Б каждый разряд сумматора введен дополниJeльный элемент И, а в каждый нечетный разряд сумматора - элемент задержки, причем входы дополнительного элемента И в каждом разряде сумматора подключены к единичному вь1ходу триггера соответствующего разряда сумматора и к шине управления сдвигом сумматора, выход дополнительного элемента И подключен к третьему входу соответствующего элемента ИЛИ непосредственно - в четных разрядах сумматора и через элемент задержки - в нечетных разрядах сумматора.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 581470, кл. G 06F 7/50, 1975,

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный накапливающий сумматор | 1986 |

|

SU1399726A1 |

| Параллельный накапливающий сумматор | 1975 |

|

SU581470A1 |

| Вычислительное устройство | 1985 |

|

SU1269124A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2278411C1 |

| Параллельный накапливающий сумматор | 1979 |

|

SU813416A2 |

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| Накапливающий сумматор кодов Фибоначчи | 1990 |

|

SU1716523A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

Авторы

Даты

1980-06-30—Публикация

1978-05-26—Подача