Изобретение относится к области автоматики и вычислительной техники и предназначено для суммирования двоичных чисел.

Известны параллельные сумматоры, содержащие в каждом разряде элементы «И и «ИЛИ и счетный триггер, который, при реализации на потенциальных логических элементах, содержит два триггера с раздельными входами и четыре элемента «И.

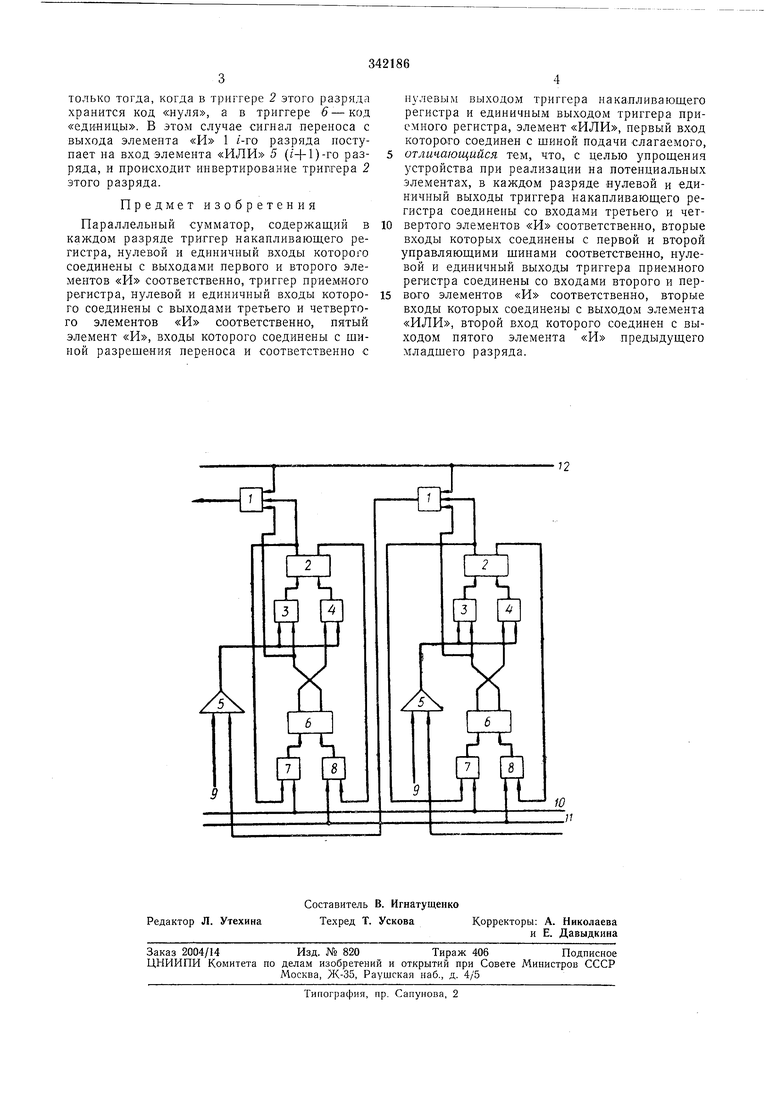

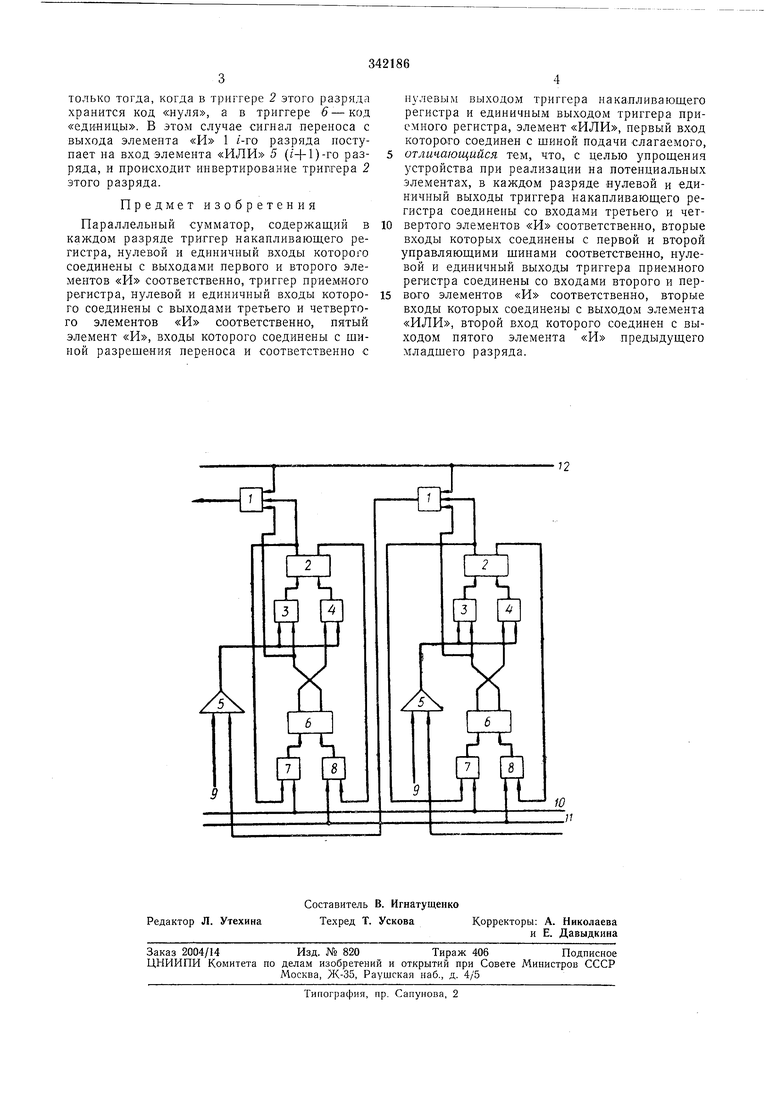

Предложенное устройство отличается тем, что в каждом разряде нулевой и единичный выходы триггера накапливающего регистра соединены со входами третьего и четвертого элементов «И соответственно, вторые входы которых соединены соответственно с первой и второй управляющими шинами. Нулевой и единичный выходы триггера приемного регистра соединены со входами второго и первого элементов «И соответственно, вторые входы которых соединены с выходом элемента «ИЛИ. Второй вход последнего соединен с выходом пятого элемента «И предыдущего младшего разряда.

Это позволяет упростить схему устройства при реализации на потенциальных элементах.

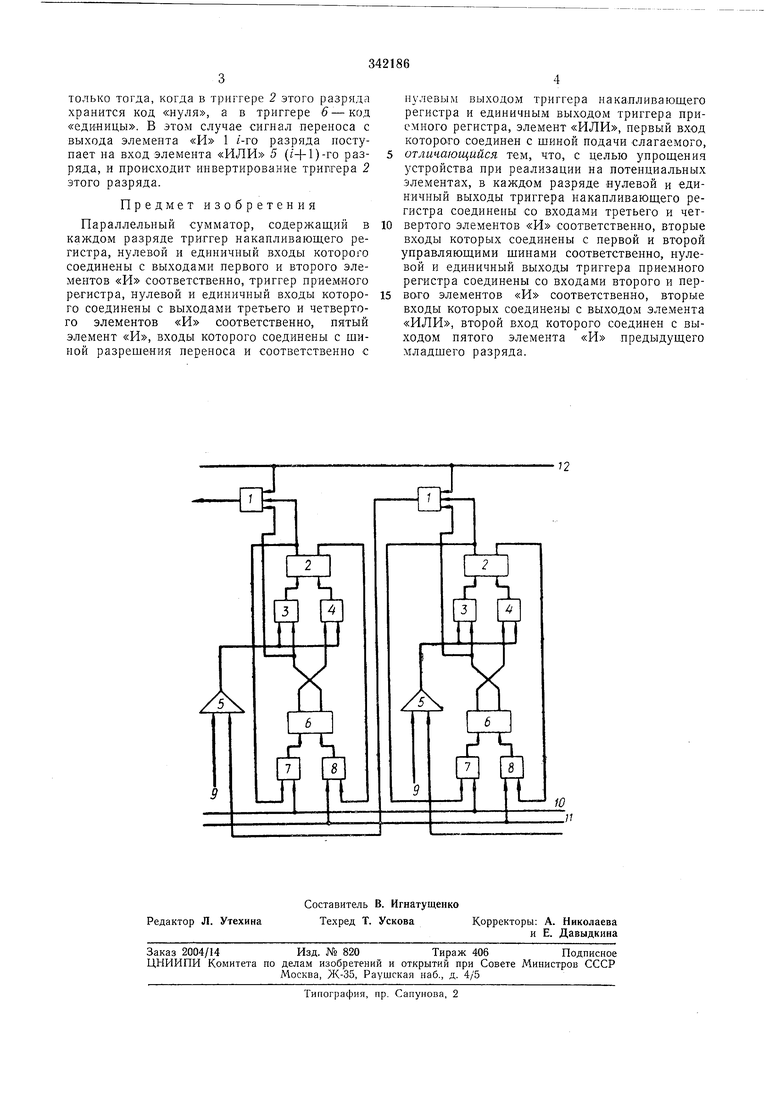

Схема устройства изображена на чертеже.

приемного регистра 6 с элементами «И 7 и 8, шину 9 подачи слагаемого, шины управления 10 и 11 и шину разрешения переноса 12.

Устройство работает следующим образом. Допустим, что в накапливающем регистре (триггеры 2) хранится код первого слагаемого, а по шинам 9 поступает код второго слагаемого. В первом такте код, хранящийся в накапливающем регистре, пересылается в приемный регистр (триггеры 6). Для того чтобы выполнить эту операцию, на шины 10 и // одновременно подаются исполнительные импульсы.

Во втором такте по шинам 9 поступает код второго слагаемого и, в случае наличия на шине 9 данного разряда кода «1 происходит инвертирование соответствующего триггера 2. Если код второго слагаемого в данном разряде равен «нулю, то состояние триггера 2 этого разряда не изменяется.

В третьем такте выполняется операция логического сложения кодов, хранящихся в накапливающем и приемном регистрах, для этого на шину 11 подается исполнительный импульс.

В четвертом такте разрешается распространение потенциала переноса и формирование результата суммирования кодов двух чисел; для этого на шину 12 подается исполнительный импульс. Формирование сигнала переноса из 1-го разряда в (i+)-u разряд выполняется

только тогда, когда в триггере 2 этого разряда хранится код «нуля, а в триггере 5-код «единицы. В этом случае сигнал переиоса с выхода элемента «И 1 /-го разряда поступает на вход элемеита «ИЛИ 5 (г4-1)-го разряда, и происходит инвертирование триггера 2 этого разряда.

Предмет изобретения

Параллельный сумматор, содержащий в каждом разряде триггер накапливающего регистра, нулевой и единичный входы которого соединены с выходами первого и второго элементов «И соответственно, триггер приемного регистра, нулевой и единичный входы которого соединены с выходами третьего и четвертого элементов «И соответственно, пятый элемент «И, входы которого соединены с шиной разрешения переноса и соответственно с

нулевым выходом триггера накалливающего регистра и единичным выходом триггера приемного регистра, элемент «ИЛИ, первый вход которо.го соединен с шиной подачи слагаемого, отличающийся тем, что, с целью упрощения устройства при реализации на потенциальных элементах, в каждом разряде нулевой и единичный выходы триггера накапливающего регистра соединены со входами третьего и четвертого элементов «И соответственно, вторые входы которых соединены с первой и второй управляющими шинами соответственно, нулевой и единичный выходы триггера приемного регистра соединены со входами второго и первого элементов «И соответственно, вторые входы которых соединены с выходом элемента «ИЛИ, второй вход которого соединен с выходом пятого элемента «И предыдущего младшего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2261469C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| Арифметическое устройство параллельного действия | 1977 |

|

SU643870A1 |

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| Накапливающий сумматор | 1985 |

|

SU1262479A1 |

| ДВОИЧНЫЙ ПАРАЛЛЕЛЬНЫЙ СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 1973 |

|

SU378844A1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

Даты

1972-01-01—Публикация