1

Изобретение относится к автомати ке и вычислительной технике, может быть применено, в частности, в мощных выходных каскадах логических устройств.

Известен инвертор на ВДП-транзисторах, содержащий транзистор предварительного заряда, затвор и сток которого подключен к шине питания, а исток - к затвору нагрузочного транзистора, между затвором и истоком которого включен ускоряющий конденсатор, сток нагрузочного транзистора подключен к шине питания, а исток - к выходной шине и к стоку переключающего транзистора, исток которого подключен к общей шине, а затвор - ко входной .

У этого устройства большая потребляемая статическая мощность, обусловленная протеканием большого тока в цепи переключающего и нагрузочного транзисторов,

. Известен управляегйай инвертор на МДП-транзисторах, содержащий транзистор предварительного заряда, затвор и сток которого подключены к шине питания, а исток - к затвору нагрузочного транзистора, между затвором и истоком которого включен ускоряющий конденсатор, сток нагрузочного транзистора подключен к шине питания, а исток - к стоку переключающего транзистора, исток которого

подключен к общей шине и к затвору зарядного транзистора, сток которого подключен к шине питания, исток - к выходной шине и к стоку разрядного транзистора, исток которого подклю

чен к общей шине, а затвор - ко входной шине и затвору переключающего транзистора, потребляемая мощность которого значительно снижена, так как все транзисторы, зарядного

и разрядного, могут быть маломощными, а зарядный и разрядный транзисторы не потребляют статической мощности 2. У этого инвертора уровень выходного напряжения логической единицы меньше

значения напряжения питания.

Цель изобретения - повышение уровня выходного напряжения йогической единицы.

Для достижения этой цели в управлаемый инвертор на МДП-транзисторах, содержащий транзистор -редварительного заряда, затвор и сток которого подключены к шине питания, а исток - к затвору нагрузочного транзистора, меж

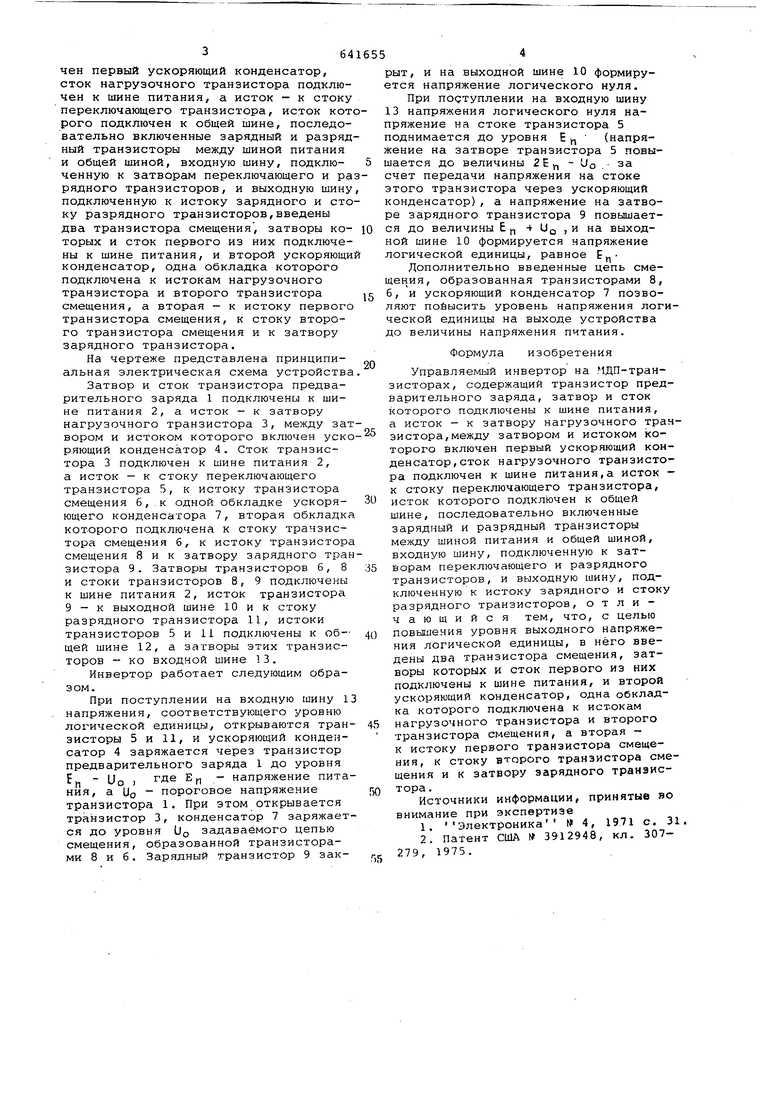

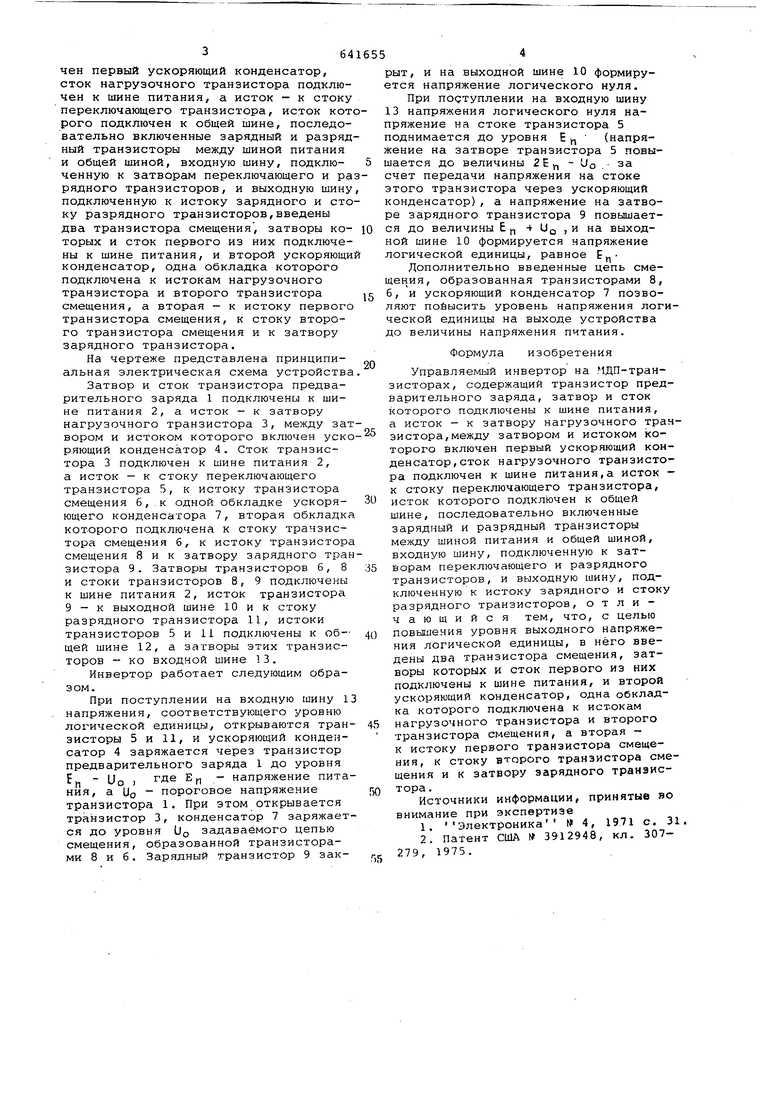

ду затвором и истоком которого вклю 6чен первый ускоряющий конденсатор, сток нагрузочного транзистора подключен к шине питания, а исток - к стоку переключающего транзистора, исток кот рого подключен к общей шине, последовательно включенные зарядный и разряд ный транзисторы между шиной питания и общей шиной, входную шину, подключенную к затворам переключающего и ра рядного транзисторов, и выходную шину подключенную к истоку зарядного и сто ку разрядного транзисторов,введены два транзистора смещения , затворы которых и сток первого из них подключены к шине питания, и второй ускоряющи конденсатор, одна обкладка которого подключена к истокам нагрузочного транзистора и второго транзистора смещения, а вторая - к истоку первого транзистора смещения, к стоку второго транзистора смещения и к затвору зарядного транзистора. На чертеже представлена принципиальная электрическая схема устройства Затвор и сток транзистора предварительного заряда 1 подключены к шине питания 2, а исток - к затвору нагрузочного транзистора 3, между за вором и истоком которого включен уск ряющий конденсатор 4. Сток транзистора 3 подключен к шине питания 2, а исток - к стоку переключающего транзистора 5, к истоку транзистора смещения 6, .к одной обкладке ускоряющего конденсатора 7, вторая обкладк которого подключена к стоку транзистора смещения 6, к истоку транзистор смещения 8 и к затвору зарядного тра зистора 9. Затворы транзисторов 6, и стоки транзисторов 8, 9 подключены к шине питания 2, исток транзистора 9 - к выходной шине 10 и к стоку разрядного транзистора 11, истоки транзисторов 5 и 11 подключены к общей шине 12, а затворы этих транзисторов - ко входной шине 13. Инвертор работает следующим образом. При поступлении на входную шину 1 напряжения, соответствующего уровню логической единицы, открываются тран зисторы 5 и 11, и ускоряющий конденсатор 4 заряжается через транзистор предварительного заряда 1 до уровня ЕЙ Uo ) Д п - напряжение пита ния, а UQ пороговое напряжение транзистора 1. При этом открывается транзистор 3, конденсатор 7 заряжает ся до уровня UQ задаваемого цепью смещения, образованной транзисторами 8 и 6 . Зарядный транзистор 9 закыт, и на выходной шине 10 формирутся напряжение логического нуля. При поступлении на входную шину 13 напряжения логического нуля наряжение на стоке транзистора 5 однимается до уровня Е (напряение на затворе транзистора 5 повыается до величины 2Е| - UQ -за чет передачи напряжения на стоке того транзистора через ускоряющий онденсатор), а напряжение на затвое зарядного транзистора 9 повышается до величины j, + UQ , и на выходной шине 10 формируется напряжение огической единицы, равное Е„Дополнительно введенные цепь смеения, образованная транзисторами 8, б, и ускоряющий конденсатор 7 позвояют пойыситъ уровень напряжения логической единицы на выходе устройства о величины напряжения питания. Формула изобретения Управляемый инвертор на МДП-транзисторах, содержащий транзистор предварительного заряда, затвор и сток которого подключены к шине питания, а исток - к затвору нагрузочного транзистора, между затвором и истоком которого включен первый ускоряющий конденсатор, сток нагрузочного транзистора подключен к шине питания,а исток - к стоку переключающего транзистора, исток которого подключен к общей шине, последовательно включенные зарядный и разрядный транзисторы между шиной питания и общей шиной, входную шину, подключенную к затворам переключающего и разрядного транзисторов, и выходную шину, подключенную к истоку зарядного и стоку разрядного транзисторов, отличающийся тем, что, с целью повышения уровня выходного напряжения логической единицы, в него введены два транзистора смещения, затворы которых и сток первого из них подключены к шине питания, и второй ускоряющий конденсатор, одна обкладка которого подключена к ист.окам нагрузочного транзистора и второго транзистора смещения, а вторая к истоку первого транзистора смещения, к стоку второго транзистора смещения и к затвору зарядного транзистора . Источники информации, принятые во внимание при экспертизе 1.Электроника № 4, 1971 с. 31. 2.Патент США 3912948, кл. 307279, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель-формирователь импульсов на мдп транзисторах | 1974 |

|

SU525247A1 |

| Устройство задержки импульсов | 1977 |

|

SU680163A1 |

| Дешифратор адреса | 1980 |

|

SU938408A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Инвертор на мдп-транзисторах | 1976 |

|

SU646441A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Генератор напряжения смещения подложки в мдп-интегральных схемах | 1978 |

|

SU764097A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Инвертор на МДП-транзисторах | 1982 |

|

SU1128388A1 |

Авторы

Даты

1979-01-05—Публикация

1976-11-29—Подача