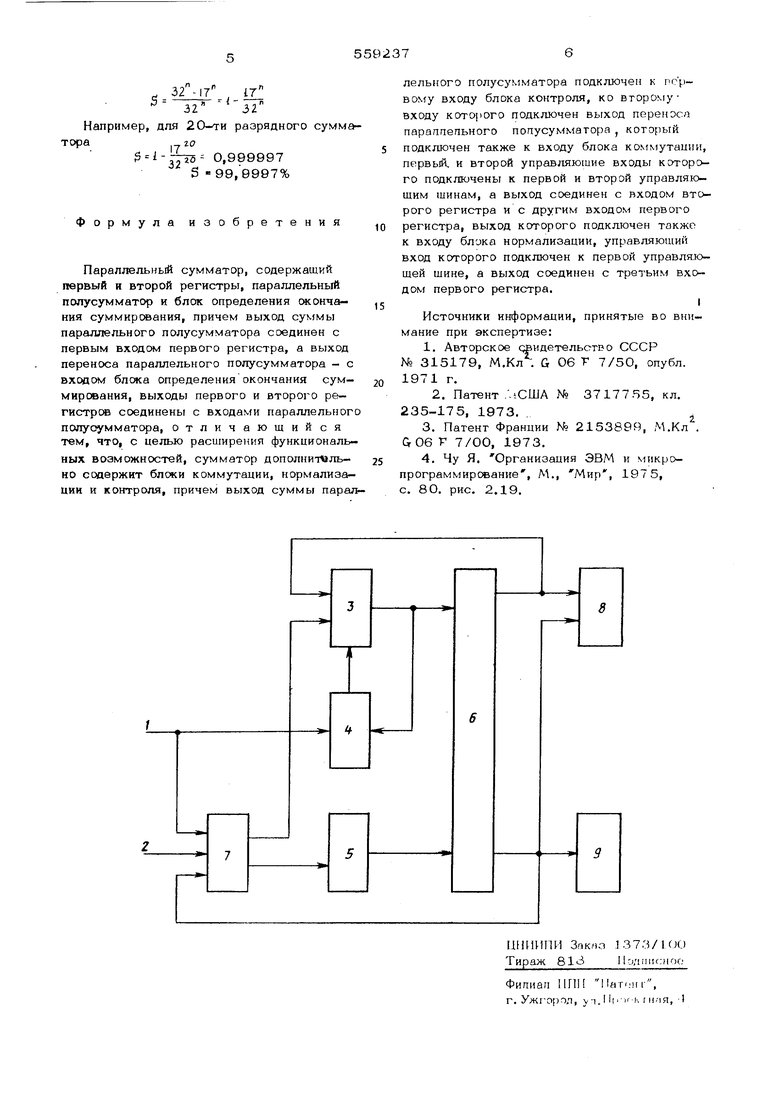

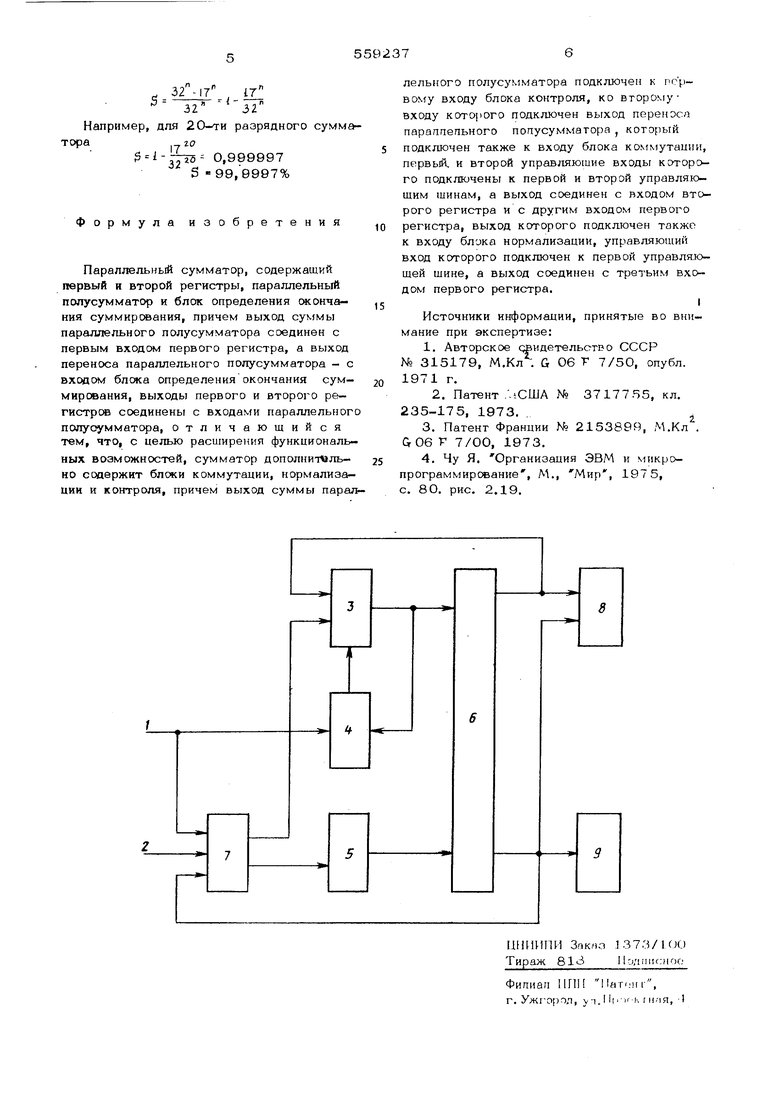

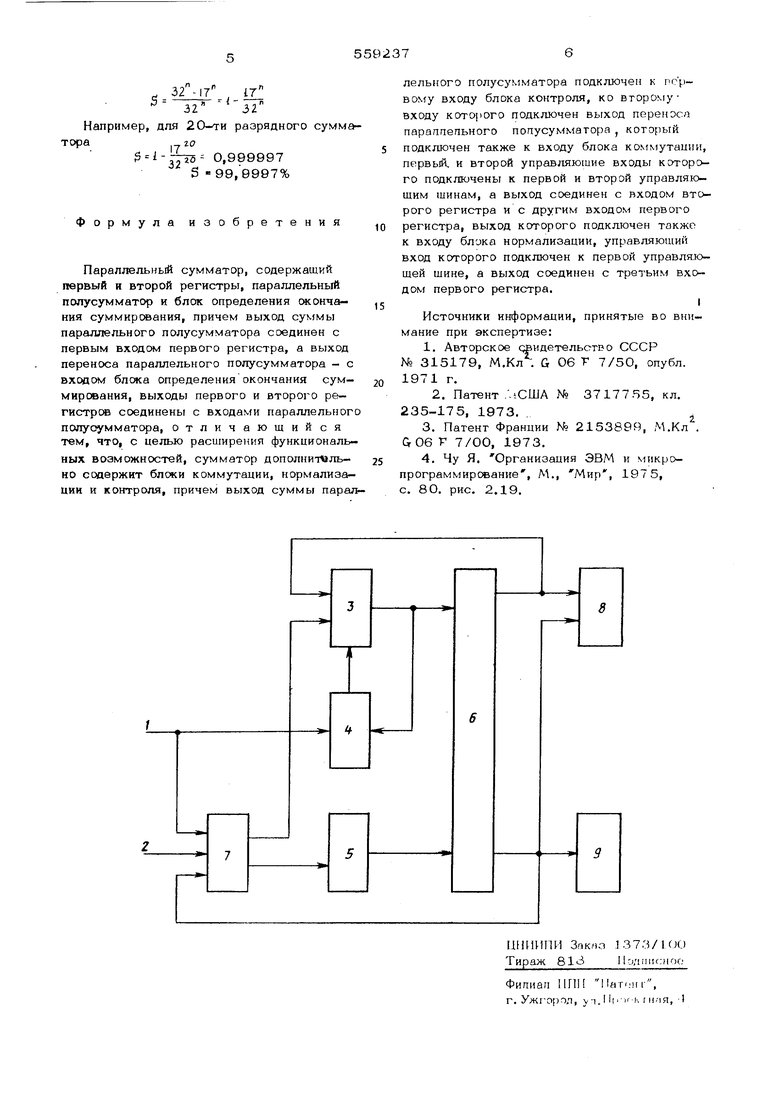

(54) ПАРАЛЛЕЛЬНЫЙ СУММАТОР ПИЯ выполняется согласно следующей таблице:О + О О 0+1 1 1+0 1 , что вытекает из рекуррентного соотношения , ()t4(i)--4(i))f4((+i)) Если в разрядах нормальных представлений слагаемых имеются единицы, то из свойства нормальной формы следует, что суммы (-1 + 1) и (4-1) -X разрядов всегда будут нулевые и, следовательно, единица переноса на i -го в ( + 1)--й разряд всегда может быть помещена в ( I + 1)-й разряд суммы, а перенос из ,ч -го в ( i -2)-Л разряд надо запомнить Из свойства этого способа сложения вытекает возможность организации контроля правильности протекания процесса сум мирования. Признаком неправильного сложения является наличие ненулевой суммы в ( i + 1) или ( i - l)-QM разрядах при возникнсжении переноса в i -ом разряде, т.е. функция ошибки имеет вид .iS«d../...va|S,. - промёжуточньй перенос; Sj - промежуточная сумма. На чертеже дана функциональная схема, параллельного сумматора. В ее состав входят первая управляпощая шина 1,вторая управляющая шина 2,первый рвгис 3, блок нормализации 4, второй регистр 5 параллельный полусумматор 6, блок коммутации 7, блсяс контроля 8, блок определе ния окончания суммирсвания 9. По первой управляющей щине 1 сигнал подается на вход блока коммутации 7 и вход блока нормализации 4. В первом такте слагаемые однсжремен- но подаются на вход параллельного полусумматора 6, одноименные разряды слагае мых попарно складьтаются согласно приведенной таблице сложения. При этом получается сумма и перенос, который при правильной работе сумматора будет| представле нормальной формой. Разряды суммы пересы лаются в первый регистр 3. Бпок коммута 7 осуществляет запись переноса { -го раз ряда в ( + I)-й разряд первого регистра 3 и в (- 2)-й разряд второго регистра 5. Содержимое первого регистра 3 (сумма и перенос) с помощью блока нормализации 4 приводится к нормальной форме. При этом образуется первая промежуточная сумма. Во втором регистре 5 находится первый п межуточный перенос. Во втopo ; такте происходит сложение 5 первой проктежутичной суммы j и первого промежуточного переноса d и образуется вторая промежуточная сумма S- и второй промежуточный перенос dj. Аналогичным образом устройство работает и в последующих тактах. Этот процесс продолжается до тех пор, пока промёжуточньй перенос не будет состоять из одних нулей. При этом блоком 9 вырабатьгоается сигнал окончания операции сложения. Если во время работы на выходах параллельного полусумматора 6 появится щибочная кодовая комбинация, то блок 8 формирует сигнал ощибки. Пример. Сложить числа А . 1001О01О10иВ 10100010ОО 1. Образование промежуточной суммы Si и переноса а А- 1001001010 В 1010001000 Sj lOOllOlOOlO d, 00010000010 Приведение S к нормальной форме Sj 1 О 9 1 ; о 1 о о 1 о 10100010010. 2. Образование промежуточной суммы. и переноса dj Sj lOlOOOlOOlO d OOOIOOOO OlO $ « 10110010011 d2 00000000000 Приведение Sj, к нормальной форме 911 0010 911 ju о о о о 1 о 1 о о ooooooioio о Сложение закончено A-t-B -Зг При сложении чисел в традиционной двоичной системе счисления подается управляющий сигнал по второй управляющей шине. При этом с помощью блока коммутации 7 осуществляется запись переноса (. -го разряда только в (i + 1)-й разряд второго регистра 5. Блок нормализации 4 в этом режиме не работает. Сложение происходит известным образом. Введение новых блсжов и связей позволяет расширить функциональные возможности параллельного сумматора, а именно выполнять операцию суммирсжания чисел, представленных вфибоначчиевой системе счисления, обладающей высокой ошибкообнаруживающей способностью. Коэффициент обнаружения ошибок для фибоначчиевого сумматора определяется следующим выражением:

32-17

L7

5

Например, для 20-ти разрядного го

Г7 32

0,999997 S99/9997%

Формула изобретения

Параллельный сумматор, содержащий первый и второй регистры, параллельный полусумматор и блок определения сжонча- НИН суммирсжания, причем выход суммы параллельного полусумматора соединен с первым входом первого регистра, а выход переноса параллельного полусумматора - с входом блока определения окончания суммирования, выходы первого и второго ре- гистрсе соединены с входами параллельног полусумматора, отличающийся тем, что, с целью расширения функциональных возможностей, сумматор дополнительно содержит блоки коммутации, нормализации и контроля, причем выход суммы параллельного полусумматора подключен к рсрBONfy входу блока контроля, ко второмувходу которого подключен выход переноса параппепьного попусумматора , который подключен также к входу блока коктмутацнн, П6ФВЫЙ. и второй управляющие входы которого подключены к первой и второй управля.ющим шинам, а выход соединен с входом второго регистра и с другим входом первого регистра, выход которого подключен такжо к входу блока нормализации, управляющий вход которого подключен к первой управля.ю- щей шине, а выход соединен с третьим входом первого регистра.

I

Источники информации, принятые во внимание при экспертизе:

1. Авторское овидетельсгво СССР № 315179, М.Кл G 06 Т 7/50, опубл. 1971 г.

2. Патент ..«США № 3717755, кл. 235-175, 1973. .

3. Патент Франции N° 2153899, М.Кл . а 06 Г 7/00, 1973.

4. Чу Я. Организация ЭВМ и микропрограммирование, А., Мир, 1975, с. 8О. рис, 2.19.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный сумматор кодов фибоначчи | 1978 |

|

SU840891A1 |

| Вычислительное устройство | 1984 |

|

SU1176322A1 |

| Устройство для деления | 1983 |

|

SU1151955A1 |

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Сумматор кодов Фибоначчи | 1981 |

|

SU981993A1 |

| Суммирующее устройство | 1979 |

|

SU824200A1 |

| Устройство для умножения | 1981 |

|

SU997031A1 |

Авторы

Даты

1977-05-25—Публикация

1976-05-03—Подача