1

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых- устройств помехоустойчивой обработки информации.

Известны двоичные сумматоры многоразрядных двоичных чисел, содержащие, регистры, блок параллельного суммирования и блок определения окончания суммирования l и 2.

Наиболее близким к предлагаемому является суммирующее устройство, содержащее первый и второй регистры, блок параллельного суммирования, блоки определения окончаний суммирования, нормализации, контроля и коммутации, причем выход суммы блока параллельного суммирования подключен к первому входу блока контроля и входу первого регистра, а к его второму входу подключен выход переноса блока параллельного суммирования, который подключен также ко входу блока коммутации и входу блока определения окончания суммирования. Выходы первого и второго регистров соединены со входами блока параллельно суммирования.

Первый и второй управляквдие входы блока коммутации подключены к управЛЯЮ1ЦИМ шинам устройства, а выходы его соединены со входами первого и второго регистров, выход первого регистра подключен ко входу блока нормализации, управляющий вход которого подключен к первой управляющей шине устройства, а выход соединен со входом первого регистра 3j.Недостаток приведенного двоичного

0 сумматора заключается в том, что он не позволяет суммировать числа представленные в избыточных (г , р) системах счисления, предназначенных для сквозного контроля информационно-вы5 числительных систем (ИВС).

Цель изобретения - расширение , функциональных возможностей устройства.

Поставленная цель достигается тем,

0 что устройство, содержащее первый и второй регистры, блок параллельного суммирования, блок определения окониания су« мрования, блок контроля, блок нормализации и блок коммутации,

5 причём выходы первого и второго регистров соединены с соо ветствукицими входами блока параллельного суммирования, выход суммы которого соединен со входом первого регистра и

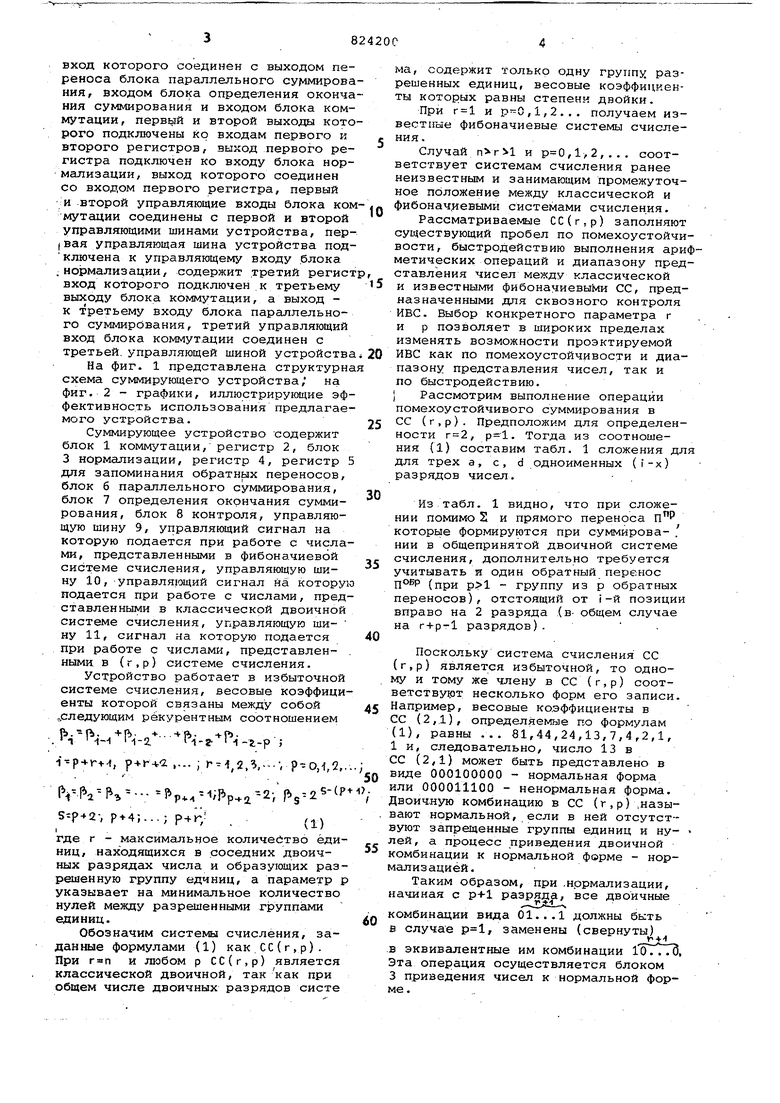

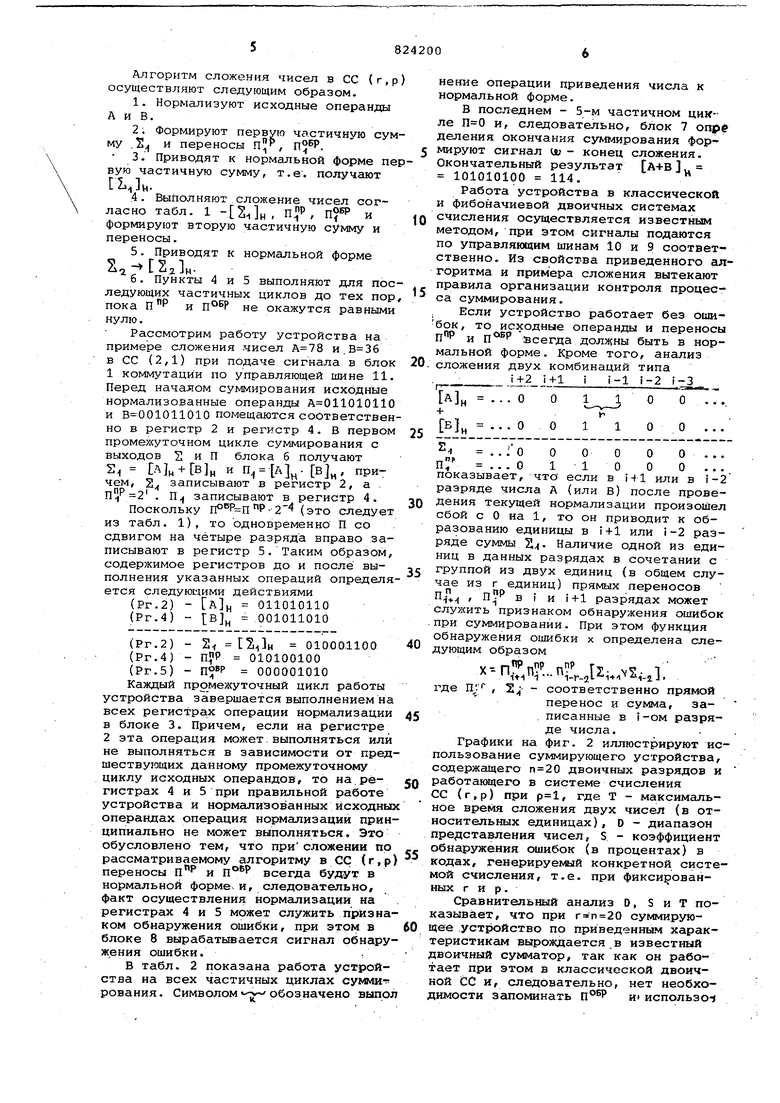

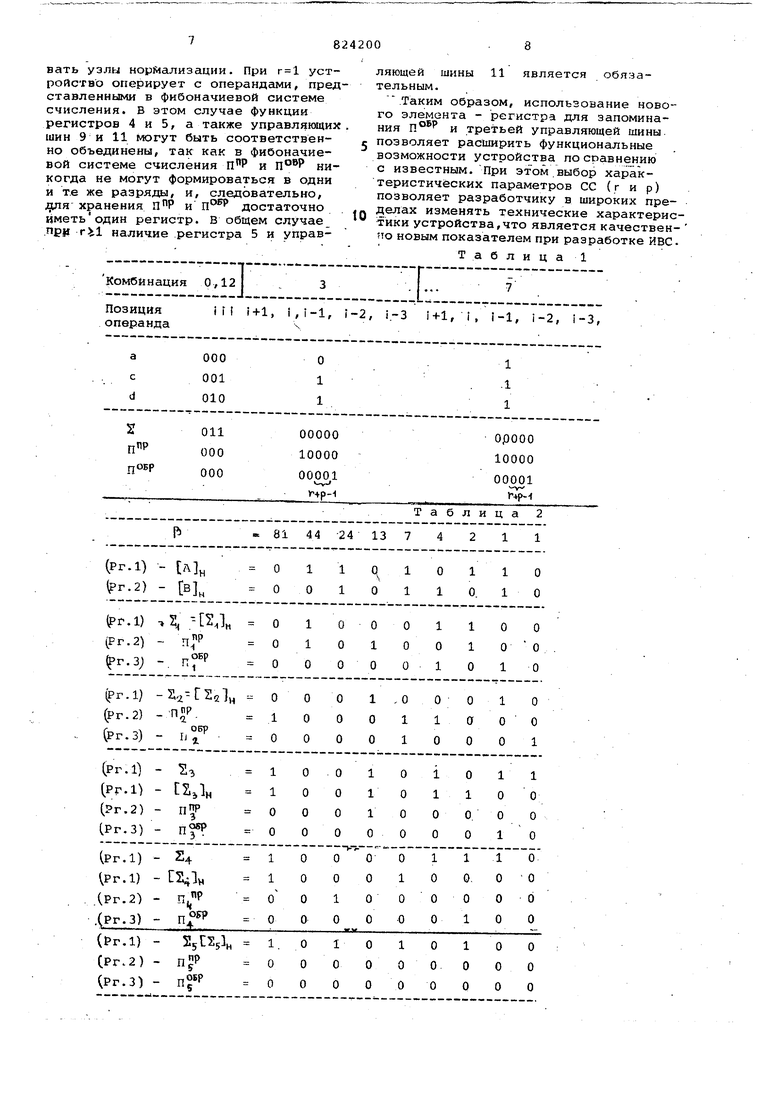

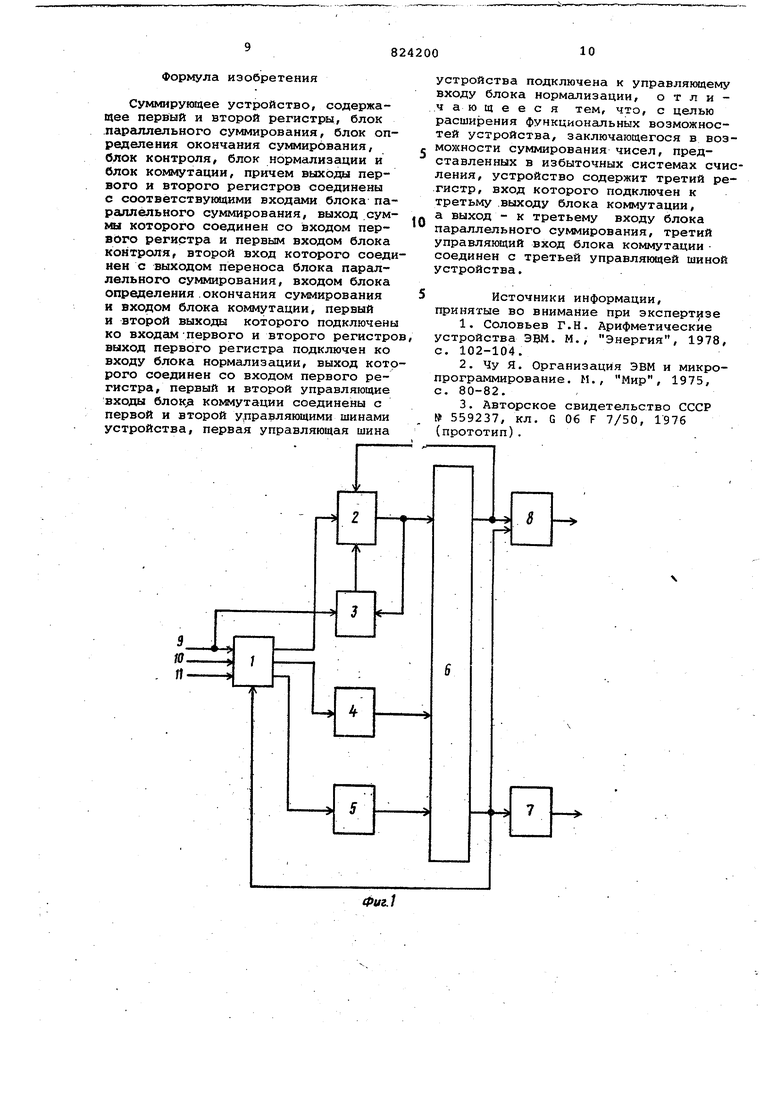

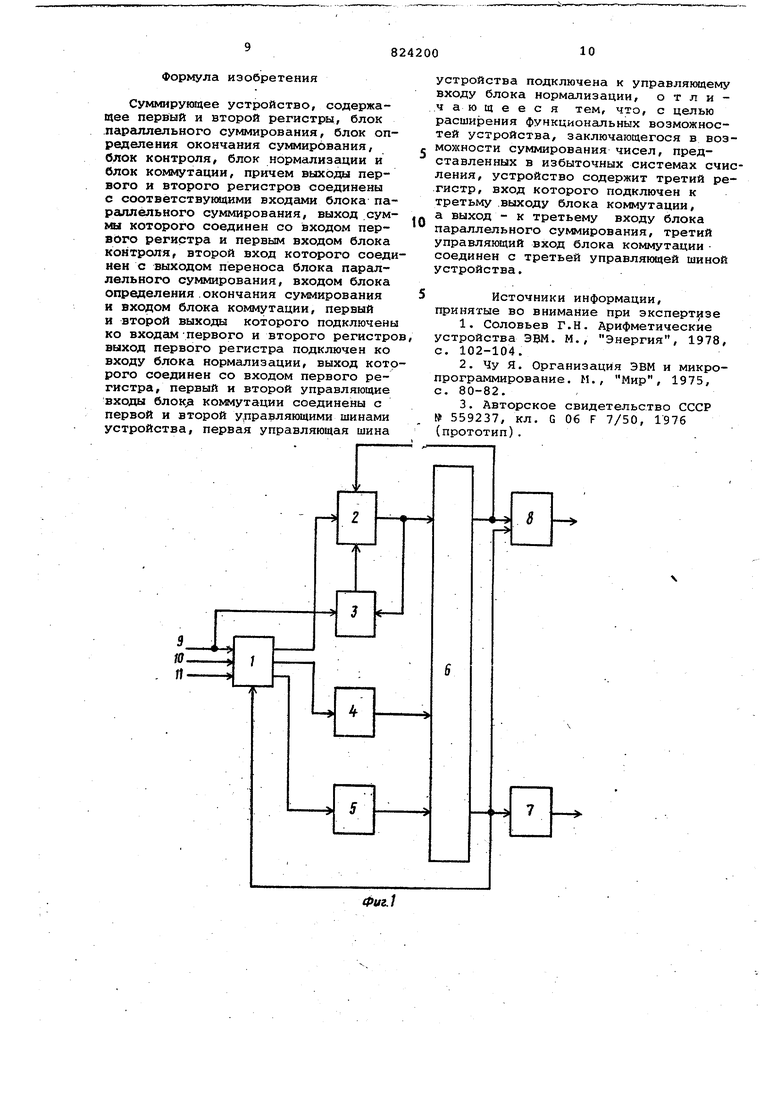

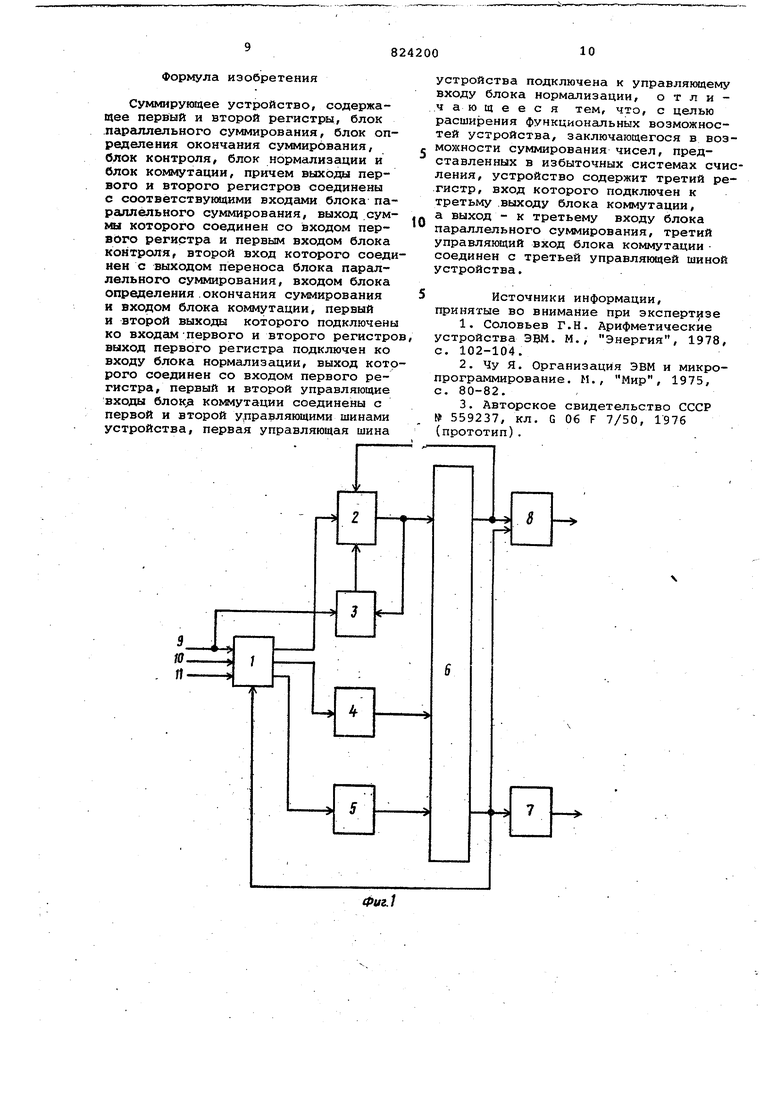

0 первым входом блока контроля, второй вход которого соединен с выходом переноса блока параллельного суммирова ния, входом блока определения оконча ния суммирования и входом блока коммутации, первый и второй выходы кото рого подключены ко входам первого и второго регистров, выход первого регистра подключен ко входу блока нормализации, выход которого соединен со входом первого регистра, первый и второй управляющие входы блока ком мутации соединены с первой и второй управляющими шинами устройства, пер1вая управляющая шина устройства подключена к управляющему входу блока ,нормализации, содержит третий регист вход которого подключен к третьему выходу блока коммутации, а выход к третьему входу блока параллельного суммирования, третий управляющий вход блока коммутации соединен с третьей, управляющей шиной устройства На фиг. 1 представлена структурна схема суммирующего устройства, на фиг. 2 - графики, иллюстрирующие эффективность использования предлагаемого устройства. Суммирующее устройство содержит блок 1 коммутации, регистр 2, блок 3 нормализации, регистр 4, регистр 5 для запоминания обратных переносов, блок б параллельного суммирования, блок 7 определения окончания суммирования, блок 8 контроля, управляющую шину 9, управляющий сигнал на которую подается при работе с числами, представленными в фибоначиевой системе счисления, управляющую шину 10, -управлякнций сигнал на которую подается при работе с числами, представленными в классической двоичной системе счисления, управляющую шину 11, сигнал на которую подается при работе с числами, представленными в (г,р) системе счисления. Устройство работает в избыточной системе счисления, весовые коэффициенты которой связаны между собой следующим рёкурентным соотношением Ь.-П. +Г)- -«-...-tft. +{ъ. . 1., I I -2 Ц.2. 1 1-.р ; + rt, p+c-vi .... ; гм,2,,----, р-о,(,2,. N.-,;Pp.i-2-, , , p + 4;...; p+r; , (.j.) где r - максимальное количество единиц, находящихся в соседних двоичных разрядах числа и образующих разрешенную группу единиц, а параметр р указывает на минимальное количество нулей между разрешенными группами единиц. Обозначим системы счисления, заданные формулами (1) как СС(г,р). При и любом р СС(г,р) является классической двоичной, так как при общем числе двоичных разрядов систе ма, содержит только одну группу разрешенных единиц, весовые коэффициенты которых равны степени двойки. При и р-0,1,2... получаем известные фибоначиевые системы счисления. Случай и ,,,.. соответствует системам счисления ранее неизвестным и занимающим промежуточное положение между классической и фибонач евыми системами счисления. Рассматриваемые СС(г,р) заполняют существующий пробел по помехоустойчивости, быстродействию выполнения арифметических операций и диапазону представления чисел между классической и известными фибоначиевыми СС, предназначенными для сквозного контроля иве. Выбор конкретного параметра г и р позволяет в широких пределах изменять возможности проэктируемой иве как по помехоустойчивости и диапазону представления чисел, так и по быстродействию. j Рассмотрим выполнение операции помехоустойчивого суммирования в СС (г,р). Предположим для определенности , . Тогда из соотношения (1) составим табл. 1 сложения для для трех а, с, d одноименных (i-x) разрядов чисел. Из табл. 1 видно, что при сложении помимо S и прямого переноса которые формируются при суммироваНИИ в общепринятой двоичной системе счисления, дополнительно требуется учитывать н один обратный перенос пОБр (при - группу из р обратных переносов), отстоящий от i-и позиции вправо на 2 разряда (в- общем случае на г-(-р-1 разрядов) . . Поскольку система счисления СС (г,р) является избыточной, то одному и тому же члену в СС (г,р) соответствуют несколько форм его записи. Например, весовые коэффициенты в СС (2,1), определяемые по формулам (1), равны ... 81,44,24,13,1,4,2,1t 1 и, следовательно, число 13 в СС (2,1) может быть представлено в виде 000100000 - нормальная форма или 000011100 - ненормальная форма. Двоичную комбинацию в СС (г,р),называют нормальной, если в ней отсутствуют запрещенные группы единиц и ну- лей, а процесс приведения двоичной комбинации к нормальной форме - нормализацией. Таким образом, при .нормализации, начиная с р-И разрял;а, все двоичные комбинации вида 01...1 должны быть в случае заменены (свернуты) J2Jtl-, .в эквивалентные им комбинации lo7V73, Эта операция осуществляется блоком 3 приведения чисел к нормальной форме. Алгоритм сложения чисел в СС (г,р осуществляют следующим образом, 1.Нормализуют исходные операнды Лив. 2.Формируют первую частичную сум му .2 и переносы , П. 3.Приводят к нормальной форме пе вую частичную сумму, т.в , получают .Выполняют сложение чисел согласно табл. 1 , , П и формируют вторую частичную сумму и переносы. 5.Приводят к нормальной форме . 6.Пункты 4 и 5 выполняют для пос ледующих частичных циклов до тех пор пока и не окажутся равными нулю. Рассмотрим работу устройства на примере сложения чисел в СС (2,1) при подаче сигнала в блок 1коммутации по управляющей шине 11, Перед началом суммирования исходные нормализобанные операнды А 011010110 и В 001011010 помещаются соответствен но в регистр 2 и регистр 4, В первом промежуточном цикле суммирования с выходов 2 и П блока б получают S + и , причем, 2 записывают в регистр 2, а , П записывают в регистр 4. Поскольку (это следует из табл. 1), то одновременно П со сдвигом на четыре разряда вправо записывают в регистр 5. Таким образом, содержимое регистров до и после выполнения указанных операций определя ется следующими действиями (Рг.2) - 011010110 (Рг.4) - В 001011010 (Рг.2) - 2 010001100 (Рг.4) - nfiP 010100100 (Рг.5) - 000001010 Каждый промежуточный цикл работы устройства завершается выполнением на всех регистрах операции нормализации в блоке 3. Причем, если на регистре 2эта операция может.выполняться или не выполняться в зависимости от пред шествующих данному промежуточному циклу исходных операндов, то на рёгистрах 4 и 5 при правильной работе устройства и нормализованных исходны операндах операция нормализации прин ципиально не может выполняться. Это обусловлено тем, что при сложении по рассматриваемому алгоритму в СС (г,р переносы п и всегда будут в нормальной формеч и, следовательно, факт осуществления нормализации на регистрах 4 и 5 может служить призна ком обнаружения ошибки, при этом в блоке 8 вырабатывается сигнал обнару жения ошибки. В табл. 2 показана работа устройства на всех частичных циклах суммирования. Символом «-j обозначено выпр некие операции приведения числа к нормальной форме. В последнем - 5-м частичном цикле и, следовательно, блок 7 опр деления окончания суммирования формируют сигнал (а - конец сложения. Окончательный результат ГА+вЗ.. 101010100 114, Работа устройства в классической и фибоначиевой двоичных системах счисления осуществляется известным методом, при этом сигналы подаются по управляющим шинам 10 и 9 соответственно. Из свойства приведенного алгоритма и примера сложения вытекают правила организации контроля процесса суммирования, Если устройство работает без ошибок, то исходные операнды и переносы и всегда должны быть в нормальной форме. Кроме того, анализ сложения двух комбинаций типа i+2 i+1 i i-1 i-2 ,,,0 1 1 О О О ,,, показывает, что если в HI или в i-2 разряде числа А (или в) после проведения текущей нормализации произошел сбой с О на 1, то он приводит к образованию единицы в i+1 или i-2 разряде суммы Наличие одной из единиц в данных разрядах в сочетании с группой из двух единиц (в общем случае из г единиц) прямых переносов пЦ , П в i и i+1 разрядах может служить признаком обнаружения ошибок при суммировании. При этом функция обнаружения ошибки х определена следующим образом X-пп П- 7 1 X 1Ц.1Ц... n,i,ii.,J, где П.; , - соответственно прямой перенос и сумма, за. писанные в i-ом разряде числа. Графики на фиг. 2 иллюстрируют использование суммирующего устройства, содержащего двоичных разрядов и работакадего в системе счисления СС (г,р) при , где Т - максимальное время сложения двух чисел (в относительных единицах), D - диапазон представления чисел, S - коэффициент обнаружения ошибок (в процентах) в кодах, генерируемый конкретной системой счисления, т,е, при фиксированных г и р, Сравнительный анализ О, S и Т показывает, что при суммирующее .устройство по приведенным характеристикам вырождается в известный двокчный сумматор, так как он работает при этом в классической двоичной СС и, следовательно, нет необходимости запоминать П° и использо-

вать узлы нормализации. При устройство оперирует с операндами, представленными в фибоначиевой системе счисления. В этом случае функции регистров 4 и 5, а также управляющих шин 9 и 11 могут быть соответственно объединены, так как в фибоначиевой системе счисления и никогда не могут формироваться в одни и те же разряды, и, следовательно, j3jin- хранения и П° достаточно . Иметьодин регистр. В общем случае прр г%.1 наличие .регистра 5 и управляющей шины 11 является обязательным.

.Таким образом, использование нового элемента - регистра для запоминания и третьей управляющей шины позволяет расширить функциональные возможности устройства по сравнению с известным.При этом.выбор характеристических параметров СС (г и р) позволяет разработчику в широких пределах изменять технические характерис0 5 тики устройства,что является качественно новым показателем при разработке ИБС.

Таблица

Формула изобретения

Суммирующее устройство, содержащее первый и второй регистры, блок .параллельного суммирования, блок определения окончания суммирования, блок контроля, блок нормализации и блок коммутации, причем выхода первого и второго регистров соединены с соответствующими входами блока параллельного суммирования, выход суммы которого соединен со :входом первЬго регистра и первым входом блока контроля, второй вход которого соединен с выходом переноса блока параллельного суммирования, входом блока определения.окончания суммирования и входом блока коммутации, первый и второй выходы которого подключены ко входам -первого и второго регистро выход первого регистра подключен ко входу блока нормализации, выход которого соединен со входом первого регистра, первый и второй управляющие входы блок коммутации соединены с первой и второй у,правляющими шинами устройства, первая управляющая шина

устройства подключена к управляющему входу блока нормализации, о т л и .чающееся тем, что, с целью расширения функциональных возможностей устройства, заключающегося в возмох ности суммирования чисел, представленных в избыточных системах счисления, устройство содержит третий регистр, вход которого подключен к третьму выходу блока коммутации, а выход - к третьему входу блока параллельного суммирования, третий управляющий вход блока коммутации соединен с третьей управляющей шиной устройства.

Источники информации, принятые во внимание при экспертизе

1.Соловьев Г.Н. Арифметические устройства ЭВМ. М., Энергия, 1978, с. 102-104.

2.Чу Я. Организация ЭВМ и микропрограммирование. М., Мир, 1975, с. 80-82.

3.Авторское свидетельство СССР 559237, кл. G 06 F 7/50, 1976 (прототип)..

-А Л TiOmH.e3

го

| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующее устройство | 1984 |

|

SU1234828A1 |

| Устройство для сложения чисел в из-быТОчНОй СиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824199A1 |

| Устройство для умножения | 1981 |

|

SU997031A1 |

| Параллельный сумматор | 1976 |

|

SU559237A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| Вычислительное устройство | 1984 |

|

SU1176322A1 |

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Параллельный сумматор кодов фибоначчи | 1978 |

|

SU840891A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

Авторы

Даты

1981-04-23—Публикация

1979-07-06—Подача