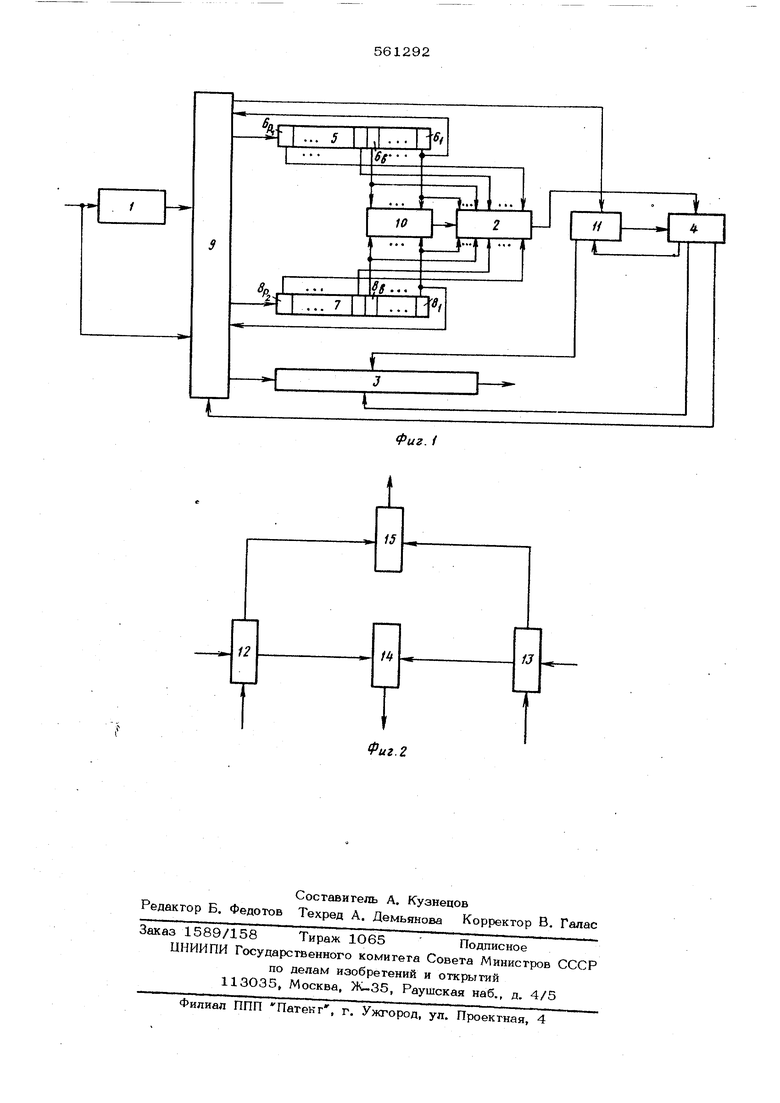

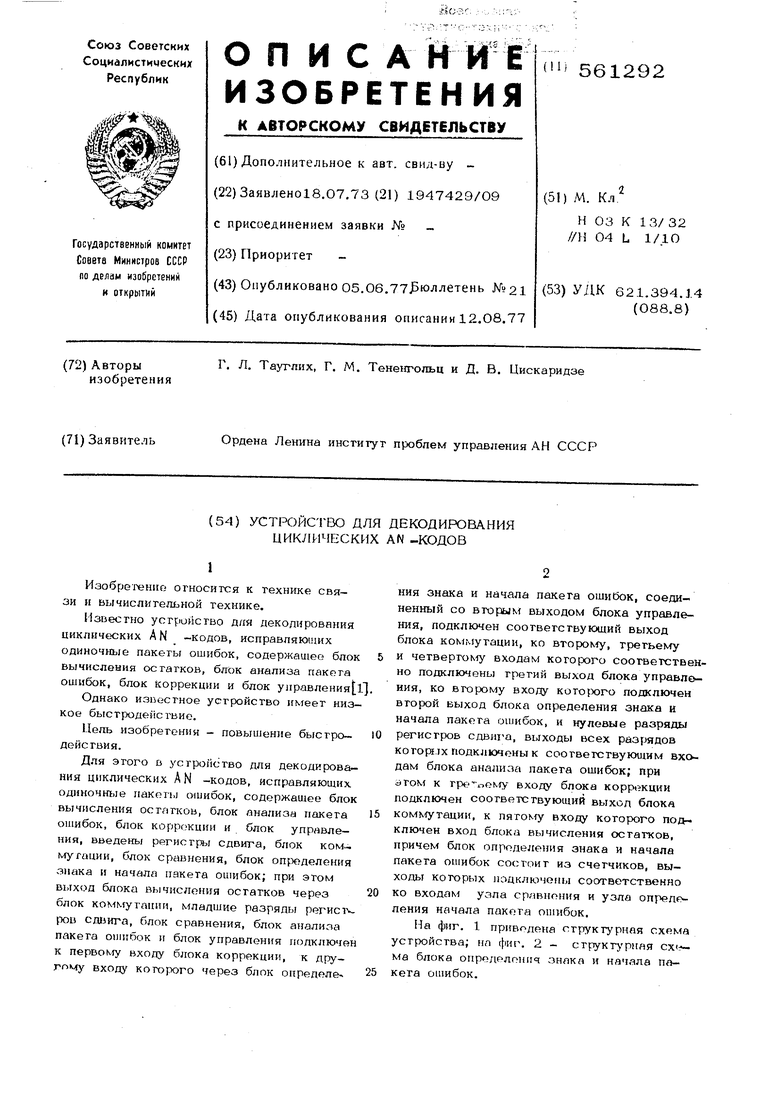

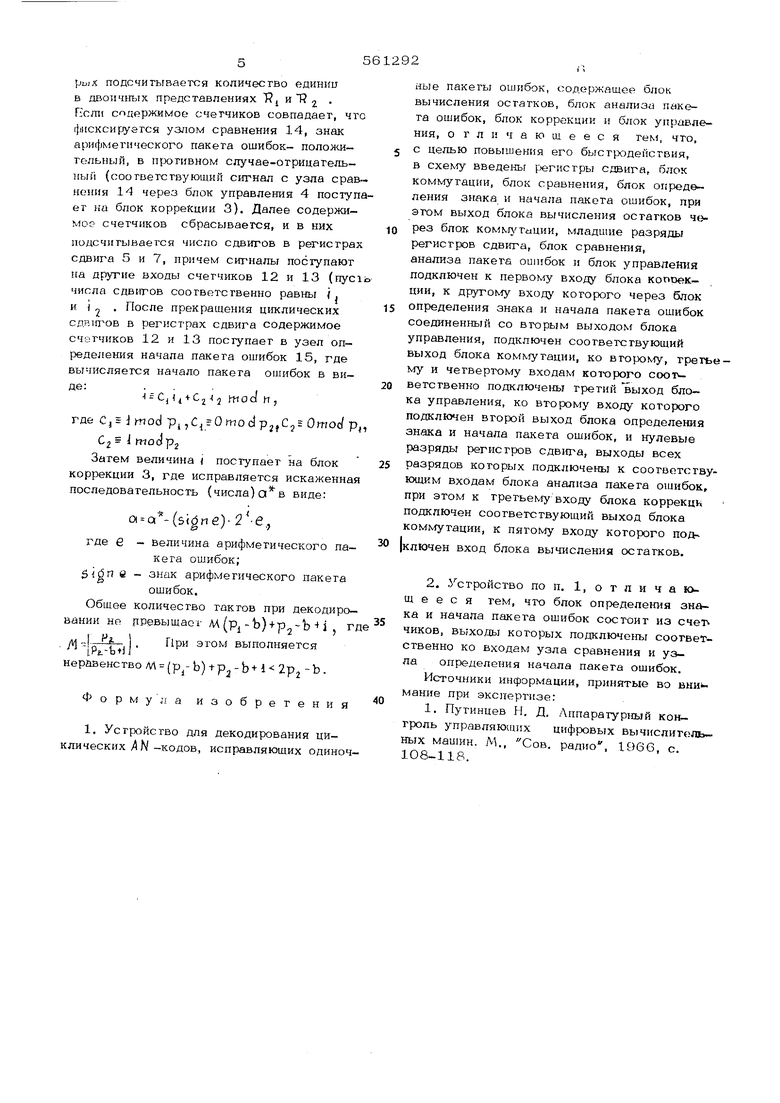

(54) УСТРОЙСГЕЮ ДЛЯ ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКИХ AN-КОДОВ ycTpoiicrao lUiK дексшировспшя гижличес KHxAN -кодоЕ, псп|1авляюших oyiihonibie пако7 л ошибок, С1 поржнг блок вычисления остлгкоЕ 1, блок анализа пакета ошибок 2 блок коррокцип) к 6jiOK ЗТграалеиия 4. ра- гпсгр сдгигр,. 5 с paapHflafvjJ О, ,,.,6, 6р регисгр 7 с разрядами 8|,.„,8},,. ..,8р . блок коммутации 9, блок сравнения 10, блок с1 редело1П1я знака и началга паке га ошибок 11. При этом БЫХОД блока выч.ислонля осгнгков 1 через блок кoм fyгaчии 9, младшпе раз1ядьг G|,...,6jjH 8|,.. ,,, yiorncTjioii сдлига 5 п 7, блок cpaBUeHiiM К), блж анализа пакета ошибо 2 н блок уирап1 ек-; по.дключен к перво viy входу 6i.o;:i :.-дм |1;;кц 1К 3. К д лугому олок определения и 1гаЧ:;;;а опп-бок 11, соеднпеитшп ;:;о )Л. .г.ыходом блока управле ния , по/;.лочои соогвегсгглгталий выход блока ком лутая;|м О, ко второму, третьему п FerBfipTTJivv входам. которого соогвег сгвенпо подключопы трггий выход блока управление -1, Ко входу блока 4 подклгоче ы ат-орои выход блока опредоде- ния знака м начала пакета олпгбок 11, и нулевый DJ и 8 ,j регистров сдвига 5 и 7, Bbixonu HCGX разрядов G|,s.. ,,, IJij,...,,о |. ); 8, ,. ,.,.;-;,.,.8р которых псд-лжче гг) к сооПОтгт-иующЕк; цходаКГ DijKa змйгп,:::. Пмп е iЧ оиптбок 2, fpn этом к греТьему вхСДу блока хоррокцпи 3 подключен соотвегствугощраг выход блока ком ivfjTaT,iiiii О. к Рйгому входл которого подЕпючоп, Ело,; .;:: ;:;; Числен;- л остатков 1 Блок onpsделонпя знака и начала пакета ошибок 11 сосгоиг из счетчиков 12 к 13, выходы которых подключоЯы соогвегсгвенно ко пхрдалл узла сравнения 14 и узла определения начала накета ошибок 1 .VcrixijicTDo работает следующим обрмзом. Декодирующая снособносгь усгройства основана на алг0рьчгк(е . декодировапргя дгзои нь;х циклических AN -кодов, гдеА()( длина кода п ; р н р - аатурпльньк:- числа, удовлетворяющие слещющик условиям, pj-b С( с наи- больаШИЙ собсгвеилый дели тега., р. ); СРоРг)- .) (b-J);nine делитр ,, 27AA;M fp-t | -j, с1 также (.()p.,1 , --- ---j -p. ДЛЯ любого dftm--i делителя выражения nw,-(m-i)p ; в случае гп А,) .-j-b -t ., ес т|(,5 , а ири ослн 3/6Ь 4p,-pj. 1 акеты ошибок длины, не превосход гшей b , когорь/е исправляются этим кодом, имеют вид; e.i2(l.|,242-), j 6; Q,i ; . На вход устройства поступает искажениая двоичная последовательность (число) а . Далее О поступает на входы блока вычисления остатков 1 и блока комк-гута- ции 9, В течение первого такта в блрке 1 вычисляются остатки и 1, т деления а на и 2 2-1 соответственно. If Через блок коммутации 9 Oi поступает в блок коррекции 3. На второй тскте по сирналу с блока управления 4, ггоданному на блок коммутации 9, Pj 2 (в виде двоичных последовательностей) вводятся соответственно в регистры сдвига 5 п 7, а также поступают на блок определения знака и начала пакета ошибок 11, где определяется знак арифметического naKei-a ошибок, причем сигнал об атом подается с блока управления 4 на блок коррекции 3. Начиная со второго такта содер га мое регистров сдвига 5 и 7 циклнчсч:ки сдыи аотся вправо до тех пор, пока: в нулевь;х разрядах Регкс сдвага не будут стоять символы 2)нен левые символы не буд;/т сгоягь только 3 млад:иих разряд.ах 6,,.,.,6 и 8,, ,..., 8 регистров сп-,ига, 3)не совпадет содерх« 1 мое младших разрядов О; сдвига, что фикси1луется Слоком сравгге-i ния 10, При згом количество сдв;{гов в регисГ. pax сдвига подсчигьшае1х;я в б/юке опреде ления знака и начала пакета ошибок 11„ Как только блоки Ю и 2 одновременно зафшссир /юг oHHcaiHibie вынде три ситуации, сигнал с блока анализа пакета оиЛ5бок 2 поступает на блок уггравления 4, по сшнаяу которого, иоданному на блок коммутации 9, прекраишютгя циклические сдвиги регис ГРОБ сдвит а, а содержимое регистра сдвига 5 заносится в блок коррекции 3. Кроме того, по сигналу с блока управления 4 в блоке определения знака и начала оигибок 11 вычисляется начало пакета ошибок, Эга величина иосгупает в блок коррекции 3, где исправляется искаженная последовательность а . Блок определения знака и начала пакета ошибок 11 работает следующим обраэом, С блока В1 гИ1слон)гя остатков I к блока комглуташп ) Т Т 2 ИГ.СТу ijafOT COOT- 11 1 ., и кото- Ben.TBftHfio на Ч(

рых подсчитывается количество единии в двоичных представлениях Т и Т j, . ficnn спцержимое счетчиков совпадает, чгс ф1 сксируется узлом сравнения 14, знак арифметического пакета ошибок- поло 1 ительный, в п{Х)тивном случае-отрицатель11ЫН (соответствующий сигнал с узла сравнения 14 через блок управления 4 поступает на блок коррекции 3). Далее содержимое счетчиков сбрасывается, и в них подсчитывается число сдвигов в регистрах сдвига 5 и 7, причем сигналы поступают на другие входь счетчиков 12 и 13 (пусг числа сдвигов соответственно равны Ij и i ,, . После прекращения циклических сдрлп ов в регистрах сдвига содержимое счетчиков 12 и 13 поступает в узел определения начала пакета ошибок 15, где вычисляется начало пакета ошибок в виде:. ..

2C.| II + GJ-II mod и ,

где Cf irnod pj,C 50modp2f-2- О mod р, С modpj

Затем величина i поступает на блок коррекции 3, где исправляется искаженная последовательность (числа) виде:

oi-Q -() .,

где е - величина арифметического пакета ошибок; 5{йп е - знак арифметического пакета

ошибок.

Обшее количество тактов при декодировании не пРевышаог М () + р2-Ь- i , где

При этом выполняется

М-lPt-btl. неравенство М ( Ь) t р - b +1 2р. - Ъ .

Формула изобретения

1, Устройство для декодирования циклических А N -кодов, исправляющих одиночные пакеты ошибок, содержащее блок вычисления остатков, блок анализа пакета ошибок, блок коррекции и блок управления, о тли чающееся TeN), что, с целью повышения его быстродействия, в схему введеньг регистры сдвига, блок коммутации, блок сравнения, блок определения знака и начала пакета ошибок, при этом выход блока вычисления остатков ч«

рез блок коммлТации, младшие разряды регистров сдвига, блок сравнения, анализа пакета ошибок и блок управления подключен к первому входу блока копоек- дни, к другому входу которого через блок

определения знака и начала пакета ошибок соединенный со вторым выходом блока управления, подключен соответствующий выход блока коммутации, ко BTopoNiy, третьему и четвертому входам которого соот ветственно подключены третий выход блока управления, ко второму входу которого подключен второй выход блока определения знака и начала пакета ошибок, и нулевые разряды регистров сдвига, выходы всех

разрядов которых подключены к соответствующим входам блока анализа пакета ошибок, при этом к третьему входу блока коррекцн подключен соответствующий выход блока коммутации, к пятому входу которого под|ключен вход блока вычисления остатков.

2. Устройство поп. 1, огличак щ е е с я тем, что блок определения знака и начала пакета ошибок состоит из счет чиков, выходы которых подключены соответственно ко входам узла сравнения и узла определения начала пакета ошибок.

Источники информации, принятые во ьни мание при экспертизе:

1. Путинцев Н, Д. Аппаратурный контроль управляющих цифровых вычислительных машин. М., Сов. радио, 1966, с. 108-118.

Фиг. /

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления пакетов ошибок | 1975 |

|

SU562931A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для декодирования пакетных ошибок | 1984 |

|

SU1185614A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Декодирующее устройство для исправления пакетных ошибок | 1985 |

|

SU1293845A1 |

| Устройство кодирования-декодирования числовых последовательностей | 1990 |

|

SU1809541A1 |

| УСТРОЙСТВО ПРИЕМА ИНФОРМАЦИИ ИЗ КАНАЛА | 1998 |

|

RU2137320C1 |

| Вычислительное устройство для определения параметров нестационарных стохастических объектов | 1978 |

|

SU746543A1 |

| Устройство декодирования с исправлением ошибок | 1985 |

|

SU1293855A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

12

/J

Авторы

Даты

1977-06-05—Публикация

1973-07-18—Подача