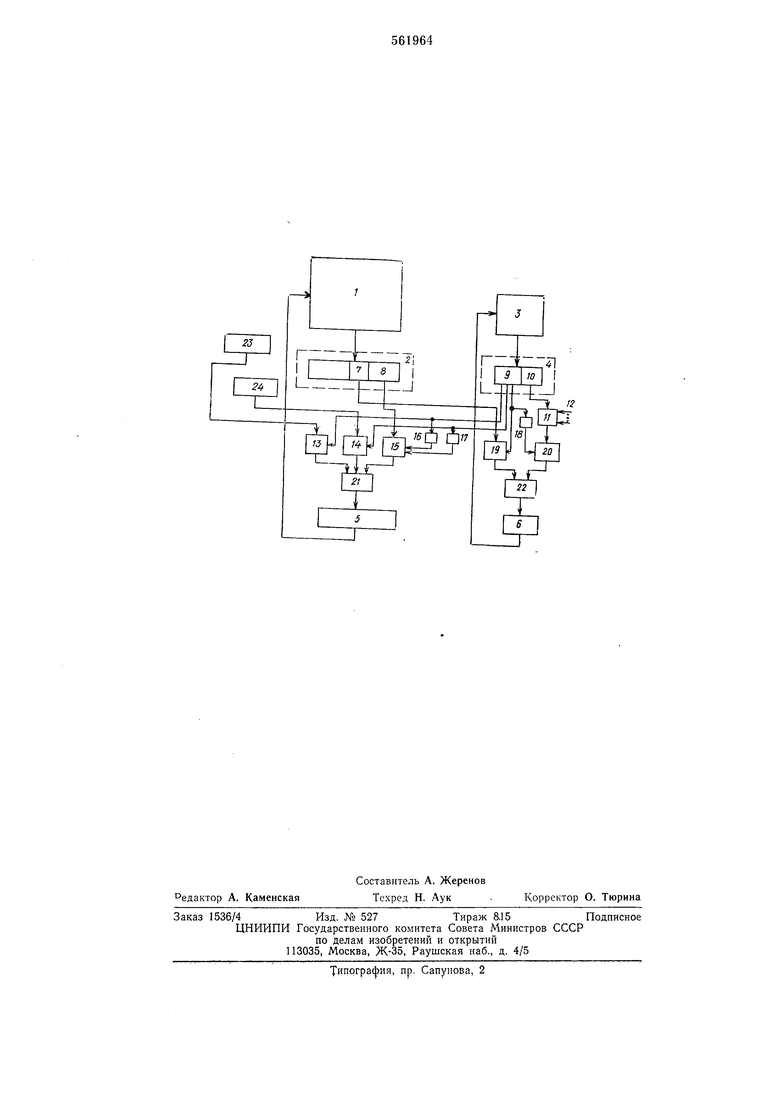

команды, узел модификации адреса, управляющий вход которого подключен к управляющему входу устройства, выходы блоков основной и дополнительной памяти микропрограмм подключены соответственно «ко входам )егистра основной микрокоманды и регистра дополнительной микрокоманды, выходы трех групп элементов И через последовательно соединенные первую группу элементов ИЛИ и первый регистр адреса соединены со входом блока основной памяти микропрограмм, первые входы первой группы элементов И соединены с выходом регистра кода операции первой команды, вторые входы - с первым щыходом регистра дополпителыюй микрокоманды, первые входы второй группы элементов PI соединены с выходом регистра кода операции второй команды, вторые .входы - со вторым выходом регистра дополнительной микрокоманды, первые входы третьей группы элементов И соединены с первым выходом регистра основной микрокоманды, а вторые и третьи входы через первую и вторую группы элементов НЕ подключены соответственно к первому и второму выходам регистра дополнительной микрокоманды, выходы четвертой и пятой групп элементов PI через последовательно соединенные вторую группу элементов ИЛИ и второй регистр адреса соединены со входом блока дополнительной намяти микропрограмм, первые входы четвертой группы элементов И соединены со вторым выходом регнстра основной микрокоманды, вторые входы - с третьим выходом регистра дополнительной микрокоманды, первые входы пятой группы элементов И подключены через узел модификации адреса к четвертому выходу регистра дополнительной микрокоманды, вторые входы через третью группу элементов НЕ соединены с третьим выходом регистра дополнительной микрокоманды. На чертеже показана блок-схема предлагаемого устройства. Устройство содержит блок 1 основной памяти микропрограмм, регистр 2 основной микрокоманды; блок 3 дополнительной памяти микропрограмм, регистр 4 дополнительной микрокоманды, регистры 5, 6 адреса, поле констант 7 н поле базового адреса 8 основной микрокоманды, поле тактов 9 и поле базового адреса 10 дополнительной микрокоманды, узел 11 модификации адреса, входы 12 устройства, группы элементов И 13, 14, 15, группы элементов НЕ 16, 17, 18, группы элементов PI 19, 20, группы элементов ИЛИ 21, 22, регистр 23 кода операции первой команды и регистр 24 кода операции второй комаиды. Устройство обеспечивает обработку системы команд типа принятых IB вычислительной системе ЕС ЭВМ. Описание работы устройства удобно производить на примере выполнения команд формата RX типа сложения с фиксированной запятой, как наиболее широко используемых. Все остальные команды по этапам обработки МОЖ1НО свести к командам этого типа н)тем удлинения соответствующих этанов за счет включения дополнительных мащинных циклов илн исключения некоторых этапов. Рассмотрим все этапы обработки, которые проходит эта команда в процессоре. Выполнение ее занимает шесть циклов работы процессора. Эти циклы называют тактами обработки команды и обозначают буквой Т с соответствующим номером: Т1 - такт распаковки команды, т. е. выборки комапды из буфера команд и чтения модификаторов адреса из местной памяти; 12--такт модификации адреса; ТЗ-такт запроса за операндом в оперативную (буферную) память; Т4 - такт выборки операндов из местной илн онеративиой памяти; Т5 - такт выполнения действий над операндами;Т6 - такт записи результата в местную память. Таким образом, для управления выполнением одной команды из блока памяти микронрограмм нужно выбрать последовательность (микропрограмму) из щести микрокоманд. Для выполнения другой команды требуется другая микропрограмма из щести микроманд и т. д. Обычно выбор первой микрокоманды из микропрограммы производится путем использования кода операции, как части адреса ячейки намяти, где хранится первая микрокоманда. Для устранения дублирования одинаковых микрокоманд, используемых в разных микропрограммах, в устройстве производится переход на общие микрокоманды из разных точек микропрограмм, обеспечивающих выполнение системных команд. Возвращаясь к щести тактам выполнения операций, переходы к общим точкам в общей микропрограмме выполнения всех операций выполпяются следующим образом. Микрокоманда первого такта Т1 является общей для всех команд. Количество микрокоманд второго такта Т2 равно количеству команд в системе. Таким образом, переход из микрокоманды Т1 на микрокоманду Т2 происходит по коду операции. Действия, выполняемые в третьем такте, одинаковы для нескольких команд. Эти команды объединяются в группу, имеющую свой код, который указывается (в микрокоманде Т2 данной команды. Ири переходах из микрокоманд Т2 на микрокоманды ТЗ этот код группы используется как часть адреса микрокоманды. Количество микрокоманд ТЗ равно количеству груни. Но общим микрокомандам ТЗ названную вьиие систему команд можно разделить на 20-25 групп. Из нескольких микрокоманд ТЗ по адресу, находящемуся в поле базы микрокоманды, производится переход на одну микрокоманду Т4, так как микрокоманд Т4 меньше, чем ТЗ.

Для выбранной системы команд можно выделить 15 микрокоманд Т4. Действия в пятом такте зависят от кода операции системной команды и поэтому при переходе из микрокоманды Т4 на Т5 код операции используется как часть адреса микрокоманды. Количество микрокоманд Т5 равно количеству команд в системе. В командах, требующих более одного такта выполнения, первая микрокоманда Т5 является началом последовательности нескольких микрокоманд типа Т5. Микрокоманда Т6 является общей для всех команд.

При выполнении трех команд в 5-6 циклах процессора (при совмещенном выполнении трех команд) команда КЗ будет находиться на первом уровне совмещения, команда К2 на втором, а команда К1 «а третьем уровне совмещения.

Для управления выполнением этих команд необходимо выбрать три последовательности микрокоманд или одну последовательность, управляющую всеми тремя командами, находящимися на разных стадиях обработки.

Трудности при организации одной последовательности возникают из-за сложности организации переходов в микропрограмме, т. е. сложности формирования адреса следующей микрокоманды. В предлагаемом устройстве эти трудности ликвидируются путем разделения функций управления между двумя блоками памяти микропрограмм следующим образом.

Действия, общие для всех команд, которые связаны лин1ь с номером такта выполнения, управляются микрокомандами блока 3 дополнительной памяти микропрограмм, а действия, зависящие от кода операции, управляются микрокомандами блока 1 основной памяти микропрограмм, т. е. последовательность микрокоманд для управления выполнением команд разбивается на две последовательности, выбираемые из двух синхронно работающих блоков 1, 3.

Функции управления, зависящие от тактов обработки команды, выполняются микрокомандами блока 3. Для управления двумя или тремя командами выбирается одна микрокоманда, имеющая признаки тактов этих команд. Функции управления, зависящие от кода онерации, производятся микрокомандами блока 1.

Микрокоманды (типа М) управляют модификацией адреса операнда. Микрокоманды (типа ОП) управляют выполнением операции.

Пусковые микрокоманды (ПК), т. е. непроизводящие никаких действий, кроме перехода, используются при входах и выходах из совмещенного режима выполнения команд для сохранения непрерывности в работе памяти микропрограмм.

Исходя из вышеизлол :енного, для управления выполнением трех команд нужно выбрать две последовательности микрокоманд из блоков 1 и 3.

Разделение управления между двумя последовательностями микрокоманд позволяет упростить схему микропрограммных переходов.

Переход на следующею микрокоманду в блоке 3 зависит от номера такта обработки команды. Через каждые два такта начинается новая последовательность, т. е. начинается выборка микрокоманд, управляющих совмеnteHHbiMi тактами. Переходы в блоке 1 осноБной памяти микроирограмм на микрокоманды типа М производятся по коду операции команды, находящейся на первом у ровне совмещения, а на микрокоманды типа ОП - по коду операции команды, находящейся на третьем уровне совмещения. Переходы в длинных последовательностях микрокоманд типа ОП происходят по базовому адресу, находяитемуся в поле выполняемой микрокоманды. В структуре процессора суи1ествуют

дополнительные схемные условия, которые определяют одно из четырех направлений перехода.

Для сокращения времени такта процессора, а следовательно повыщения быстродействия,

схемные условия перехода не учитываются при формировании адреса. Ветвление на четыре направления производится нутем разбиения блока 1 основной памяти мпкропрограмм на четыре независимых модуля, обраиленпе к которым происходит одновременно по одному базовому адресу. Время выборки из модулей используется для анализа схемных условий и формирования сигнала приема из соответствующего модуля памяти на регистр 2 основной микрокоманды.

Организацию переходов в микропрограммах основной н дополнительной памятп можпо проследить при выборке двух последовательностей мпкрокоманд для управления обработкой трех команд.

Па первую микрокоманду Т1 процессор выходит после завершения операций по загрузке системных команд в буфер команд.

Пз блока 1 выбирается «пустая команда, так как процессор еще не вошел в режим совмещения. Переход из Т1 на Т2 происходит по базовому адресу, который из поля 10 через узел И, группы элементов П 20 и 1-1ЛП 22

подается на регистр 6. Переход на микрокоманду типа М для команды К1 происходит путем подачи кода операции команды К1, находящейся на первом уровне совмещения. Хранящийся на регистре 23 код операции через группы элементов И 13 и ПЛИ 21 подается на регистр 5 адреса. Элемеиты И 13 управляются сигналом Т1 iH3 поля тактов 9 регистра 4.

Переход из микрокоманды М для К1 на

микрокоманду ПК происходит по базовому адресу, который из поля 8 регистра 2 через группы элементов И 15 и ИЛИ 21 поступает на регистр 5 адреса. Иа второй и третий входы подаются пнвер ные управляющие сигналы Т1 и Т4. Переход из микрокол1анды Т2 на совмещенную микрокоманду Т13 нроисходит по коду группы, поступающему из поля 7 регистра 2 через группы элементов И 19 и Р1ЛИ 22 на регистр 6 адреса. На второй вход элементов И 19 подается сигнал признака такта Т2. Переход из Т13 в совмещенную микрокоманду Т24 происходит по базовому адресу, который через группы элементов И 20 и ИЛИ 22 поступает на регистр 6, как было описано выще, а переход из ПК на М для команды К2 происходит с помощью кода операции команды К2, которая теперь находится на первом уровне совмеп ения, а ее код на регистре 23. Команда К1 уже находится на втором уровне совмещения, а ее код операции .хранится в регистре 24. Формирование адреса микрокоманды по коду системной команды, находящейся на первом уровне совмещения, был описан выше. Образование переходов в последующих микрокомандах организуется аналогично выщеопнсапным. Оба блока 1, 3 памяти микропрограмм работают сихронно, вырабатывая сигналы для управления выполнением системных команд на всех этапах обработки. Управляющи(1 сигналы блока 3 дополнительпой памяти г/гикропрограмм влияют на организацию микропрограммных переходов и основпой памяти, а код группы команд, находящейся в микрокоманде блока I основной памяти микрошро рамм используется для переходов в микропрограммах блока 3 дополнительной памяти микропрогра.мм. Такил образом, устройство позволяет производить в процессоре одновременную обработку трех команд, т. с. допускает три уровня совмещения, что значительно увеличи1вает производительность системы и повышает эффективность использования оборудования. KifOMe того, использованием общих микрокоманд можно сократить общий объем памяти микропрограмм на 15-20%, т. е. уменьщить оборудование процессора. Формула изобретения Микропрограммное устройство управления, содержащее группы элементов И, ИЛИ, ПЕ, блоки основной памяти микропрограмм и дополнительной памяти микропрограмм, отличающееся тем, что, с целью уменьшения оборудования и времени обработки команд, оно содержит первый и второй регистры адреса, регистры кода операции первой команды и второй команды, регистры основной микрокоманды и дополнительной микрокоманды, узел модификации адреса, управляющий вход которого подключен к управляющему входу устройства, выходы блоков основной и дополнительной памяти микропрограмм подключены соответственно ко входам регистра основной микрокоманды и регистра дополнительной микрокоманды, выходы трех групп элементов И через последовательно соединенные первую группу элементов Р1ЛИ и первый регистр адреса соединены со входом блока оС новной памяти микропрограмм, первые входы первой группы элементов И соединены с выходом регистра кода операции первой команды, вторые пходы - с первым выходом регистра дополнительной микрокоманды, первые входы второй грзппы элементов И соединены с выходом регистра кода операции второй команды, вторые входы - со вторым выходом регистра дополнительной микрокоманды, первые входы третьей группы элементов И соединены с первым выходом регистра основной микрокоманды, а вторые и третьи входы через нервую и вторую группы элеметов НЕ подключены соответственно к первому и вто)ому выходам регистра дополнительной микрокоманды, выходы четвертой и пятой групп элементов И через последовательно соединенные .вторую группу элементов ИЛИ и второй регист|) ад)еса соединены со входом блока дополнительной памяти микропрограмм, пер|;ые входы четвертой группы элементов И соединены со вторым выходом регистра основной микрокоманды, вторые входы -- с третьим выходом регистра дополнительной микрокоманды, первые входы пятой группы эле.ментов И подключены через узел модификации адреса к четвертому выходу регистра дополнительной микрокоманды, вторые входы - через третью группу элементов НЕ соединены с третьим выходом регистра дополнительной микрокоманды. Источники информации, принятые во впимание при экспертизе: 1- С. Хассон, Микропрограммное управление, вып. 1, 2 М., «Мир, 1973 г. 2. Патент США ЛЬ 3800293, кл. 340-172.5, 26.03.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1980 |

|

SU942020A1 |

| Микропрограммное устройство управления | 1980 |

|

SU940158A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для сопряжения памяти с процессором | 1982 |

|

SU1136176A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для сопряжения канала ввода-вывода с внешними устройствами | 1977 |

|

SU656050A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Вычислительное устройство с совмещением операций | 1989 |

|

SU1716528A1 |

Авторы

Даты

1977-06-15—Публикация

1975-09-19—Подача