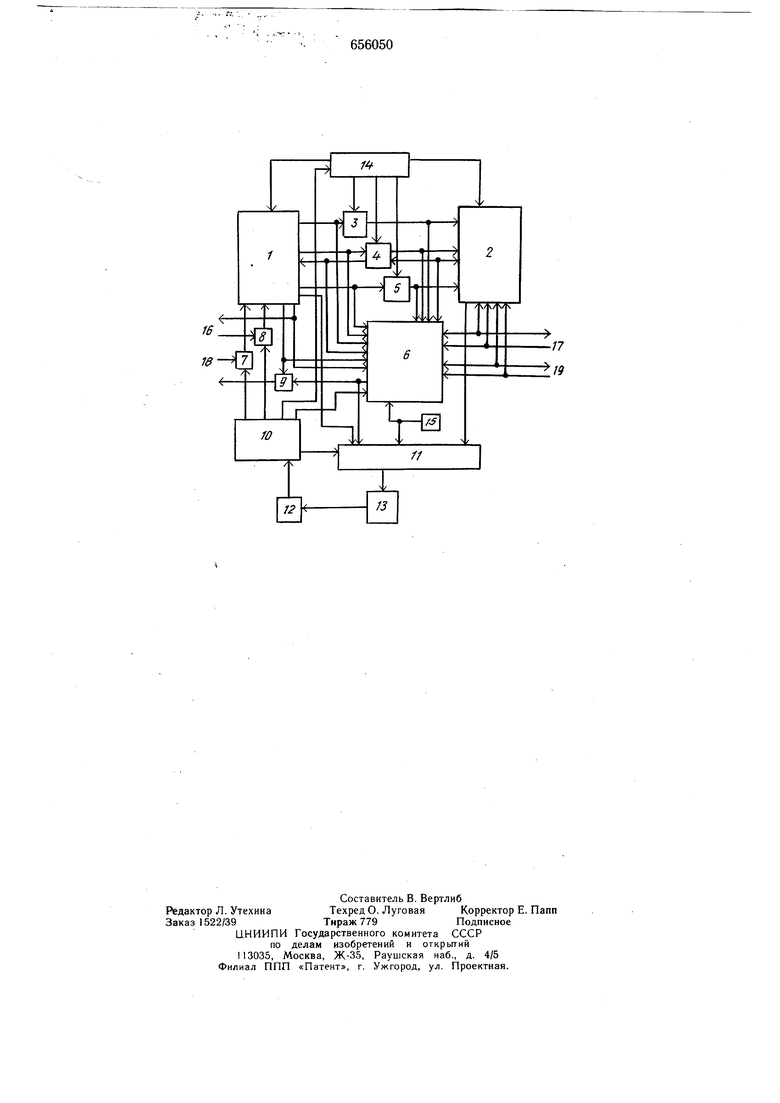

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных системах для сопряжения внешних устройств (ВУ) с каналом ввода-вывода (КВВ). Известны устройства 1 для сопряжения ЦВМ с ВУ, содержащие регистр связи, блок адреса, блок анализа, буферный блок, регистры управляющих слов и блок модификации адресов и выполняющие функции сопряжения между процессором и ВУ. Функциональные возможности этих устройств ограничены, так как они не позволяют осуществить текстовый контроль без использования процессора ЦВМ. Наиболее близким по технической сущнести к изобретению является процессор связи 2, содержащий память микропрограммы, соединенную через регистр микрокоманд со входом дешифратора микрокоманд, первый и второй выходы которого подключены соответственно ко входу формирователя управляющих сигналов и первому входу формирователя адреса микрокоманды, выходом соединенного со входом памяти микропрограмм, а вторым входом - с выходом генератора тактов и управляющим входом схемы сравнения. Недостатком такого устройства являются ограниченные функциональные возможности, так как оно не позволяет осуществлять непосредственный контроль работы устройства сопряжения и ВУ, а также низкое быстродействие устройства при выполнении программы контроля. При контроле информация поступает на ЦВМ, поэтому процесс проверки проводится не оперативно и выполняется в течение длительного интервала времени. Целью изобретения является расширение функциональных возможностей путем реализации режима автономной проверки устройства для сопряжения и ВУ и повышение быстродействия работы системы контроля. Поставленная цель достигается тем, что в предложенное устройство введены регистр команд, регистр данных, регистр адреса, три элемента ИЛИ, узел согласования с КВВ и узел согласования с ВУ. Первый, второй и третий выходы узла согласования с КВВ соединены соответственно с входами регистра команд, регистра адреса и первым входом регистра данных, управляющие входы которых подключены соответственно к первому, второму и третьему выходам формирователя управляющих сигналов, соединенному четвертым выходом с синхронизирующим входом узла согласования с КВВ - информационный и управляющие входы которого соответственно подключены к выходам первого и второго элементов ИЛИ, соединенных первыми входами соответственно с третьим и четвертым выходами дещифратора микроком-анд, а вторыми входами - соответственно с первыми информационным и управляющим входом устройства. Вход и информационный и управляющий выходы узла согласования с КВВ подключены соответственно к первому выходу регистра данных, первым входам третьего элемента ИЛИ и схемы сравнения и второму входу схемы сравнения и первому управляющему выходу устройства. Второй вход третьего элемента ИЛИ соединен с выходом схемы сравнения и вторым входом формирователя адреса микрокоманд, третий вход которого подключен к адресному выходу узла согласования с КВВ а четвертый вход - с адресным выходом узла согласования с ВУ первый, второй и третий входы и выход которого подключены соответственно к выходам регистра команд, регистра адреса и вторым выходу и входу регистра данных, синхронизирующий вход - к пятому выходу формирователя управляющих сигналов, а управляющие и информационные входы и выходы, являющиеся соответственно вторыми управляющими входом и выходом устройства и вторыми информационными входом и выходом устройства, подключены к соответствующим входам первой группы входов схемы сравнения, ко второй группе входов которой подключены соответственно выходы и входы регистра команд, регистра данных и регистра адреса. Пятый выход дещифратора микрокоманд соединен с третьим входом схемы сравнения. На чертеже представлена структурная схема устройства. Оно содержит узел 1 согласования с КВВ, узел 2 согласования с ВУ, регистр 3 команд, регистр 4 данных, регистр 5 адреса, схему 6 сравнения, первый 7, второй 8 и третий 9 элементы ИЛИ, дещифратор 10 микрокоманд, формирователь 11 адреса микрокоманд, регистр 12 микрокоманд, память 13 микропрограммы, формирователь 14 управляющих сигналов, генератор 15 тактов, первые 16 и вторые 17 управляющие входы и выходы устройства, первые 18 и вторые 19 информационные выходы устройства. Узлы 1 и 2 служат для согласования устройства при обмене информацией соответственно с КВВ и ВУ и имеют конструкцию аналогичную конструкции устройств, описанных в 3. Устройство работает следующим образом. При выполнении основной программы обмена между ЦВМ и ВУ, процессор выдает в канал команду ввода-вывода (например, «Начать ввод/вывод), в которой указаны номер канала и номер ВУ. Этот КВВ производит выборку из памяти адресного слова канала и командного слова канала, в которых указаны массив данных, подлежащий передаче, начальный адрес массива и код операции ввода/вывода. КВВ разворачивает последовательность сигналов интерфейса ввода/вывода, в ходе которой осуществляется непосредственный обмен информацией между КВВ и устройством. Для этого по входу 16 выдаются управляющий сигнал в узел 1, который выдает запрос на формирование адреса микрокоманды в формирователь 11, вырабатывающий непосредственный адрес микрокоманды в соответствии с сигналами генератора 15. По этому адресу считывается память 13, и содержимое записывается в регистр 12 и на вход дещифратора 10, где отдельные поля микрокоманд декодируются и управляющая информация поступает на формирователь 14, а затем в узел 1, который выдает в соответствии с принятой процедурой обмена сигнал управления по выходу 16 в КВВ. КВВ в ответ на этот сигнал выдает информацию на вход 18, сопровождая ее сигналом управления по входу 16. Через элемент ИЛИ 7 информация поступает в узел 1. Формирователь И производит выборку следующей микрокоманды по сигналу от дещифратора 10, который, декодировав предыдущую микрокоманду, определил адрес следующей. Получив новую микрокоманду и декодировав ее, дещифратор 10 и формирователь 14 выдают сигналы управления в регистры 3, 4 и 5 на запись информации, находящейся на входе 18. Получив от дешифратора 10 следующую микрокоманду, формирователь 14 выдает сигнал в узел 2, по которому из регистров 3, 4 и 5 информация поступает на выход 19 и сопровождается сигналом управления на выходе 17. ВУ, получив эти сигналы, выдает ответный управляющий сигнал на вход 17 и узел 2. Последний в ответ на него выдает в формирователь 11 сигнал формирования следующего адреса микрокоманды и т.д. Информация из ВУ в КВВ передается аналогично. При получении от КВВ команды «Тест, которая записывается в регистр 3, узел 1 вырабатывает начальный адрес исполнения микрокоманды «Тест и инициирует чтение памяти 13, после чего в регистре 12 оказывается запращиваемая микрокоманда. Дещифратор 10 выдает соответственно информационную и управляющую тестовые последовательности, имитирующие сигналы КВВ, При этом устройство вводит в ВУ тестовую последовательность, получая из ВУ соответствующие реакции. При этом процессор и КВВ освобождаются от работы с устройством, а по окончании режима проверки информация о состоянии передается в КВВ по прерыванию. Наряду с тестовыми сигналами дешифратор формирует опорную тестовую последовательность, которая подается на схему сравнения 6. Сравнение отдельных кодов тестовой последовательности с состоянием входов регистров 3, 4 и 5 происходит по тактовому импульсу, получаемому от генератора 15. Результаты сравнения хранятся в схеме сравнения 6. По следующей микрокоманде производится сравнение состояний входов и выходов регистров 3, 4 и 5 и кода опорной последовательности. Далее по следующей микрокоманде осуществляется сравнение опорных кодов с сигналами на входах и выходах узла 2, узла 1 и т. д. После заверщения проверки устройства и ВУ на выходе схемы сравнения 6 формируется адрес микрокоманды на прерывание КВВ, и на выход 18 устройства подается информация о состоянии ВУ и устройства. При появлении ощибок (отклонение при сравнении сигналов в схеме 6 из памяти 13) вызывается микропрограмма обработки ошибок. В результате отключается либо неиснравное ВУ, либо устройство в целом. Предложенное устройство позволяет проводить проверку самого устройства для сопряжения и ВУ в автономном режиме и при значительно больщих скоростях, чем известные устройства. Формула изобретения Устройство для сопряжения канала ввода-вывода с внешними устройствами (ВУ), содержащее память микропрограммы, соединенную через регистр микрокоманд со входом дешифратора микрокоманд, первый и второй выходы которого подключены соответственно ко входу формирователя управляющих сигналов и первому входу формирователя адреса микрокоманды, выходом соединенного со входом памяти микропрограмм, а вторым входом - с выходом генератора тактов и управляющим входом схемы сравнения, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет реализации режима автономной проверки ВУ в устройство введены регистр команд, регистр данных, регистр адреса, три элемента ИЛИ, узел согласования с каналом ввода-вывода и узел согласоваНИИ с ВУ; причем первый, второй и третий выходы узла согласования с каналом вводавывода соединены соответственно со входами регистра команд, регистра адреса и первым входом регистра данных, управляющие входы которых подключены соответственно к первому, второму и третьему выходам формирователя управляющих сигналов, соединенному четвертым выходом с синхронизирующим входом узла согласования с каналом ввода-вывода, информационный и управляющие входы которого соответственно подключены к выходам первого и второго элементов ИЛИ, соединенных первыми входами соответственно с третьим и четвертым выходами дешифратора микрокоманд, а вторыми входами - соответственно с первыми информационными и управляющим входом устройства, вход и -информационный и управляющий выходы узла согласования с каналом ввода-вывода подключены соответственно к первому выходу регистра данных, первым входам третьего элемента ИЛИ и схемы сравнения и второму входу схемы сравнения и первому управляющему выходу устройства, второй вход третьего элемента ИЛИ соединен с выходом схемы сравнения и пятым входом формирователя адреса микрокоманд, третий вход которого подключен к адресному выходу узла согласования с каналом ввода-вывода, а четвертый вход - с адресным выходом узла согласования с ВУ первый, второй и третий входы и выход которого подключены соответственно к выходам регистра команд, регистра адреса и вторым выходу и входу регистра данных, синхронизирующий вход - к пятому выхоДу формирователя управляющих сигналов, а управляющие и информационные входы и выходы, являющиеся соответственно вторыми управляющими входом и выходом устройства и вторыми информационными входом и выходом устройства, подключены к соответствующим входам первой группы входов схемы сравнения, ко второй группе входов которой подключены соответственно выходы и входы регистра команд, регистра данных, и регистра адреса, пятый выход дешифратора микрокоманд соединен с третьим входом схемы сравнения. Источники информации, принятые во внимание при экспертизе: 1. Авторское свидетельство СССР № 404088, М., кл. G 06 F 9/19, 1970. 2. Авторское свидетельство СССР № 526899, М., кл. G 06 F 15/00, 1971. 3. Авторское свидетельство СССР № 503232, М., кл. G 06 F 3/04, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля канала ввода-вы-ВОдА ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU840869A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1986 |

|

SU1381521A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для сопряжения | 1978 |

|

SU750474A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Адаптер канал-канал | 1985 |

|

SU1259276A1 |

| Устройство для интерпретации выражений языков программирования | 1982 |

|

SU1078432A1 |

| Микропрограммное устройство управления | 1977 |

|

SU746516A1 |

Авторы

Даты

1979-04-05—Публикация

1977-12-06—Подача