И, первые входы четвертого и пятого элементов Pi - к управляющей шине приема второго чиела, вторые входы - соответственно к шине приема прямого и обратного кода соответствующего разряда второго числа, третьи входы - соответственно к нулевому и единичному выходам триггера суммы, первые входы шестого и седьмого элементов И подсоединены соответственно к пулевому и единичному выходам триггера слагаемого, вторые входы - соответственно к единичному выходу триггера суммы и входу переноса из предыдущего разряда, третий вход шестого элемента И - к управлящей шине стробированпя переноса, выходы шестого и седьмого элементов И соединены с входами пятого элемента ИЛИ, выход которого является выходом перноса в последующий разряд.

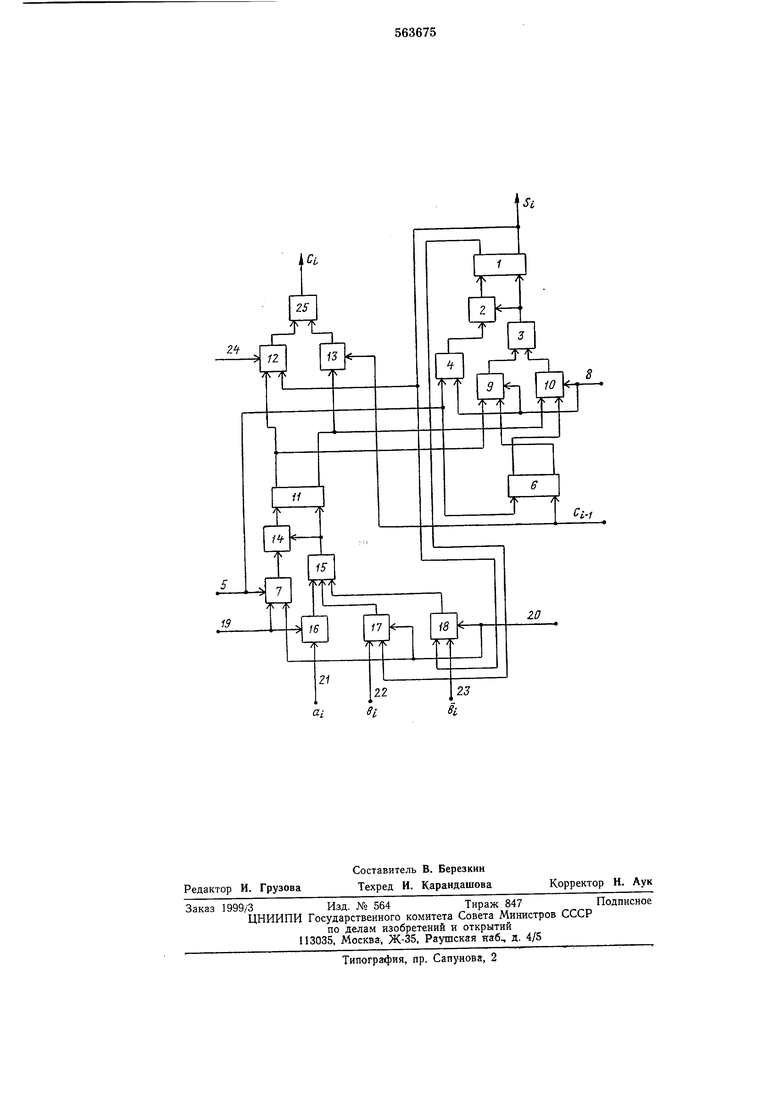

На чертеже представлена схема одного разряда сумматора.

Единичный вход триггера 1 суммы соединен с вторым входом управляемого элемента НЕ 2 и с выходом элемента ИЛИ 3, нулевой вход триггера суммы - с выходом элемента НЕ 2. Первый вход управляемого элемента НЕ 2 связан с выходом элемента ИЛИ 4, первый вход элемента ИЛИ 4 - с управляющей щиной 5 установки в нуль, с нулевым входом триггера 6 переноса и с первым входом элемента ИЛИ 7. Второй вход элемента ИЛИ 4 соединен с управляющей шиной 8 стробирования суммы и с первыми входа(МИ элементов И 9 и 10. Выходы элементов И 9 и 10 подключены соответственно к первому и второму входам элемента ИЛИ 3. Второй вход элемента И 9 соединен с пулевым выходом триггера 11 слагаемого и с вторым входом элемента И 12, третий вход элемента И 9 - с единичным выходом триггера 6 переноса. Второй вход элемента И 10 связан с единичным выходом триггера И слагаемого и с вторым входом элемента И 13, третий вход элемента И 10 - с нулевым выходом триггера 6 переноса. Нулевой вход триггера И слагаемого соединен с выходом управляемого элемента НЕ 14, первый вход элемента НЕ 14 - с выходом элемента ИЛИ 7.

Единичный вход триггера 11 слагаемого подключен к второму входу управляемого элемента НЕ 14 и выходу элемента ИЛИ 15, первый, второй и третий входы элемента ИЛИ 15 - соответственно к выходам элемента И 16, элемента И 17 и элемента И 18. Второй вход элемента ИЛИ 7 соединен с первым входом элемента И 16 и с управляющей шиной 19 приема первого числа, третий вход элемента ИЛИ 7 - с первыми входами элементов И 17 и 18 и с управляющей шиной 20 приема второго числа. Второй вход элемента И 16 подключен к шине 21 прямого кода соответствующего разряда первого числа, второй вход элемента И 17 - к нулевому выходу триггера 1 суммы, третий вход элемепта И

17 - к шине 22 прямого кода соответствующего разряда второго числа. Второй вход элемента И 18 соединен с единичным выходом триггера 1 суммы и с третьим входом элемента И 12, третий вход элемента И 18- с шиной 23 инверсного кода соответствующего разряда второго числа, первый вход элемента И 12 - с управляющей шиной 24 стробирования переноса. Выходы элементов И 12 и 13 подключены соответственно к первому и второму входам элемента ИЛИ 25, выход элемента ИЛИ 25 данного разряда является выходом переноса в доследующий разряд.

Нервый вход элемента И 13 соединен с единичным входом триггера 6 переноса данного разряда и с входом переноса из предыдущего разряда.

Сумматор работает следующим образом.

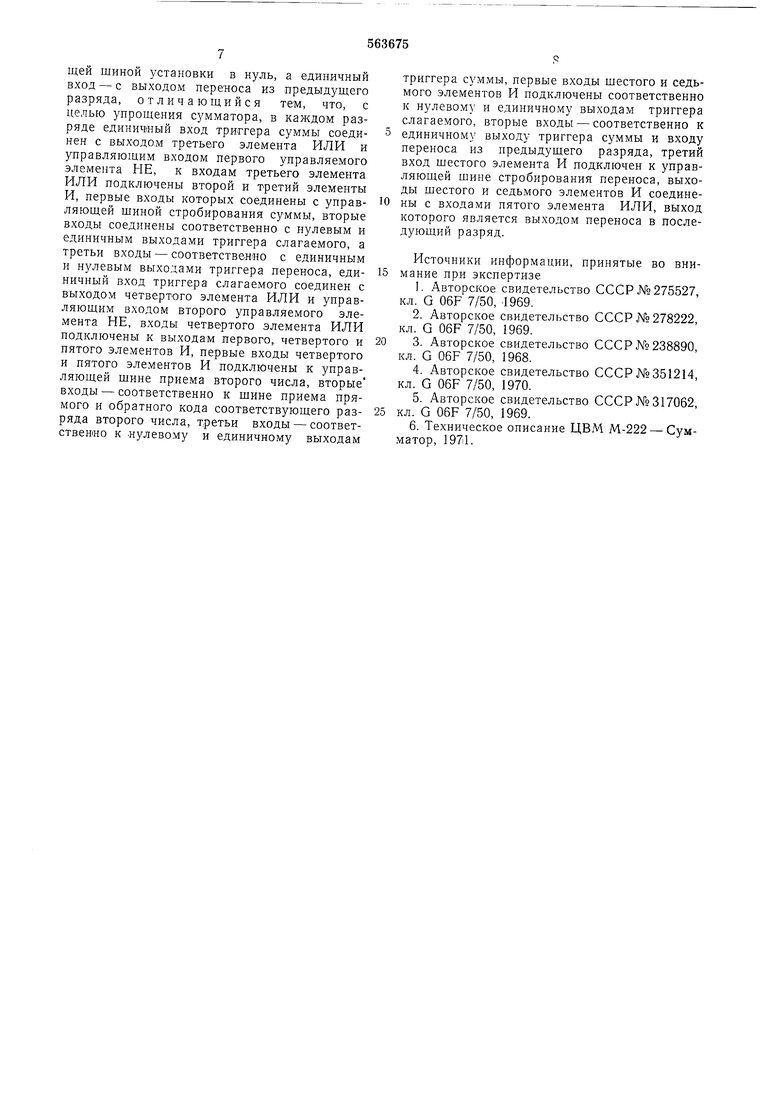

Работу сумматора рассмотрим для случая, когда в данном (i-м) разряде значения цифр слагаемых и значение переноса из предыдущего (I-1-го) разряда следующие: цифра первого слагаемого равна единице (),

цифра второго слагаемого - нулю (), а перенос - единице (). Предварительно отметим следующее: входы триггеров - импульсные, а выходы - потенциальные; входы и выходы схем ИЛИ и схем логической инверсии - импульсные; первые входы и выходы схем И - импульсные, а остальные входы - потенциальные; сигнал на выходе схемы логической инверсии будет только в случае наличия сигнала на первом входе и отсутствия

сигнала на втором входе. Перед суммированием слагаемых сумматор устанавливается в нуль сигналом, поступающим по управляющей шине 5 установки в нуль, т. е. этот сигнал подается на первый вход элемента ИЛИ 7, проходит на выход этой схемы, затем на первый вход элемента НЕ 14, далее на выход этого элемепта, на нулевой вход триггера И слагаемого и устанавливает этот триггер в нулевое состояние (нулевому состоянию соответствует разрешающий потенциал на нулевом вььходе). После этого сигнал поступает на нулевой вход триггера 6 переноса и устанавливает этот триггер в нулевое состояние, затем на первый вход элемента ИЛИ 4, на выход этого элемента, далее он подается на первый

вход элемента НЕ 2, проходит па его выход, затем поступает на нулевой вход триггера 1 суммы и устанавливает этот триггер в нулевое состояние.

В первом такте суммирования по управляющей шине 19 подается сигнал, разрешающий прпем первой цифры через элементы И 16 и элемент ИЛИ .15 на единичный вход триггера 11 слагаемого. Триггер слагаемого устанавливается в единичное состояние, т. е. на его единичном выходе появляется разрешающий потенциал. Во втором такте .по управляющей шине 8 стробироваиия суммы поступает сигнал. Разрешающие потенциалы

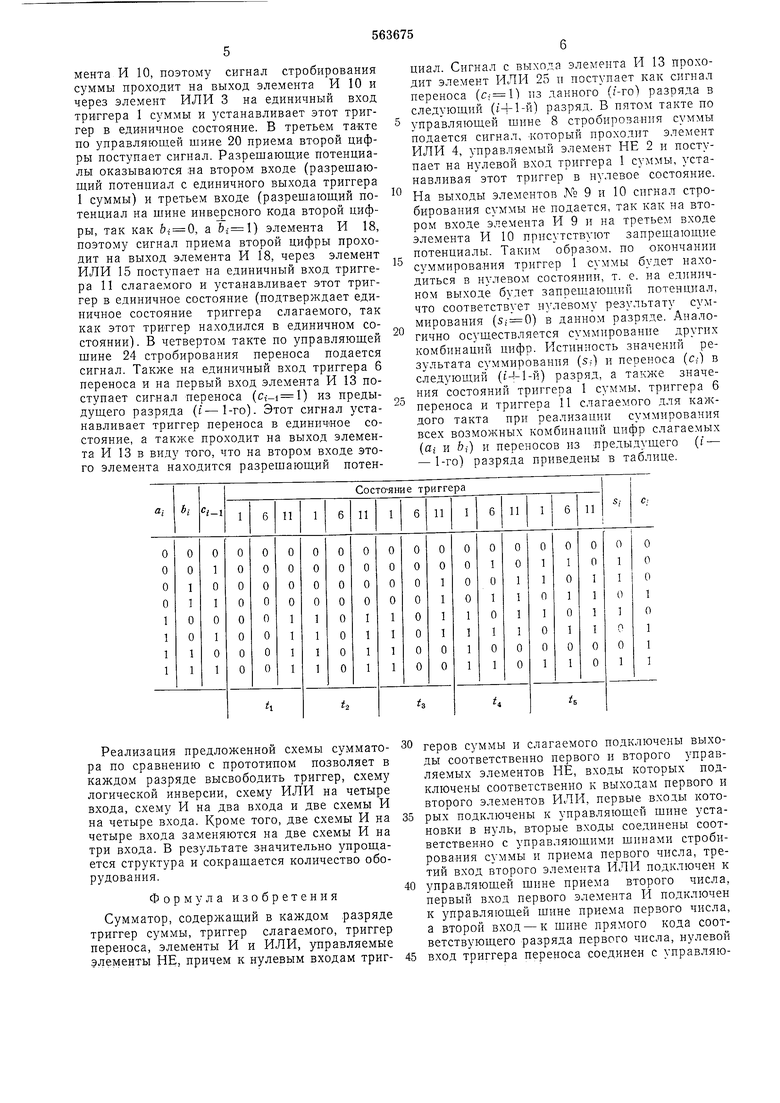

оказываются на втором и третьем входах элемента И 10, поэтому сигнал стробирования суммы проходит на выход элемента И 10 и через элемент ИЛИ 3 на единичный вход триггера 1 суммы и устанавливает этот триггер в единичное состояние. В третьем такте по управляющей шине 20 приема второй цифры поступает сигнал. Разрешающие потенциалы оказываются яа втором входе (разрешающий потенциал с единичного выхода триггера 1 суммы) и третьем входе (разрещающий потенциал на шине инверсного кода второй цифры, так как &i 0, а ) элемента И 18, поэтому сигнал приема второй цифры проходит на выход элемента И 18, через элемент ИЛИ 15 поступает на единичный вход триггера 11 слагаемого и устанавливает этот триггер в единичное состояние (подтверждает единичное состояние триггера слагаемого, так как этот триггер находился в единичном состоянии). В четвертом такте по управляющей щине 24 стробирования переноса подается сигнал. Также на единичный вход триггера 6 переноса и на первый вход элемента И 13 поступает сигнал цереноса (c,) из предыдущего разряда (1-1-го). Этот сигнал устанавливает триггер переноса в единичное состояние, а также проходит на выход элемента И 13 в виду того, что на втором входе этого элемента находится разрешающий потенциал. Сигнал с выхода элемента И 13 проходит элемент ИЛИ 25 и поступает как сигнал переноса (с,) пз данного (г-го) разряда в следующий (i+1-й) разряд. В пятом такте по управляющей шине 8 стробирования суммы подается сигнал, который проходит элемент ИЛИ 4, управляемый элемент НЕ 2 и поступает на нулевой вход триггера 1 суммы, устанавливая этот триггер в нулевое состояние. На выходы элементов № 9 и 10 сигнал стробирования суммы не подается, так как на втором входе элемента И 9 и на третьем входе элемента И 10 присутствуют запрещающие потенциалы. Таким образом, по окончании суммирования триггер 1 суммы будет находиться в нулевом состоянии, т. е. на единичном выходе будет запрещающий потенциал, что соответствует нулевому результату суммирования (Si 0) в данном разряде. Аналогично осуществляется суммирование других комбинаций цифр. Истинность значений результата суммирования (s,-) и переноса (с,-) в следующий () разряд, а также значения состояний триггера 1 суммы, триггера 6 переноса и триггера И слагаемого для каждого такта при реализации суммирования всех возможных комбинатщй цифр слагаемых (а, и bi) и переносов из предыдущего (( - - 1-го) разряда приведены в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Накапливающий сумматор с запоминанием переноса | 1978 |

|

SU943710A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Накапливающий сумматор | 1976 |

|

SU577528A1 |

| Фазо-импульсный сумматор | 1977 |

|

SU651343A1 |

| Устройство для сложения и вычитания чисел в фазо-импульсной форме | 1976 |

|

SU595732A1 |

| Сумматор | 1972 |

|

SU519709A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| Параллельный накапливающий сумматор | 1978 |

|

SU744568A2 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Аналого-цифровой сумматор | 1986 |

|

SU1316006A1 |

Реализация предложенной схемы сумматора по сравнению с прототипом позволяет в каждом разряде высвободить триггер, схему логической инверсии, схему ИЛИ на четыре входа, схему И на два входа и две схемы И на четыре входа. Кроме того, две схемы И на четыре входа заменяются на две схемы И на три входа. В результате значительно упрощается структура и сокращается количество оборудования.

Формула изобретения

Сумматор, содержащий в каждом разряде триггер суммы, триггер слагаемого, триггер переноса, элементы И и ИЛИ, управляемые элементы НЕ, причем к нулевым входам триггеров суммы и слагаемого подключены выходы соответственно первого и второго управляемых элементов НЕ, входы которых подключены соответственно к выходам первого и второго элементов ИЛИ, первые входы которых подключены к управляющей щине установки в нуль, вторые входы соединены соответственно с управляющими шинами стробироваиия суммы и приема первого числа, третий вход второго элемента ИЛИ подключен к

управляющей щине приема второго числа, первый вход первого элемента И подключен к управляющей щнне приема первого числа, а второй вход - к шине прямого кода соответствующего разряда первого числа, нулевой

вход триггера переноса соединен с управляющей шиной Зстановки в нуль, а единичный вход - с выходом переноса из предыдущего разряда, отличающийся тем, что, с целью упрощения сумматора, в каждом разряде единичеый вход триггера суммы соединен с выходом третьего элемента ИЛИ и управляющим входом первого управляемого элемента НЕ, к входам третьего элемента ИЛИ подключены второй и третий элементы И, первые входы которых соединены с управляющей щиной стробирования суммы, вторые входы соединены соответственно с нулевым и единичным выходами триггера слагаемого, а третьи входы - соответственно с единичным и нулевым выходами триггера переноса, единичный вход триггера слагаемого соединен с выходом четвертого элемента ИЛИ и управляющим входом второго управляемого элемента НЕ, входы четвертого элемента ИЛИ подключены к выходам первого, четвертого и пятого элементов И, первые входы четвертого и пятого элементов И подключены к управляющей щине приема второго числа, вторые входы - соответственно к щине приема прямого и обратного кода соответствующего разряда второго числа, третьи входы - соответственио к .нулевому и единичному выходам

триггера суммы, первые входы щестого и седьмого элементов И подключены соответственно к нулевому и единичному выходам триггера слагаемого, вторые входы - соответственно к единичному выходу триггера суммы и входу переноса из предыдущего разряда, третий вход щестого элемента И подключен к управляющей шине стробирования переноса, выходы шестого и седьмого элементов И соединены с входами пятого элемента ИЛИ, выход которого является выходом переноса в последующий разряд.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1977-06-30—Публикация

1974-12-13—Подача