Изобр4;тение относится к области автоматики и вычислительной техники и может быть использована при реализации технически средств аналого-цифровых следящих систем. Известны устройства для сравнения сиг налов многоотсчетных циклических врем импульсных преобразователей с предвар тельным преобразованием их в цифровой коД Известные устройства содержат сумматор, :один вход которого подключен к выходу пре образоват я фаза-код, второй вход - к выходу управляющей ЦВМ, а БЫХОД через блок съема - ко входу управляющего преобразователя код-напряжение ll. Недостатком таких устройств является ограничение на выбор чисел междушкальной редукции преобразователя, .заключающееся в том, о их значения Могут быть равны только степеням числа два. Это ноключает возможность оптимальной новкя их шкал я монотгйшого уменьшения уровня кванта сигнала. Наиболее близким техническим решением к изобретению является многоуровневое уст ройство для сравнения, содержащее преобра зователь временной интервал код, выходы которого через блок выдачи подключены ко входам преобразователя код-напряжение, узел сравнения и группы элементов И 12|. Устройство содержит также сумматор, одни входы которого подключены к выходам пр образователя фаза-код, вторые - к выходам вычислительного устройства, а выход через блок съема - ко входам преобразователя код напряжение. Шкалы этих устройств из-эа необходим мости предварительного преобразования их сигналов в код сопрягаются числами между шкалыюй редукадаи: Pp,g+ 02 , кратными числу 2, где 1, 2, ... ( S - 1)номер шкал, iTp - разрядность щкал. ТЖкое ограничение на значение чисел f|t,g+j исклочает возможность монотонного увеличения общего числа уровней N мноЛщкальных цифровых время-импульсных преобразоватьI NsSlей, посколькуN NS 4 Р,дм|,где - чис ло уровней младшей шкалы. Целью изобретения йвляется повышенте точности работы и расширение диапазона чц«,

сел междушкальной редукции входных величин.

Поставленная цель д .кггигается тем, что Б предложенное устройство введены s уэпап сопряжения и ( S - 1) узлов сравнения. Первый и второй информационные входы первого узла сравнения соединены с первь ми входными шинами. Первый и второй выходы каждого -го узла сравнения, где rl:

1, 2, ..,., S , подключены к входам -гс узла сопряжения соответственно, а первый выход -го узла сопряжения - к входам первого и второго элементов И -и , другие входы которых подключены к первым выходам 1, 2, ... ( - 1)-го уэлов сопряжения и к (g + 1)ым входным шинам, кроме элементов И б -ой группы. Выходы первого и второго элементов -ой группы, где 1,2,..., S - 1, соединены с входами ( / 1)-го узла сравнения. Второй выход каждого J -го узла сопряжения подключен к одним из входов третьего н четвертого элементов И i -и группы. Другие третьего и четвертог-о элементов И 0 -и группы соеди}1С НЫ с третьим и четвертым выходами -го узла сравнения, а выходы третьегб и четвертого элементов И О -ой группы и третий выход

Г) -го узла сопряжения - с соответствующими входами преобразователя KOff-напряжение. Одни из входов первого и второго элементов И S -и группы соединены с входной шиной, с четверТым выходом -го узла сопряжения и с пятым выходом s -го узла сравнения, а их выходы - с входом преобразователя временной интервал-код н с входом блока выдачи соответственно. Одни из входов тргетьего и четвертого элементов И 5 -и группы подключены к первому выходу (S- 1)-го узла сопряжения. Узлы сравн&ния содержат элементы ИЛИ и триггер с двумя счетными входами, которые соединены с входными шинами узла, а первый и второй выходы подключены через элемент ИЛИ к первой выходной шине узла. Третий и четвертый выходы триггера соединены с третьей и четвертой выходными шинами уэ-i. ла и через элемент ИЛИ с второй выходной шиной, а пятый выход - с пятой выходной шиной узла Узлы сопряжения содержат триг гер с двумя счетными входами, элемент задержки и K.-S триггер. Вход установки в нулевое состояние триггера с двумя счетными входами соединен через элемент задержки с.его первьЯи счетным входом и первой входной шиной узла, второй счетный вход - со второй входной шиной узла, а первый и ; второй выходы - со входами R-s триггера и с третьей и четвертой выходными шинаМИ узла. Выходы R - s триггера подключены к первой и второй выходным шинам узлй сопряжения.

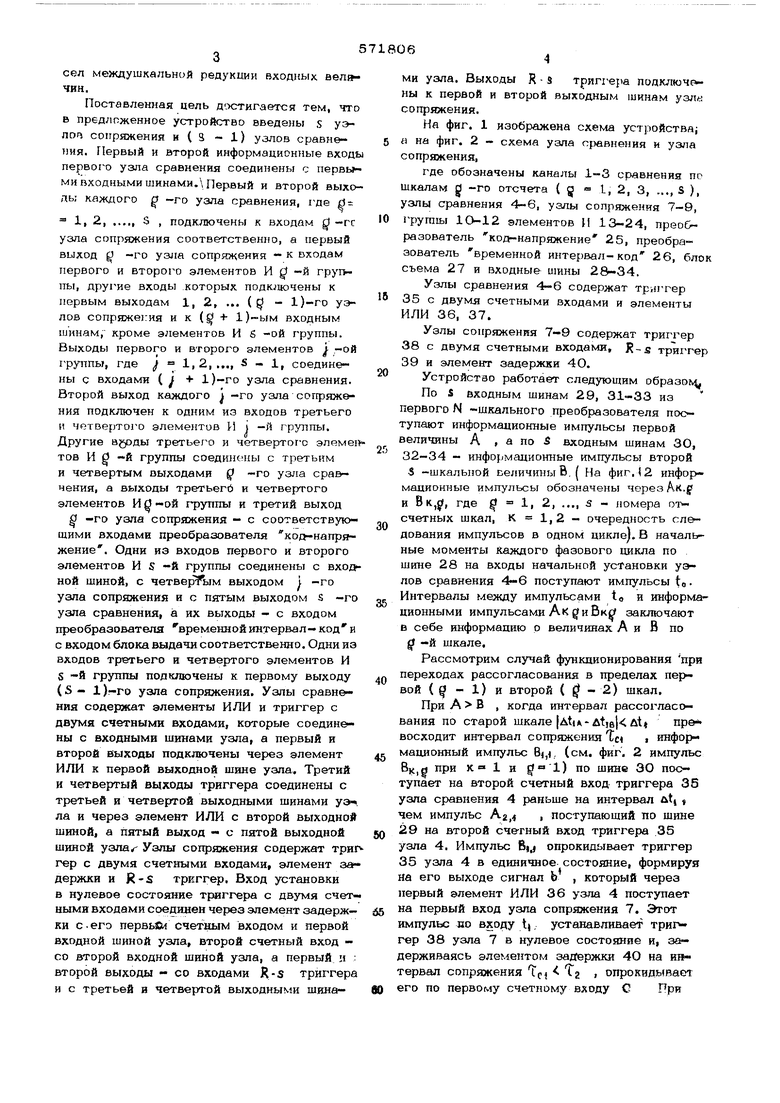

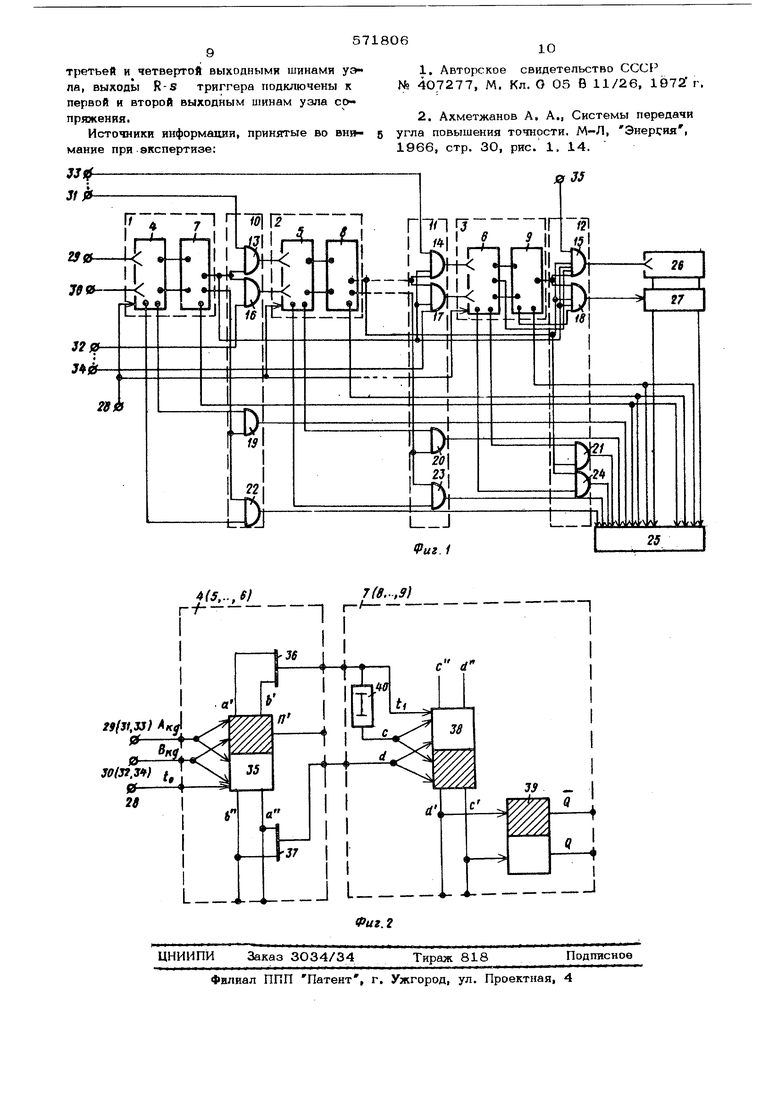

На фиг. 1 изображена схема устройства; 6 « на фиг. 2 - схема узла пршвнения и узла сопряжения,

где обозначены каналы 1-3 сравнения по шкалам g -го отсчета { g 1, 2, 3, ..., S ), узлы сравнения 4-6, узлы сопряжения 7-9, группы 1О-12 элементов И 13-24, преоСразователь код-напряжение 25, преобразователь временной интервал-код 26, блок съема 27 и входные шины 2&-34.

Узлы сравнения 4-6 содержат триггер 35 с двумя счетными входами и элементы ИЛИ 36, 37.

Узлы сопряжения 7-9 содержат триггер

38с двумя счетными входами, Tplirrep

39и элемент задержки 4О.

Устройство работает следующим образоц,

По S входным шинам 29, 31-33 из первого N -шкального преобразователя поступают информадионные импульсы первой величины А , а по 5 входным шинам ЗО, 32-34 - информадионные импульсы второй 5 -шкальной величины В, I На фиг. 12 информадионные импульсы обозначены через A.K.g и Вк,, где 1, 2, ..., s - номера oi счетных шкал, К 1, 2 - очередность следования импульсов в одном цикле). В начальные моменты Каждого фазового цикла по шине 28 на входы начальной установки у&лов сравнения 4-6 поступают импульсы to Интервалы между импульсами to и информационными импульсами Вк заключают в себе информацию о величинах А и В по -и шкале.

Рассмотрим случай функционирования при переходах рассогласования в пределах первой ( - 1) и второй ( - 2) шкал.

При А В , когда интервал рассогласования по старой шкале |AtiA-Atiel л1« пре восходит интервал сопряжения tci t инфор, мационный импульс BI,, (см. фиг, 2 импульс BK,O при к 1 и 1) по шине ЭО поступает на второй счетный вход триггера 35 узла сравнения 4 раньше на интервал utj , чем импульс Лг, , поступающий по шине 29 на второй счегный вход триггера 35 узла 4. Импульс B|j опрокидывает триггер 35 узла 4 в единичное состояние, формируя на его выходе сигнал b , который через первый элемент ИЛИ 36 узла 4 поступает на первый вход узла сопряжения 7. Этот импульс по Bxojfiy t), устанавливает трипгер 38 узла 7 в нулевое состояние и, задерживаясь элементом задержки 4О на интервал сопряжения Tpi Tg , опрокидывает его по первому счетному входу G При 8ТОМ на выходе С триггера 38 узла 7 формируется импульс, который, поступая на входы преоб1)азователя 25, устаршвливае на его выходе максимальное напряжение. Этот же импульс, поступая на вход R-s триггера 39 узла 7, устанавливает его в состояние, при котором выходные потенциалы Q и Q устанавливают элементы И 13-18 в состояние запрета, а элементы И 22, 19 - в состояние разрешения. Через интервал utj по входной шине 29 на счетный вход узла 4 поступает информационный импульс- Аг ( и опрокидывйет триггер 35 узла 4 в нулевое состояние. Пр этом на выходе а триггера 35 формируется импульс, который через второй элемент ИЛИ 37 узла 4 поступает на второй счетны вход триггера 38 узла 7 и через элемент И 19 на знаковый вход преобразователя 25 В преобразователе 25 устанавливается положительный знак выходного напряжения, а триггер 38 узла 7 устанавливается в нул&вое состояние, формируя на своем выходе d импульс. При этом информационные импульсы АКс| и BKJ всех мшадших шкал не проходят на входы узлов через элементы И 13, 14, 16 и 17, находящиеся в состоянии запрета. Через элемент 11 15 на вход преобразователя 26 гшполняющие импульсы, поступающие по входу 35 устройст- ва, также не проходят. Устройство работает аналогично в каж дом К -ом цикле, если рассогласование по первой шкале больше интервала сопряжения tct Аналогично работает устройство и при отрицательных рассогласованиях (АВ О) npHJAtf Tc4 с той лишь разницей, что информационный импульс Ац по шине 29 поступает раньше на первый счетный вход триггера 35 узла 4, чем информационный импуяБс БЗ, , поступающий на его второй счетный вход по шине 30. При первом опро .квдывании триггера 35 узла 4 импульс фор MHJpyeTCH не на выходе Ь , а на выходе а , а при втором опрокидывании - не на выходе а а на выходе Ь . Отрицательный знак выходного напряжения преобразователя 25 устанавливается импульсом Ь проход$шшм через элемент И 22. При уменьшении рассогласования наступает момент, когда по первой шкале интервал рассогласования Att становится меньше янтервала сопряжения Т с ч « При этом импульс с выхода а или Ъ (в зависимости ог знака рассогласования) триггера 35 уэла 4 поступает через элемент задержки 40 на первый счетный вход триггера 38 узла 7 позднее, чем импульс с выхода а или Ь тригг-ера 35 узла 4 поступит на счетны ВХОД трипера 38 узла 7, Первое опрокидывание триггера 38 узла 7 происходит от действия импульса по счетному входу cf , при котором формируется импульс на выходе d . Этот импульс опрокидывает R- трнг гер 39 узла 7. Потенциалы Q и Щ R-S триггера устанавливают элементы И 19 и 22 в состояние запрета, а элементы И 13 и 16 - в состояние разрешения. При этом осуществляется переход на сравнение по в рой шкале. По шинам 31 и 32 через элементы И 13 и 16 на счетные входы триггера 35 узла 5 поступают информационные .импульсы AR и Bj . Узел сравнения 5 и узел сопряжения 8 канала 2 по второй шкале функционируют аналогично узлам 4 и 7 а канале 1 по первой шкале. Максимальное напряжение в преобразователе 25 устанавливае ся импульсом с выхода С узла. 8, а его знак - импульсом с выхода а или с выхода Ь уэла 5, которые поступают на знаковый вход преобразователя 25 через элемент И 20 или через элекюиг И 23. При раг(:г.1гласованиях в пределах млааlufi шкалы, Когда интервал рассогласования ut Гюльше интервала линейного участка 1;j (Tj задается элементом задержки 40 узла элементы И 13, 14, 16 и 17 установлены в состояние разрешения, а элеме ты И 19, 20, 22 и 23 - в состотше запрета. Информационные импульсы младшей шкалы по шинам 33 и 34 поступают через эпеменгы И 14 и 17 на входы узла сравнения 6. Узлы 6 и 9 канала 3 функционвруют аналогично узлам 4 и 7 или 5 и 8 в старших, каналах. При уменьшении рассог ласования до значения lutjK 1лимпульс по входу d триггера 38 узла 9 поступает раньше импульса, поступающего по его входу С ,поэтому в каждом цикле С триггер 38 узла 9 при первом опрокидывании формирует импульс на выходе d , а при втором опрокидывании - на выходе.с . Импульсом с выхода d R-S триггер 39 узла 9 устанавливается в состояние, при котором его потенциал является разрешающим для элементов И 15 и 18. Разрешающими дня них являются и потенциалы Q узлов сопряжения 7, 8 всех старших шкал. Кроме т.ого, элемент И 15 управляется потенциалом Л с выхода узЛа 6, длительность уровня которого в каждом цикле равна рассопласованню Atsi. « задний фронт совпадает с импульсом на выходе d узла 9, поэтому в каждом цикле элемент И 15 находится в состоянии разрешения в течениеинтервала tg , который преобразуется в код путем заполнения преобсазователя 20 тактовыми импульсами Т i поступающими через шину 35, По заднему фронту потенциала П элемент И 15 закрывает вход преобразоваФеля 26, и импульсом с выхода d узла 9 через элемент И 18 и блок съема 27 производится перезапись кода преобразовав теля 26 в преобразователь 25, Если рассогласование увеличится до зна чения |ats ТА , то R-S триггер 39 уэла 9 под действием импульса на его выходе С опрокидывается, и его потенциалом Q элементы И 15 и 18 устанавливаются в соо то$шие запрета. Импульсом с выхода С узл 9 во все разряды преобразователя 25 за писываются единицы, т. е, максимальный сигнал. При дальнейшем увеличенииpaccoi -ласования аналогично срабатывают узлы сопряжения 8 и 7 старших шкал, и их потенциалами Q и S поочередно перевбдЗятся в состояние запрета элементы И 14, 17, 13 и 16, а в состоЕШие разрешения - элементы И 20, 23, 19 и 22. Устройство формирует разностный сигнал без предварительного преобразования ходных сигналов многошкальнык преобразователей в код. В известных устройствах шкалы S-шкальных преобразователей сопр гаются числами междушкальной редукции Раа« - т, е. кратными числу 2. Та ЧЧкое ограничение исключает возможность оптимальной компановки шкал и монотонного увеличения числа Ng,iквантов (уровней) сигнала S -шкальноод. преобразователя, поо ..Hpd.d.l 8g. Устройство без изменений может быть использовано для сравнения сигналов многошкальных преобразователей различных типов индукционных фазовращателей с электрической или механической редукцией между шка лами, преобразователей напряжения в сигналы преобразователей с применением опорного генератора пилообразного напряжения или компенсирующего генератора, преобразсн вателей код - временной интервал ; вателей кпп - ППРМРНТТПЙ гттог пяп Формула изобретения 1. Многоуровневое устройство для срав нения, содержащее преобразователь временной интервал - код , выходы которого через блок выдачи подключены к входам преобразователя код-напряжение, узел

сравнения группы элементов И, о т л и- 55соединен через элемент задержки с его

чающееся тем, что, с целью повы-первым счетным входом и с первой входной

шения точности работы и расширения дна-шиной узла второй счетный вход триггера

пазона чисел . междушКальной редукции вход-с двумя счетными входами соединен со втоных величин, в него введенУ з узлов входной шиной узла, а первый и второй

жения и ( S - 1) узлов сравнения- причем дОвыходы - со входами R-S триггера и с первый и второй информационные входы первого узла сравнения соединены с перовыми входными шинами, первый и второй выходы каждого д -го узла сравнения, где 1, 2, ..... S , подключены к входам g -го узла сопряжения соответственно, а первый выход -го узла сопряжения соединен с входами первого и второго элементов И -и группы, другие входы которых пойключены к первым выходам 1, 2,.., ( - 1)го узлов сопряжения и к ( + 1)-ым BXOffным ишнам, кроме элементов И S -и группы выходы первого и второго элементов i -& группы, где } 1, 2, -..S- i) соединены с входами ( ./ + 1)-го узла сравнения; второй выход каждого -То узла сопряжения подключен к одним из входов третьего ji четвертого элементов И -и группы, дру гие входы третьего и Четвертого элементов и -и группы соединены с третьим и.четвертым выходами gf-ro узла :сравнения, а выходы третьего и четвертого элементов И О -и группы и третий выход -го узла сопряжения подключены к сЪответствующим входам преобразователя код-напряжение, одни из входов первого я второго элементов И , группы соединены с входной шиной, с четвертым выходом J. -го узла сопр)ЯЖения и с пятым выходом -го узла сравнения, а их выходы - с входом преобразователя временной интервал - код и с входом блока выдачи соответственно; одни из входов третьего и четвертого элементов И 5 -и группы подключены к. первому выходу ( 5 - 1)™го узла сопряжения. 2, Устройство по п. 1, о т л и ч а ющ е е с я тем, что в нем узлы сравнения содержат элементы ИЛИ, триггер с двумя счетными входами, которые соединены с входными шинами узла, а первый и второй выходы подключены через элемент ИЛИ к первой выходной шине узла, третий и чет вертый выходы триггера соединены с третг ей и четвертой выходными шинами узла и . через элемент ИЛИ - с второй выходной шиной, а пяггый выход - с пятой выходной шиной узла. 3. Устройство по п. 1, отлича ющ е е с я тем, что в нем узлы сопряж&ния содержат триггер с двумя счетными входами, элемент задержки и R 5 триггер, причем вход установки в нулевое состояние триггера с двумя счетными входами третьей и четвертой выходными шинами па, выходы R-S триггера подключены к первой и второй выходным шинам узла сопр51жения. Источники информации, принятые во вни-5 мание при экспертизе: 1, Авторское свидетельство СССР № 4О7277, М. Кл, О 05 В 11/26, 1972г. 2. Ахметжанов А, А., Системы передачи угла повышения точности. М-Л, Энергия, 1966, стр. 30, рис. 1, 14.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая следящая система | 1977 |

|

SU682872A1 |

| Цифровая следящая система | 1973 |

|

SU525052A1 |

| Устройство для контроля статических параметров цифроаналоговых преобразователей | 1986 |

|

SU1352647A1 |

| Устройство для ввода аналоговой информации | 1988 |

|

SU1501026A1 |

| Многоканальный преобразовательКОд-ВРЕМЕННОй иНТЕРВАл | 1979 |

|

SU818000A1 |

| Стабилизатор переменного напряжения | 1988 |

|

SU1534434A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1991 |

|

SU1820386A1 |

| Преобразователь код-временной интервал | 1985 |

|

SU1305865A1 |

| Дифференцирующее устройство | 1974 |

|

SU516063A1 |

| Селектор импульсов по длительности | 1988 |

|

SU1647876A1 |

Авторы

Даты

1977-09-05—Публикация

1974-09-09—Подача