I

Изобретение относится к спепиализиро- ванным цифровым вычислительным устройс р вам для.определения статистических xapas Теристик случайных процессов и может ней ти применение при исследовании объектов автоматизации в различных отраслях про ЫШЛенностНя

Известен регресс.иограф работающий по аналоговой схемотехнике. Недостатком этого; регрессиографа является невысокая точность работы.

Известно цифровое вычислительное уст«« ройство 2, содержащее блок управления выходы которого ,подключены cooTBeTCTBea но к управляющим входам блока памяти, арифметического блока, блока регистрации и первого и второго аналого-цифровых пре обраэователей (АЦП), информационные вхоа ды которых являются входами устройства, а разрядные выходы через первый и второй коммутаторы соответственно подключены к соответствующим Ьходам блока памяти, вь ход( koToporoi соединен со входом арифметй ческого блока, подключенного выходом s

2

первому информационному блока ре-« гистрации

Однако определение регрессии |с помощью этого устройства требует значительных зй1« рат времени, несмотря на его цифровую структуру.

Цель изобретения повышения быстродействия I устройства,

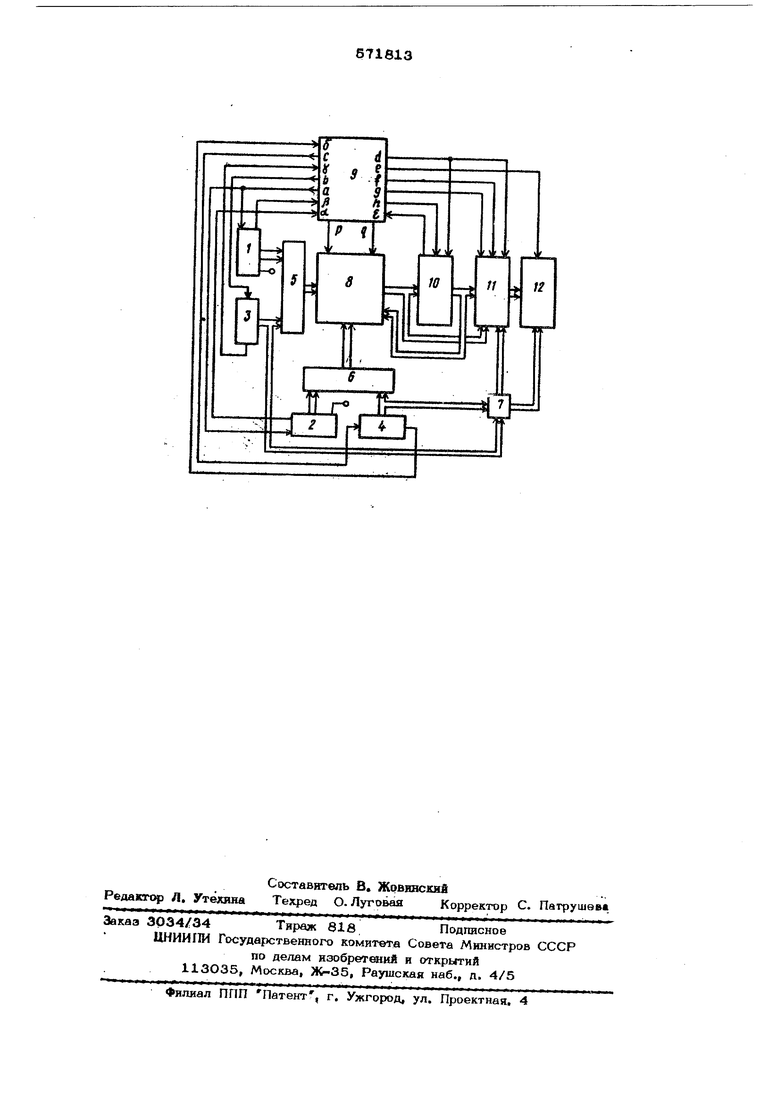

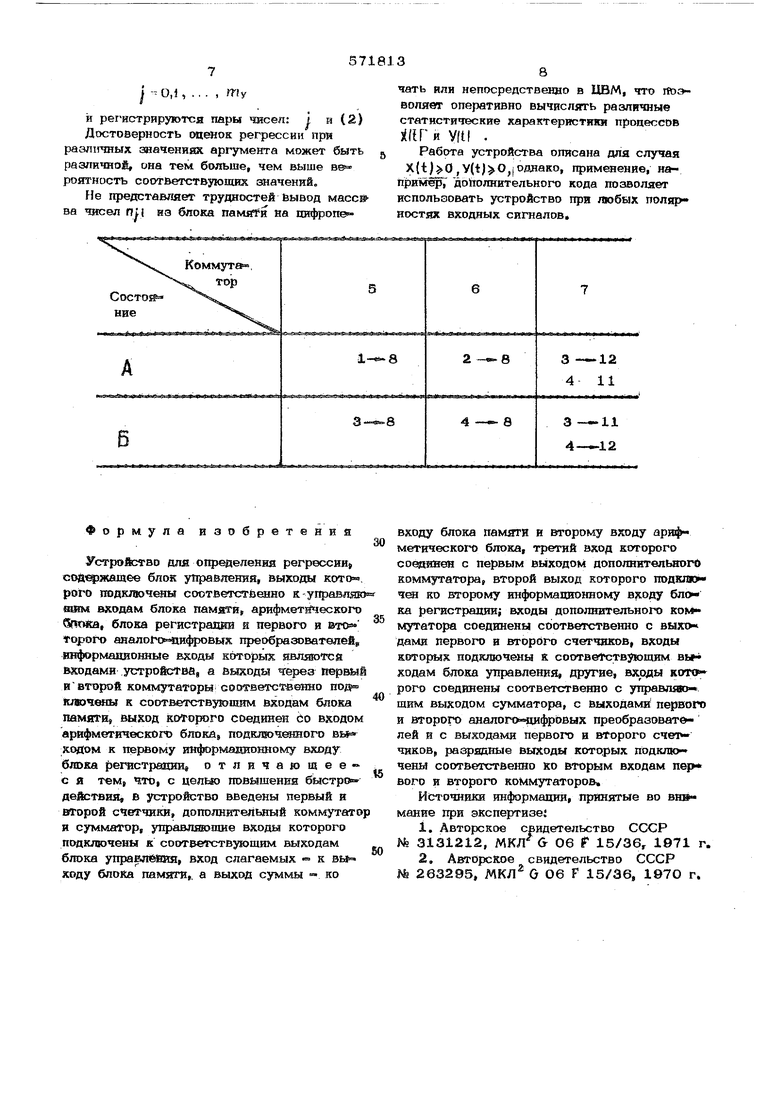

Эта цель достигается тем, что в предложенное устройство введены первый и вто рой счетчики, дополнительный teoMMyTETOp и сумматор, управл аощйв входы которого подключены к соответствующим выходам блока управления, вход слагаемых - к вь ходу блока памяти, .а выход суммы ко входу блока паматй и второму входу ар1ф метического блока. Третий вход арвфмвтв ческого блока соединен с первым выходом дополнительного коммутатора, второй выход которого подключен ко второму информадвов ному входу блока регястрадии. Входы дополнительного коммутатора соединены соотве ственно с выходами первого и второго счетчиков, входы которых пoдкJ5oчeны к cwn ветствующнм выходам блока упраалеввя Другие входы последнего соединены состветственно с управляющим выходом cyv матора, с выходами первого и второго АЦП и с выходами первого и второго счетчиков, разрядные выходы которых подключены соответственно ко вторым входам первого и второго коммутаторов. На чертеже дана блок-схема устройства. Оно содержит АЦП 1 и 2, счетчики импульсов 3 и 4, коммутаторы 5-7, блок памяти 8, блок управления 9, сумматор 10, арифметический блок 11 и блок регистрации 12.,. Исследуемые процессы | Yft) и I Xft) цоданы соответственно на информационные входы АЦП 1 и 2, разрядные выходы котсн рых соединены с первыми входами комму Тагоров 5 и 6. АЦП 1 и 2 выполнены ждущими -. после подачи импульса на нх запускающие входы, соединенные с выходом блока управления, они осуществляют один цикл преобразования, причем оба результата преобразования относятся к одному и тому же моменту временя (например, АЦП cBej ) , Ha выходах АЦП, соединенных со входами ( к f) блока упра&лениЯ| генерируются импульсы в моменты окончания преобразования. Счетчики 3 и 4, входы и выходы которых соединены соответственно с выходами Ь,С и входами у , § блока управления а разрядные выходы - со вторыми входами коммутаторов 5 я 6 соответственно и ВХЕ дами коммутатора 7, представляют собой накапливающие счетчики импульсов, с чиолом разрядов, равным числу разр5щов АЦП Iи 2 соответственно. Коммутаторы 5-7 имеют по два состояния, А и Б . Соответствующие соединения (выход- вход) указаны в таблице. Коммутатор 7 осуществляет соединения так, Vfv разряды одного и того же веса счетчиков 3 и 4 (начиная с младшего) подкш)чаются к одним и тем же щинам блоков IIи 12. Если при этом старщие разряды блоков 11 и 12 свободны (при различном числе разрядов счетчи1и в 3 и 4), на них подается нулевой потенциал. Блок памяти служит для накопления ста тнстических данных. Его адресными входами являются выходы коммутаторов Бив, Выход блока памяти соединен со входом ело гаемых сумматора и первым входом арифмети-

ческого блока, а вход-с выходом суммы сум-65 9 и 10. матора. При импульсах на выходах р и с блока управления, соединенных с управляющими входами блока памяти, последний передает в сумматор и арифметический блок со-. держнмое {гчейкв. определяемой кодовыми 60 комбинациями j , I на выходах коммут торов 5 и 6 соответственно, и записывает в ячейку с адресом ( j , I ) содержимое сумматора соответственно. Блок управления, выходы d и h которого соединены с управляющими входами сумматора, выходы d , f и а - с управляющими входами арифметического блока, выход - с управляющим входом блока, а вход - с управляющим выходом сумматора, работает в одном из трех режимов, задаваемых оператором: 1)ввод (накопление) статистических данных; 2)определение и вывод регрессии У на X i 3)определение и вывод регрессии X на V . Сумматор суммирует числа, поступающие с выхода блока памяти. Импульс, поступак « щий на вход сумматора с выхода Ь блока управления, увеличивает содержимое сумматора на единицу. Импульс, поступающий на сумматора с выхода d блока управITOUXTCT urTQlia ntmjtQQCip Qfr a ulrni- Uft BLI.... леиия, устанавливает его в нуль. На выходе сумматора, соединенном со входом блока управления, возникает импульс, когда число, введенное в сумматор с выхода блока памяти, оказывается .равным Ш - максимальному числу, которое может быть записано в ячейке блока памяти. Арифметический блок после каждого импульса с выхода р блока упраншения умножает числа, поступающие на второй и третий входы, соединенрые соответственно с выхо дами блока памяти и коммутатора 7, и суммирует результаты умножения. По команде, подаваемой импульсом с выхода f блока управления, арифметический блок делит сумму результатов умножения на число, поступающее с выхода сумматора. Импульс с выхода d блока управления устанавливает арифметический блок в исходное нулевое соо ояние. Блок регистрации, по команде, подаваемой импульсом с выхода Р блока управленвя печатает два числа, поступающих на его первый и второй| информационные входы. соединенные соответственно с выходами арифметического блока и коммутатора 7, Устройство работает следующим ображ)м В режиме ввода статистических данных в работе участву1от блоки 1, 2, б, 6, 8, В исходном состоянии коммутаторы 5 и 6 установлены в состояние А (см. таблицу), блок управления переведен в режим 1, блок памяти очищен, а сумматор установлен в нуль. После включения устройства блок управления импульсом с выхода а одновременно запускает АЦП 1 и 2. После того, как на входы « я р блока управления с выходов лип 1 и 2 поступают импульсы, свидетель вующие об окончвйии каждым из них преобрааования аналор-код: Yft -/) , Xlt)-H, он генерирует импульс на выходе Р . По этой команде содержимое пм ячейки с адре сом ( } , 1 ) передается в сумматор (сум мируется. с его содержимым). Затем ик пульс с выхода h блока управления увеличивает содержимое сумматора 10 на едв иицу, а импульс с выхода ) помещает результат (число п(/ ) в ячейку с адресом (i ,(/ . После этого описанные действия циклически повторяются: снова генерируется импульс на выходе а блока управления и т. д. В этом режиме устройство работает до техпор, пока оператор не прекратит ее, либо пока содержимое одной из ячеек блока памяти не достигнет максимально BoaMojKHO го числа m . При этом на выходе суммаго, ра, соединенном со входом блока управ ления 9, возникает импульс, останавливающий работу и срабатывает индикншш, указывающая причину останова. В результате в блоке памяти формирует ся. массив I чисел n:j , принимающих значений от нуля до т . Число т представляет собой число одновременных преобразований аналог-код процессов У(1 nXftJc результатами j и i соответственно из общего числа преобразований, равного И1хftiy где «х и - максимальные возможные чения t и j соответственно. В режим определения и вывода регресси У на X - регрессия У на X определяетс согласно формуле м ГУ/ X1 Г / /П L где t и i - результаты аналого-цифрового преобразования1 значений X и У соответственно;Ку - масштабный коэффициент; М - математическое ожидание. В этом режиме в работе участвуют все блоки устройства, кроме АЦП 1 и 2. В исходном состоянии счетчики 3 и 4 очищены, в блоке памяти сформирорэн маосив чисел пц , сумматор и арифметический блок установлены в нуль, коммутаторы 5-7 переведены в состояние Б (см. таблицу), а блок управления - в режим 2. После запуска устройства в этом режиме блок управления генерирует импульс на вь ходе Р , затем последовательно во времени на выходах g и b . После этого указанное сочетание этих трех импульсов цив лически повторяется, пока не; возникнет импульс переполнения на выходе счетчика 3, возвращающегося при этом в исходное соотояние. К этому моменту в сумматоре сформировано число , а в арифметическ ом блоке - число ffla. 1 , , С приходом на вход у импульса пере, полнения с выхода счетчика 3 блок упра&ления генерирует последовательно во времени по одному импульсу на выходах / , , d и С , В результате арифметичеЬ-. кий блок вычисляет величину м J/0 (1) блок регистрадши регистрирует число О и число (151 сумматор и арифметический блок сбрасываются в нуль, а содержимое счетчика 4 увеличивается на единицу. Далее описанная последовательность действий циклически повторяется, hpи этом определяются и регистрируются пары чисел: 1 «Mlj/t при ( 1,2,...,П1 . Импульс переполнения счетчика 4, поступая на вход b блока управления, останавливает работу устройства. При этом включается соответст вуютая индикация причины останова В режиме определения и вывода регрессии X на V . Работа устройства отличается от описанной выше только тем, что комму татор 7 устанавливают в состояние А , а блок управления меняет ролями выходы b и С : те импульсы, которые в предыду. щем режиме генерировались на вьлходе tr , появляются теперь на выходе С и наоборот. Таким образом, счетчики 3 и 4 как бы меняются местами ,; в результате aliaлbnг но предыдущему определяются величины Ы i

-0,J

my

/

и регистрируются пары чнсел: i и (2) Достоверность (щенок регрессии при раал1пшых значениях аргумента может быть различной, она тем больше, чем выше в&poiTTHocTb соответствующих значений.

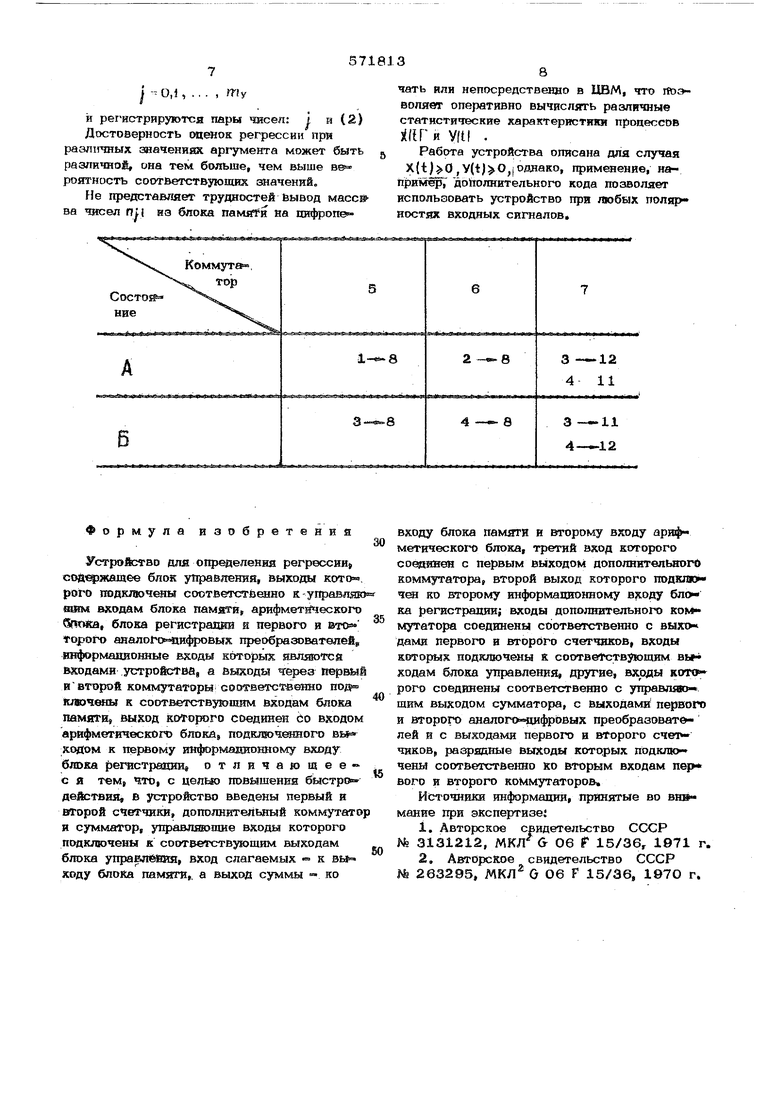

Не представляет трудностей ьывод масс ва чисел nil из блока памяти на цифропеКоммута,

TOJP

Состой вне

чать или непосредственно в ЦВМ, что гйээвопявг оперативно вычислять различные статистические характеристики процессов

тг и vfti .

Работа устройства описана для случая X(,V(t)O,|однако, применение, напримёр дополнительного кода позволяет использовать устройство при /аобых полярностях входных сигналов.

6

1-«-8

3

2-«-8 4 11

3 -11

4 - 8 4-12

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания графической информации | 1987 |

|

SU1564661A1 |

| Устройство для определения корреляционной функции | 1987 |

|

SU1501086A1 |

| Многоканальный многомерный цифровой коррелометр | 1984 |

|

SU1187177A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для вычисления полинома | 1982 |

|

SU1098003A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

Формула изобретения Устройство для опрейеленна регрессии содержащее блок управления, выходы кото рого тюккпоч&аз соответстбенно к-управляг WBtA входам блока памяти, арифметического , блоке регистрации и первого и тррого аналоГтмди чювых преобразователей 1шформа1шонные входы которых гтляютса входами устрой ства, а выходы чорез першя ивторой коммутаторы соответствеяно под ключены к соответствующим входам блока памяти выход которого соединен bo входом арифметического бпокй., подключшшого вь ходом к первому информадионному входу блока регистрадиив отличающеес я тем, «сто, с цельет повышения быстро действия, в устройство введены первый и второй счетчики, дополнительный коммутато и сумматор, управляющие входы которого подключены к соответствующим выходам блока управления, вход слагаемых к вы ходу блока пам5гги,, а выход суммы ко входу блока памяти и второму входу арифметического блока, третий вход которого сочинен с первым выходом дополнительного коммутатора, второй выход которого подшао Ч&1 ко второму информационному входу блока регистрации; входы дополнительного коммутатора соединены соответственно с выхх дами первого и второго счетчиков, входы которых подключены к соотве11ствующим выходам блока управления, другие, входы кото рого соединены соответственно с управляю- шим выходом сумматора, с выходами первого и второго аналого-цифровых преобразователей и с выходами первого и второго счет чнков, разрядные выходы которых подкшочены соответственно ко вторым входам пер вого и второго коммутаторов. Источники информации, принятые во внв мание при экспертизе; 1.Авторское свидетельство СССР № 3131212, Сг 06 Г 15/36, 1971 г. 2,Авторское свидетельство СССР № 263295, МКЛ О Об F 15/36, 1970 г.

Авторы

Даты

1977-09-05—Публикация

1975-11-10—Подача