pa соответственно к разрядной шине X н чнслевой шине У.

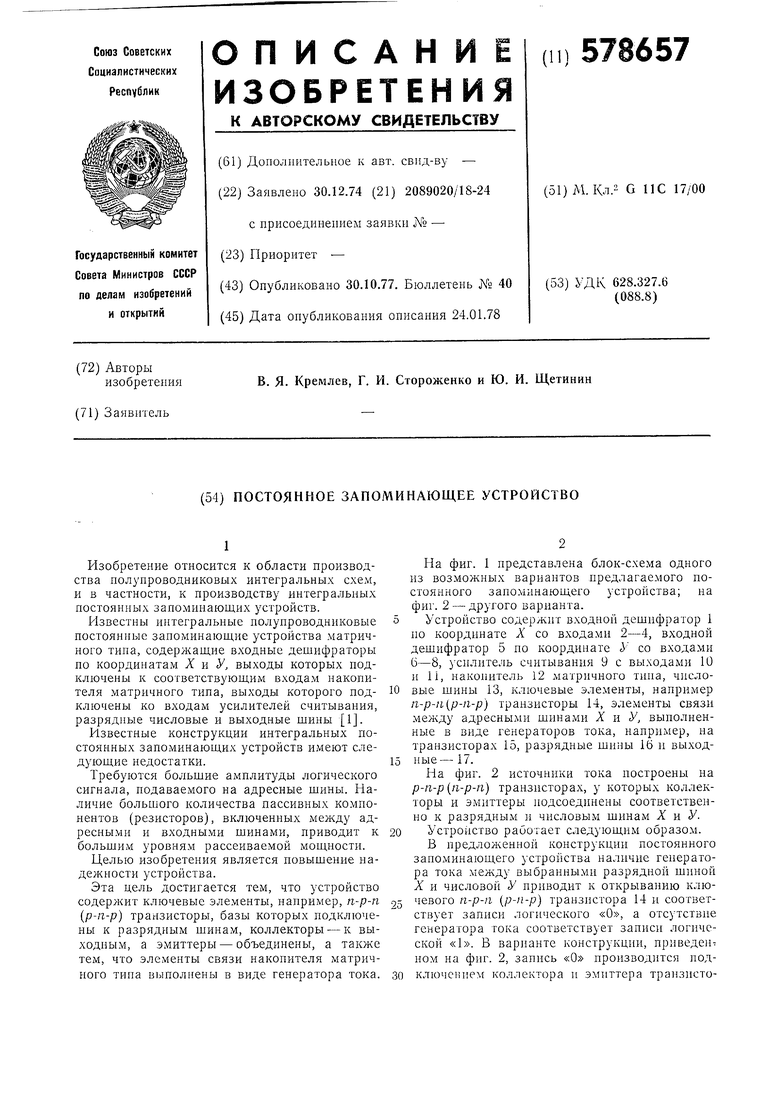

При подаче на входы 2-4 и б-8 адресного кода выборки на одной пя числовых шин 13 возникает высокий уровень наиряжепия, а на одной или более разрядны ч шин 16 создается режим высокого выходного соиротивления. При наличии генератора тока как элемента связи накопителя выбранная числовая шина

13оказывается соединенно с разрядными шинами 16 и базами ключевых транзисторов 14. Ключевые транзисторы открываются и на выходах накопителя появляется низкий уровень напряжения. Если связь между выбранной числовой шиной 13 и разрядными шинами 16 отсутствует, т. е. генератор тока оборван, то соответствуюшие ключевые транзисторы 14 оказываются закрытыми, что соответствует высокому уровню напряжения на выходах накопителя. Таким образом, наличие или отсутствие генератора тока в качестве элемента связи между числовыми и разрядными шинами накопителя позволяет записывать логические уровни «О и «1.

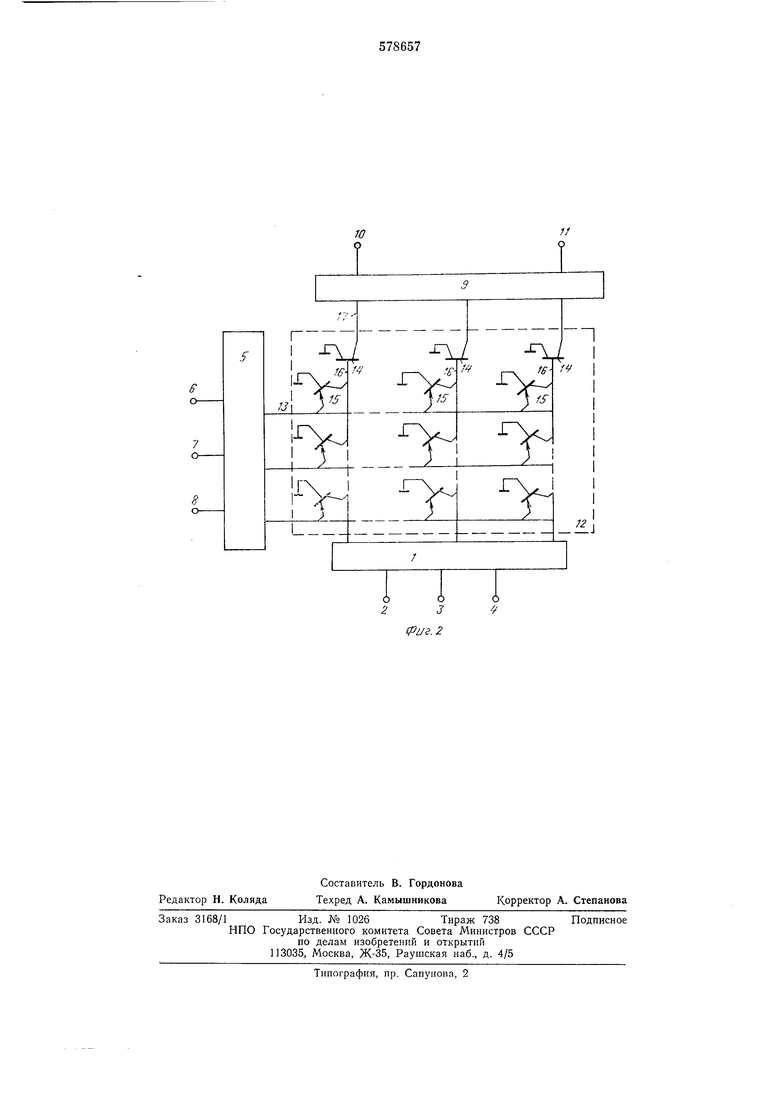

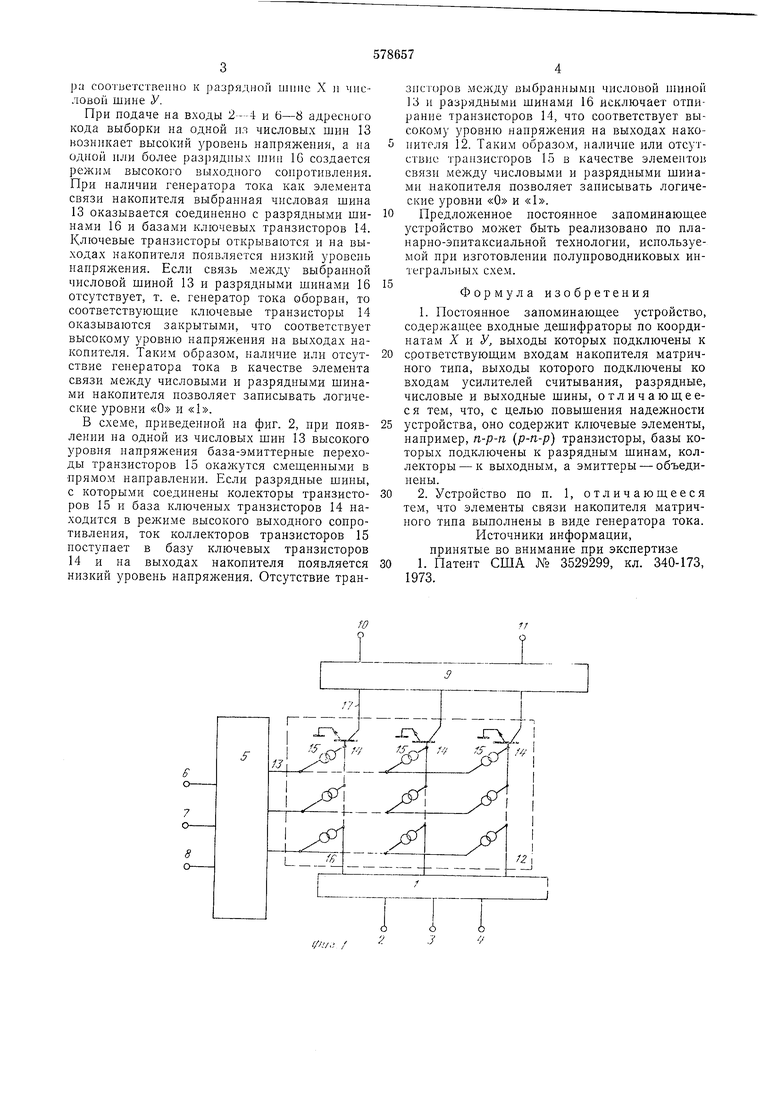

В схеме, приведенной на фиг. 2, при появлении на одной из числовых шии 13 высокого уровня напряжения база-эмиттерные переходы транзисторов 15 окажутся смешенными в прямом направлении. Если разрядные шины, с которыми соединены колекторы транзисторов 15 и база ключеных транзисторов 14 находится в режиме высокого выходного сопротивления, ток коллекторов транзисторов 15 поступает в базу ключевых транзисторов

14и на выходах накопителя появляется низкий уровень напряжения. Отсутствие транзнсгоров между выбранными числовой шиной 13 и разрядными шинами 16 исключает отпирание транзисторов 14, что соответствует высокому уровню напряжения на выходах накопителя 12. Таким образом, наличие или отсутствие транзисторов 15 в качестве элементов связи между числовыми и разрядными шинами накопителя позволяет записывать логические уровни «О и «1.

Предлол енное постоянное запоминаюш,ее устройство может быть реализовано по планарно-эпитаксиальной технологии, используемой при изготовлении полупроводниковых интегральных схем.

Формула изобретения

1.Постоянное запоминаюш,ее устройство, содержащее входные дешифраторы по координатам X и У, выходы которых подключены к срответствуюшим входам накопителя матричного типа, выходы которого подключены ко входам усилителей считывания, разрядные, числовые и выходные шины, отличающееся тем, что, с целью повышения надежности устройства, оно содержит ключевые элементы, например, п-р-п (р-п-р) транзисторы, базы которых подключены к разрядным шинам, коллекторы - к выходным, а эмиттеры - объединены.

2.Устройство по п. 1, отличающееся те.м, что элементы связи накопителя матричного типа выполнены в виде генератора тока.

Источники информации, принятые во внимание при экспертизе 1. Патент США № 3529299, кл. 340-173, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1988 |

|

SU1573472A1 |

| Матричный накопитель | 1986 |

|

SU1343443A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ | 1991 |

|

RU2020614C1 |

| Запоминающее устройство | 1977 |

|

SU769627A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1305775A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2018979C1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1111204A1 |

| Матричный накопитель | 1979 |

|

SU799007A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

№

/

ЛЛ

;/

41

/4

-У

/JM-

/

y,

Авторы

Даты

1977-10-30—Публикация

1974-12-30—Подача