I

Изобретение относится к области вычислительной техники, в частности К устройствам для умножения, работающим в системе счисления остаточных классов. .

Известны устройства умножения 1 работающие в позиционной системе счисления и содержащие регистры множимого, множителя и произведения, сумматор и блок элементов И.

Недостатком таких устройств является невозможность работы в системе счисления остаточных классов, что влечет за собой низкое быстродействие

Наиболее близким техническим решекием к изобретению является устройство, содержащее регистр множимого, регистр множителя, блок модульного умножения и сумматор 2 .

Надостатком устройства является низкое быстродействие.

Целью изобретения является повшиение быстродействия.

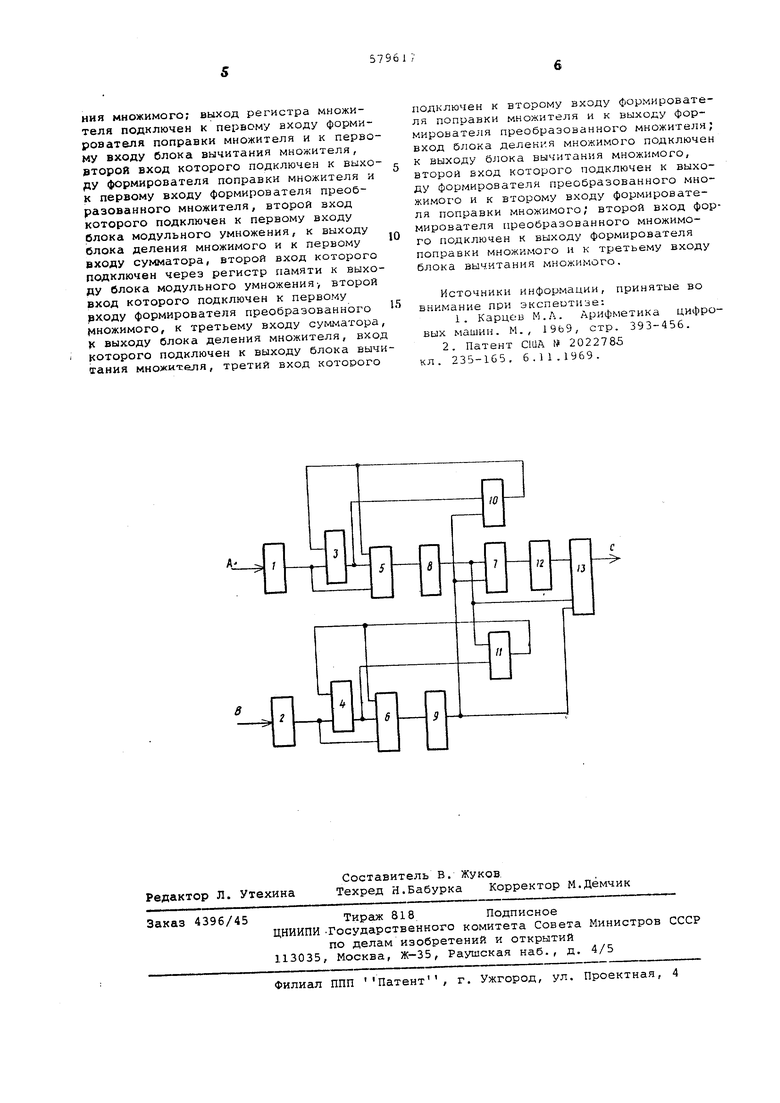

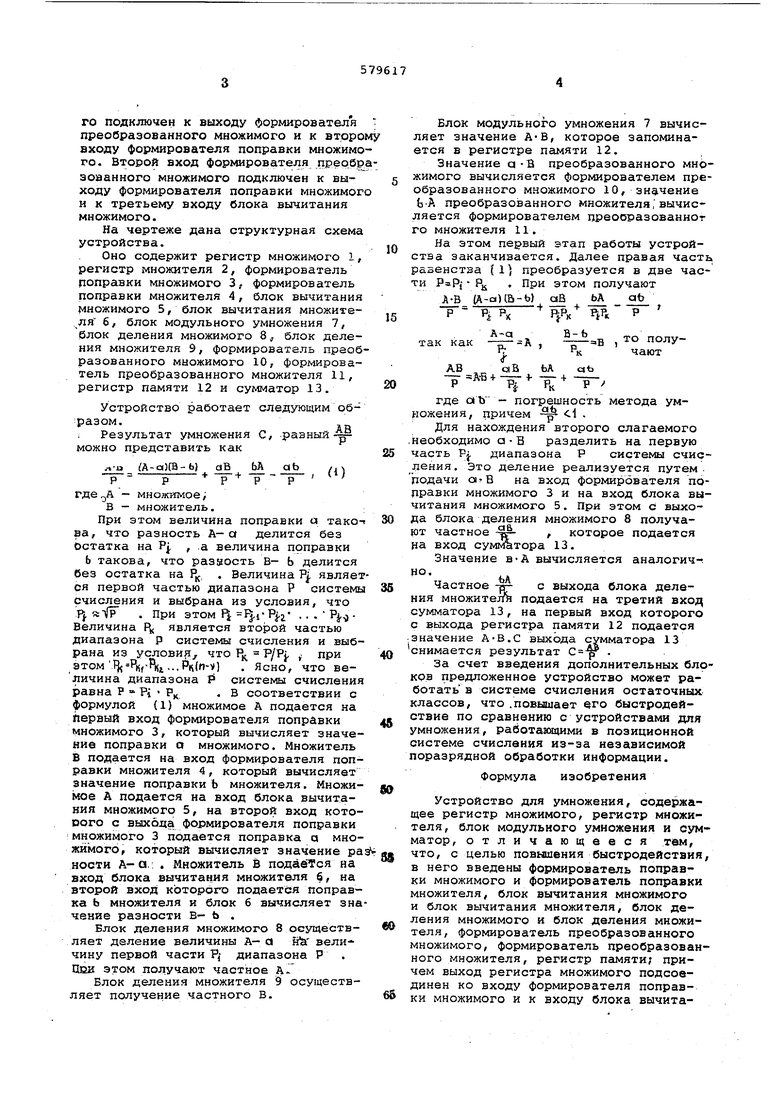

Эта цель достигается тем, что в предложенное устройство введены форми рователи поправки множимого и множителя, блоки вычитания множимого и множителя, блоки деления множимого и множителя, формирователь преобразованного множимого и формирователь преобра.зованного множителя, регистр памяти. Выход регистра множимого подключен к первому входу блока формирования поправки множимого и к первому входу блд ка вычитания множимого. Выход регистра множителя подключен к первому входу формирователя поправки множителя и к первому входу блока вычитания множителя , рторой вход которого подключен к выходу формирователя поправки множителя и к первому входу формирователя преобразованного множителя, вто рой вход которого подключен к первому входу блока модульного умножения, к выходу блока деления множимого и к первому входу сумматора, второй вход которого подключен через тэегисиз ддмяхи к выходу блока модульного умножения, второй вход которого подключен к первому входу формирователя преобразованного множимого, к третьему входу сумматора и к выходу блока деления множителя. Вход последнего подключен к выходу блока вычитания множителя, третий вход которого подключен к второму входу формирователя поправки множителя и к выходу формирователя преобразованного множителя. Вход блока деления множимого подключен к выходу блока вычитания множимого,второй вход котороГО подключен к выходу формирователя преобразованного множимого и к второ входу формирователя поправки множимо го. Второй вход формирователя преоб зованного множимого подключен к выходу формирователя поправки множимог н к третьему входу блока вычитания множимого. На чертеже дана структурная схема устройства. Оно содержит регистр множимого 1, регистр множителя 2, формирователь поправки множимого 3, формирователь поправки множителя 4, блок вычитания множимого 5, блок вычитания множителя 6, блок модульного умножения 7, блок деления множимого 8, блок деления множителя 9, формирователь преоб разованного множимого 10, формирователь преобразованного множителя И, регистр памяти 12 и сумматор 13. Устройство работаетследующим образом., Результат умноженияС, равный - можно представить как л-о Л-аКа-Ь) аВ ЬА аЬ р р +р+р-р где ,jA - множимое j в - множитель. При этом величина поправки а такова, что разность А- а делится без Остатка на Р , а величина поправки Ь такова, что развость В- Ь делится без остатка на Р, . Величина Р являет ся первой частью диапазона Р системы счисления и выбрана из условия, что 1 ft . При этом FJ 15-1-Р}- .. . Pj, Величина Р является второй частью диапазона Р системы счисления и выбрана из ycлoвия ЧТО Р P/Pj, при этом1 Рк|-Ркг ..,Рк{п-у1 . Ясно, что величина диапазона Р системы счисления равна Р Pi РК «В соответствии с формулой (1) множимое А подается на Первый вход формирователя поправки множимого 3, который вычисляет значение поправки а множимого. Множитель В подается на вход формирователя поправки множителя 4, который вычисляет значение поправки Ь множителя. Множимое А подается на вход блока вычитания множимого 5, на второй вход котоDoro с выхода формирователя поправки множимого 3 подается поправка а множимого, который вычисляет значение pa нести А- а . Множитель В подается на вход блока вычитания множителя б, на второй вход которого подается поправка Ь множителя и блок б вычисляет зна чение разности в- Ь . Блок деления множимого 8 осуществляет деление величины А- d Ife. величину первой части Р,- диапазона Р . Ней этом получают частное Д Блок деления множителя 5 осуществляет получение частного В. Блок модульного умножения 7 вычисляет значение А-В, которое запоминается в регистре памяти 12. Значение а-В преобразованного множимого вычисляется формирователем преобразованного множимого 10, значение Ь-А преобразованного множителя,вычисляется формирователем преооразованиот го множителя 11. На этом первый этап работы устройства заканчивается. Далее правая часть равенства {1) преобразуется в две части ,- - Р, При этом получают ЬА аЬ А-В (A-a)a-b) оВ -р- Pi РК ПЧс рЁ1± В , то полуА-атак как „ А , Р чают (Г А« ЬА qfa А-Б + -:;т- - Р Р РК f п где 01U - погрешность метода умножения, причем - 1 . Для нахождения второго слагаемого необходимо а-Б разделить на первую часть Р}. диапазона Р системы счисления. Это деление реализуется путем. подачи От В на вход формирователя поправки множимого 3 и на вход блока вычитания множимого 5. При этом с выхода блока деления множимого 8 получают частное - , которое подается на вход сумм&тора 13. Значение в-А вычисляется аналогич-г но. Частное - с выхода блока деления множитеш подается на третий вхо сумматора 13, на первый вход которого с выхода регистра памяти 12 подается значение А-В.С выхода сумматора 13 снимается результат . За счет введения дополнительных блоков предложенное устройство может работать в системе счисления остаточных классов, что .повышает его быстродействие по сравнению с устройствами для умножения, работаяадими в позиционной системе счисления из-за независимой поразрядной обработки информации. Формула изобретения Устройство для умножения, содержащее регистр множимого, регистр множителя, блок модульного умножения и сумматор, отличающееся тем, что, с целью повышения быстродействия, в него введены формирователь поправки множимого и формирователь поправки множителя, блок вычитания множимого и блок вычитания множителя, блок деления множимого и блок деления множителя, формирователь преобразованного множимого, формирователь преобразованного множителя, регистр памяти; причем выход регистра множимого подсоединен ко входу формирователя поправки множимого и к входу блока вычитания множимого; выход регистра множителя подключен к первому входу формирователя поправки множителя и к первому входу блока вычитания множителя, этороЯ вход которого подключен к выхоРУ формирователя поправки множителя и к первому входу формирователя преобразованного множителя, второй вход которого подключен к первому входу блока модульного умножения, к выходу блока деления множимого и к первому входу сумматора, второй вход которого подключен через регистр памяти к выходу блока модульного умножения-, второй вход которого подключен к первому рходу формирователя преобразованного множимого, к третьему входу сумматора {С выходу блока деления множителя, вход которого подключен к выходу блока вычи тания множителя, третий вход которого подключен к второму входу формирователя поправки множителя и к выходу формирователя преобразованного множителя; вход блока деления множимого подключен к выходу блока вычитания множимого, второй вход которого подключен к выходу формирователя преобразованного множимого и к второму входу формирователя поправки множимого; второй вход формирователя преобразованного множимого подключен к выходу формирователя поправки множимого и к третьему входу блока вычитания множимого. Источники информации, принятые во внимание при экспеотизе: 1. Карцев М.Л. Арифметика цифровых машин. М., 19Ь9, стр. 393-456. 2. Патент США № 2022785 кл. 235-1G5, 6.11.1969.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения по модулю | 1980 |

|

SU947860A1 |

| Устройство для умножения чисел в системе остаточных классов | 1983 |

|

SU1149254A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Устройство для умножения | 1981 |

|

SU997031A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для умножения чисел в непозиционной системе счисления | 1981 |

|

SU1015382A1 |

| Арифметическое устройство для процессоров быстрого преобразования Фурье | 1983 |

|

SU1116434A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для умножения | 1988 |

|

SU1569824A1 |

А.1

13

Авторы

Даты

1977-11-05—Публикация

1975-03-25—Подача