ел

о

СЈ 00

ю

Изобретение относится к вычислиельной технике и может быть использовано при разработке быстродействуюих устройств для умножения чисел в тюбой позиционной системе счисления н дополнительном последовательном кое. Особенно эффективно его применение при разработке высокопроизводительных ЭВМ, использующих большие интегральные схемы и арифметику многократной точности.

Цель изобретения - увеличение быстодействия.

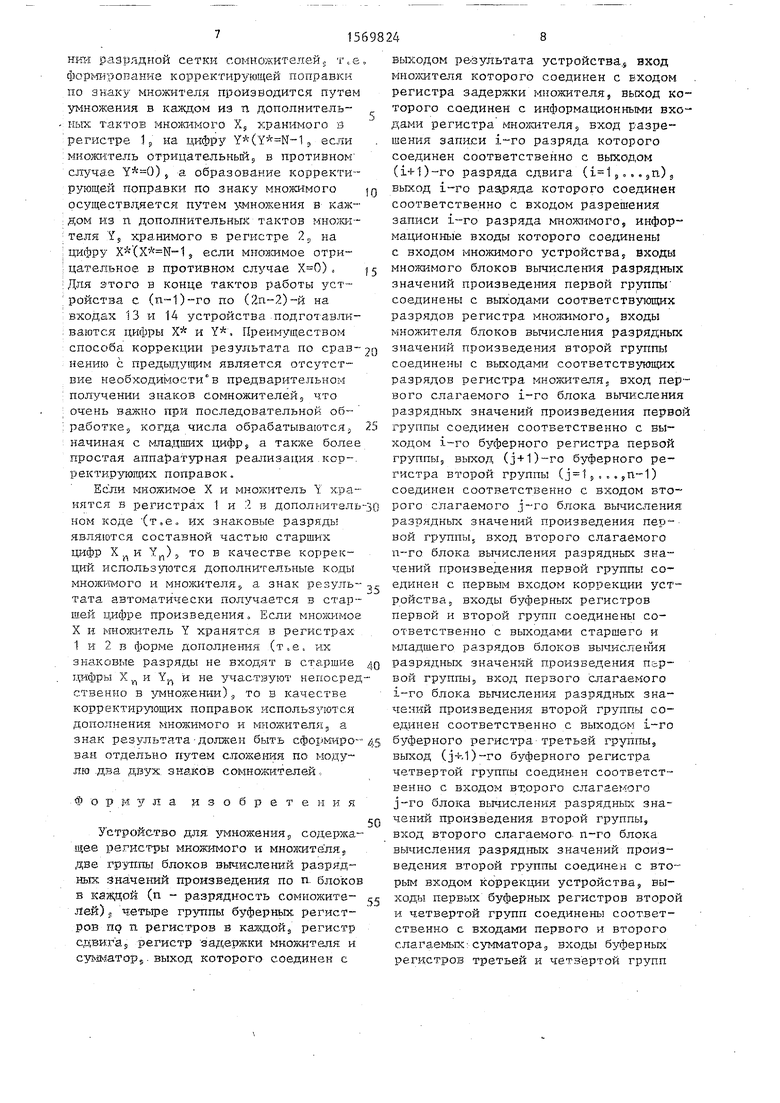

На чертеже приведена структурная схема устройства для умножения ,

Устройство для умножения содержит регистр 1 множимого, регистр 2 множителя, п блоков 3 вычисления разрядных значений произведения первой группы, п блоков 4 вычисления разрядных значений произведения второй группы, буферные регистры Ъ - 8 первой, второй, третьей и четвертой групп соответственно, регистр 9 сдвига,

регистр 10 задержки множителя, сумматор 11, регистр 12 задержки множимого, вход 13 множителя устройства,, вход 14 множимого устройства, первый 15 и второй 16 входы коррекции устройства,, выход результата 17 устройства .

Рассмотрим функциональное назначение и реализацию основных блоков уст ройства,

Регистры 1 и 2 предназначены для хранения значений разрядов множимого и множителя соответственно, поступаю щих в каждом такте работы устройства поразрядно,, начиная с младших разрядов, через входы 14 и 13 множимого и множителя устройства соответственно. Цепи синхронизации и установки в исходное состояние регистров 1 и 2, а также буферных регистров 5 - регистра 9 сдвига, сумматора 11 и регистров задержки 10 и 12 множителя и множимого соответственно не показаны. Каждый из блоков 3 и 4 предназначен для перемножения соответствующих значений разрядов множимого и множителя с одновременным подсуммированием к младшей части получившегося двухразрядного произведения двух одноразрядных слагаемых с выходов соответствующих буферных регистров. Буферные регистры. 5 и 7 первой и третьей групп соответственно предназначены для временного хранения значений старших раз1

2

2

0

5

0

5

0

35

40

5

50

55

рядов результатов, образованных на выходах соответственно блоков 3 и 4 вычисления разрядных значений произведения , Буферные регистры 6 и 8 второй и четвертой групп соответственно предназначены для временного хранения значений младших разрядов результатов, образованных на выходах соответственно блоков 3 и 4 .

Регистр 9 сдвига - (п+1)-разрядный и предназначен для управления записью разрядов множимого и множетеля в регистры соответственно 1 и 2. В начале работы устройства регистр 9 сдвига устанавливается в исходное состояние, при котором в самый первый его разряд заносится единица, которая в первом такте перезаписывается во второй разряд, во втором такте - из второго разряда в третий и т.д. Регистр 10 задержки множителя предназначен для временного хранения одного разряда множителя. Сумматор 11 последовательного типа осуществляет сложение в системе счисления с основанием значений двух равновесовых разрядов промежуточного результата, поступающих на его входы с выходов первых буферных регистров 6 и 8 второй и четвертой групп. Он состоит из комбинационного сумматора и элемента запоминания переноса, в который в каждом такте записывается значение переноса для гюдсуммирования в следующем такте. Регистр 12 задержки множимого предназначен для временного хранения одного разряда множимого.

Устройство работает следующим образом,

В исходном состоянии все регистры устройства обнулены, за исключением регистра 9 сдвига, в первом разряде которого записана единица. Множимое

, и множитель , . . . , представленные в N-й () системе счисления дополнительным кодом или дополнением (под дополнением понимается дополнительный код числа без знака), поступают на входы 13 и 14 устройства последовательно, начиная с их мпадших цифр X, и Y. Запись информации во все регистры устройства и сдвиг в регистре 9 осуществляются под действием одной и той же серии синхроимпульсов, т.е. один и тот же импульс, присутствующий в некоторый момент на синхровходе устройства, производит запись соответстх-х„,... ,

Y Y Y 1 3 2. 1

вующей информации в регистры 1 и 2 множимого и множителя, в буферные регистры 5 - 8, в регистры 10 и 12 задержки, в элемент запоминания переноса сумматора 11, а также осуществляется сдвиг информации в регистре 9. В начале выполняется подготовительный такт, в конце которого по первому синхроимпульсу происходит запись младшей цифры Y множителя в регистр 10 и младшей цифры X, множимого в регистр 12 и в первый разряд регистра 1. Одновременно в регистре 9 сдвига производится перезапись единицы из первого его разряда во второй, а на входах 13 и 14 подготавливаются следующие цифры V,, и Х„ сомножителей.

i и хе

После подготовительного такта начинается собственно умножение чисел.

В первом такте работы устройства в первом блоке 3 формируется разрядное произведение (. В конце такта по второму синхроимпульсу осуществляется запись значения данного произведения в первые буферные регистры 5 и 6, в регистр 10 заносится вторая цифра Уг множителя, а во второй разряд регистра 1 и в регистр 12 - вторая цифра Хг множимого, первая цифра Y множителя перезаписывается из регистра 10 в первый разряд регистра 2. На входах 13 и 14 устройства подготавливаются следующие цифры Х3 и Y3 сомножителей. Кроме этого, осу- ществляется перезапись единицы из второго разряда регистра 9 в третий разряд.

Во втором такте работы устройства в первом и втором блоках 3 формируются разрядные произведения соответственно и Х2У, а в первом блоке 4 - разрядное произведение . В конце такта по третьему синхроимпульсу после начала работы устройства осуществляется запись результатов, сформированных на выходах блоков 3 и 4, в соответствующие буферные регистры 5-8, третьей цифры Y} множителя - в регистр 10, третьей цифры Xj множимого - в третий разряд регистра множимого и в регистр 12, второй цифры Y2 множителя - из регистра 10 во второй разряд регистра 2. Кроме того, одновременно производится перезапись единицы в регистре 9 сдвига из третьего разряда в четвертый, а на входах 13 и 14 устройства подгоo

5

0

5

,

тавливаются следующие цифры Х4 и Y4 сомножителей.

Аналогичным образом устройство работает и в других тактах..

В п-м такте его работы в блоках 3 и 4 формируются разрядные произведения соответственно ХД, X4Yn

х nY п

XnV

и Xn Y,,

X и Y,

Х„ Y

ХЛ

3

В конце такта по (п+1)-му синхроимпульсу после начала работы устройства результаты, полученные на выходах блоков 3 и 4, записываются в буферные регистры 5-8, цифра YM из

0

регистра 10 в n-й разряд регистра 2 множимого. Кроме того, одновременно производится выдвижение единицы,из последнего (п+1)-го разряда регистра 9 сдвига, а это означает, что информация, сформированная в регистрах 1 и 2 к окончанию n-го такта, в дальнейшем не может быть изменена (в регистре 1 хранится множимое ,..., ,, а в регистре 2 - множитель

Y YnY3Y Y,).

Далее возможны два варианта получения окончательного произведения. Если выходы буферных регистров 5-8 подсоединены к 4-входовому сумматору (эти выходы обозначены прерывистой линией), то после выполнения п первых тактов необходим еще один такт, в котором четырехрядный код сворачивается к однорядному. При отсутствии 4-входо- вого сумматора окончательный результат образуется после п дополнительных тактов, в течение которых из устройства через его выход 17 выводится с соответствующими преобразованиями информация, хранимая в буферных регистрах 5 - 8.

В зависимости от указанных вариантов получения окончательного произведения возможны два разных способа его коррекции согласно алгоритму умно- жения чисел в дополнительном коде.

Если умножение выполняется с помощью 4-входового сумматора за (п-Н) тактов, то тогда возможен только спо0 соб коррекции результата, при котором корректирующие поправки по знакам сомножителей вводятся через входы 15 и 16 устройства.

Если умножение выполняется без ис5 пользования 4-входового сумматора за 2п тактов, то возможны два способа введения коррекции. При первом коррекция вводится через входы 15 и 16 устройства, а второй основан на расшире0

5

HIM р пг 1днои сетки омножитч л-ч- , i ф pMivo iHiie корректирующей п праы по HJ.I ;r множителя производится путем умножения в каждом из п дополнигель- II ч тидгоь 4НОЖЧМО1О X, хранч i эм и регистре 1, на цифру Y(. егпи множитепь отрицательный, в противном стлчае Y 0), а образование ч рректи рующеи поправки по знаку MHOJKHMOI о осуществляется путем умножения в каж ном из п дополнительных; тактов мнокь тепя Y, хранимого в регистре на циЛр X(, еспи множимое отги- цягетьное в противном случае /-О) Т ш лого в конце тактов работи v i ройстзл с in-1)-ro по ( 2п-0)-и на входах 13 и 14 устройства под i отминают с цифры X и Y, Прей iviue гном способа коррекции результат т. по с риз нснп о г прецн г является ir Ttr- вче нз %бх.от;нг о ги в предвариn 1ыю попечении знчко сомножителей г ) очень ва.чо прч последовательной о работчр, когда чиста обрабатнв inic iy начиная с младших цифр, а также боле простая аппаратурная реализация i гр- Р в к тир укицих поправок.

Если множимое X и множите ib t нягся в регистрах 1 и в rtoiimn i ном кеде (т.- их; знаковые пазрчдп чвлчюг я cocTdiHOH частью старших цифр и Yn), го в качестве коррекции исполь-и кт я дополнигепт п re кодп множичип п , а зть рс гь tara автоматически попучиехtя в г гф 1ЧРЙ иифре прои ведения t г ли ч v i чмо X и мнолп тель Y хранятся в ре гнс грч 1 и в рорме дотпненич (ii

in IKLIBMC разряды не входя ь i ipn не

и V

и не частв от

цисррн

о в шоженни), то в i if

корректирующих поправок испопы

iiei t i ред i ье

иТСЯ

допоп ения множимого и множитечл, а знак результата должен быть формпро ван отдельно спожения по модулю ДВУХ знаков сомножителей

ь о р м v л а изобре i синя

Устройство для умножения, содержа щее рргисг-ры множимого и множителя, цве группьт блоков вычислении разрядных значений произведения по п блоков

в каждой (п - разрядность сомножите- чодм первых буферных регистров второй

лей), четыре группы буферных, регистров по п регистров в каждой, регистр сдвига, регистр задержки множителя и сумматор, выход которого соединен г

и четвертой групп соединены соответ- стненно с входами первого и второго сттаг)рмпч сумматора, ччоды б1 верных регистров третьей и четчрргои групп

0

5

Q

v

31

in

SO

ьп одом результата устройства вход мноли-неля которого оедииен с входом регистра aдepлки сожителя, выход которого соединен с информационными вхо - гаги per е.тр i if o ran сая, ьход разре- HieniiH записи J-го разряда которого соединен соответственно с выходом (iH) го р пряда сдвига (1 1,...,п), i-i о рааряда которого соединен соответственно с входом разрешения апчси i го разряда множимого, информационные входы которого соединены с входом множимого устройства, входы множимого Споков вычисления разрядных значении произведения первой группы соединен. с выходами соответствующих рирчдо регистра мнокимого, входы t UTAH t. ш (i iQKOB вычисления разрядных Л iPitiiH ,еищ второй группы

т iHHi л с выходямн -оответгтвующих .oH jc HCipa г ноы еля, вход пер- ро ч т 11 т смог о 1-го Ьлока вычисления п )рч и ы -жа 1ении произведения первой Р |ы опцинен еоотеегственно с вы- -ход м i-ici буферного регистра первой j р пи, выход (т + 1)-го буферного реiH |)П ГП ЭРОЙ 1 р ППР . ,П-1)

ч ;инеЧ1 гоогпет(. в одом пто i)iii u Mi i о T-IJ bioin вышсчечия

i нь ч. «нацени произведения пе ц i- 11 л пп i, j.1 од втерло спагаемого а м) блока янпс пен IF pa i рядных значении плтпзведедия первой группы со- 1днн(н f чс рви 1 ь юг екции уст- роис i ь , Влоды i фепц Г негров ш Ui и и в орон ip-ipii оедннены со- от i г i с пчх1Д1Ми старшего и Ю11дие.о р чря ;ов ьпок пч л ччс е1гия na jjniibK in аче i in ппоиз стения п р- LO ( группы, ь) о ц ncji iOio cjTaraeMoro 1 t бпок j ВЬГЧНСЛРПНЛ разрядных зна- чс чи произведет-гя второй группы со дпиен с ос тветствечно с ь 1-го буферного регистра третьей группы, выход ()-ro гпгЛерного perncipi четвертой гругшч соединен со тветст- е ю - в содом второго ггат с1- тг j io блокг в гчисче,ния ра рчдньх зна чончй произведения iторой группы, вход второго счагаемого n-го бпока. вы ШСЛРНИЯ разрядных з шчений произведения второй группы соединен с вто рым входом коррекции устройства, чодм первых буферных регистров второй

и четвертой групп соединены соответ- стненно с входами первого и второго сттаг)рмпч сумматора, ччоды б1 верных регистров третьей и четчрргои групп

915698248

соединеныtсоответственно с выходамиройства, а вькод - с входами множимостаршего и младшего разрядов блоковго блоков вычисления разрядных эначевычисления разрядных значений произ-ний произведения второй группы, вховедения второй группы, отличаю-,ды множителя блоков вычисления разщ е -е с я тем, что, с целью повыше-рядных значений произведения первой

ния быстродействия, в него введен ре-группы соединены с выходом регистра

гистр задержки множимого, вход кото-задержки множителя, рого соединен с входом множимого уст

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1988 |

|

SU1529216A1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для умножения | 1982 |

|

SU1022156A2 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для умножения | 1989 |

|

SU1635176A1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Устройство для умножения чисел | 1988 |

|

SU1536374A1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

Изобретение относится к вычислительной технике и предназначено для быстрого выполнения операции умножения чисел в любой позиционной системе счисления в дополнительном последовательном коде. Особенно эффективно его использование при применении БИС и СБИС. Цель изобретения - повышение быстродействия. Новым в устройстве, содержащем регистр 1 множимого, регистр 2 множителя, две группы блоков 3, 4 вычисления разрядных значений произведения, четыре группы буферных регистров 5 - 8, регистр 9 сдвига, регистр 10 задержки множителя, сумматор 11, является введение регистра 12 задержки множимого, что позволяет сократить длительность такта работы устройства за счет исключения из нее времени записи в регистры множимого и множителя. 1 ил.

| Основы построения технических средств ЕС ЭВМ на интегральных микросхемах | |||

| /По)ц ред | |||

| Б | |||

| Н.Файзулаева | |||

| - .: адио и пять, 1981, с | |||

| Двухколейная подвесная дорога | 1919 |

|

SU151A1 |

| зторское свидетельство СССР ., 1022156, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ) УСТРОЙСТВО УМНОЖЕНИЯ () Изобретение относится к вычисли- ел ой техник | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Особенно эффективно его использование при применении БИС и СБИС | |||

| Цель изобретения - повышение быстродействия | |||

| Новым в устройстве, содержащем регистр 1 множимого, регистр 2 множителя, две группы блоков 3,4 вычисления разрядных значений произведения, четыре группы буферных регистров 5-8, регистр 9 сдвига, регистр 10 задержки множителя, сумматор 11, является введение регистра 12 задержки множимого, что позволяет сократить длительность такта работы устройства за счет исключения из нее времени записи в регистры множимого и множителя | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| i (Л | |||

Авторы

Даты

1990-06-07—Публикация

1988-01-06—Подача